Page 207 - Cloud computing: From paradigm to operation

P. 207

Framework and requirements for cloud computing 1

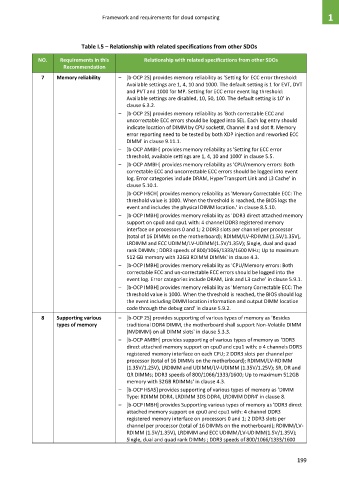

Table I.5 – Relationship with related specifications from other SDOs

NO. Requirements in this Relationship with related specifications from other SDOs

Recommendation

7 Memory reliability – [b-OCP 2S] provides memory reliability as 'Setting for ECC error threshold:

Available settings are 1, 4, 10 and 1000. The default setting is 1 for EVT, DVT

and PVT and 1000 for MP. Setting for ECC error event log threshold:

Available settings are disabled, 10, 50, 100. The default setting is 10' in

clause 6.3.2.

– [b-OCP 2S] provides memory reliability as 'Both correctable ECC and

uncorrectable ECC errors should be logged into SEL. Each log entry should

indicate location of DIMM by CPU socket#, Channel # and slot #. Memory

error reporting need to be tested by both XDP injection and reworked ECC

DIMM' in clause 9.11.1.

– [b-OCP AMBH] provides memory reliability as 'Setting for ECC error

threshold, available settings are 1, 4, 10 and 1000' in clause 5.5.

– [b-OCP AMBH] provides memory reliability as 'CPU/memory errors: Both

correctable ECC and uncorrectable ECC errors should be logged into event

log. Error categories include DRAM, HyperTransport Link and L3 Cache' in

clause 5.10.1.

[b-OCP HSCH] provides memory reliability as 'Memory Correctable ECC: The

threshold value is 1000. When the threshold is reached, the BIOS logs the

event and includes the physical DIMM location.' in clause 8.5.10.

– [b-OCP IMBH] provides memory reliability as 'DDR3 direct attached memory

support on cpu0 and cpu1 with: 4 channel DDR3 registered memory

interface on processors 0 and 1; 2 DDR3 slots per channel per processor

(total of 16 DIMMs on the motherboard); RDIMM/LV-RDIMM (1.5V/1.35V),

LRDIMM and ECC UDIMM/LV-UDIMM(1.5V/1.35V); Single, dual and quad

rank DIMMs ; DDR3 speeds of 800/1066/1333/1600 MHz; Up to maximum

512 GB memory with 32GB RDIMM DIMMs' in clause 4.3.

– [b-OCP IMBH] provides memory reliability as 'CPU/Memory errors: Both

correctable ECC and un-correctable ECC errors should be logged into the

event log. Error categories include DRAM, Link and L3 cache' in clause 5.9.1.

– [b-OCP IMBH] provides memory reliability as 'Memory Correctable ECC: The

threshold value is 1000. When the threshold is reached, the BIOS should log

the event including DIMM location information and output DIMM location

code through the debug card' in clause 5.9.2.

8 Supporting various – [b-OCP 2S] provides supporting of various types of memory as 'Besides

types of memory traditional DDR4 DIMM, the motherboard shall support Non-Volatile DIMM

(NVDIMM) on all DIMM slots' in clause 5.3.3.

– [b-OCP AMBH] provides supporting of various types of memory as 'DDR3

direct attached memory support on cpu0 and cpu1 with: o 4 channels DDR3

registered memory interface on each CPU; 2 DDR3 slots per channel per

processor (total of 16 DIMMs on the motherboard); RDIMM/LV-RDIMM

(1.35V/1.25V), LRDIMM and UDIMM/LV-UDIMM (1.35V/1.25V); SR, DR and

QR DIMMs; DDR3 speeds of 800/1066/1333/1600; Up to maximum 512GB

memory with 32GB RDIMMs' in clause 4.3.

– [b-OCP HSAS] provides supporting of various types of memory as 'DIMM

Type: RDIMM DDR4, LRDIMM 3DS DDR4, LRDIMM DDR4' in clause 8.

– [b-OCP IMBH] provides Supporting various types of memory as 'DDR3 direct

attached memory support on cpu0 and cpu1 with: 4 channel DDR3

registered memory interface on processors 0 and 1; 2 DDR3 slots per

channel per processor (total of 16 DIMMs on the motherboard); RDIMM/LV-

RDIMM (1.5V/1.35V), LRDIMM and ECC UDIMM/LV-UDIMM(1.5V/1.35V);

Single, dual and quad rank DIMMs ; DDR3 speeds of 800/1066/1333/1600

199