Page 128 - ITU Journal Future and evolving technologies – Volume 2 (2021), Issue 2

P. 128

ITU Journal on Future and Evolving Technologies, Volume 2 (2021), Issue 2

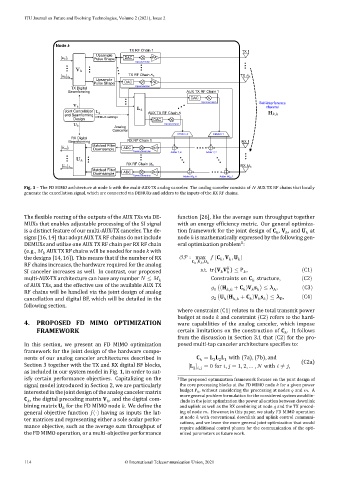

Node k

TX RF Chain 1 TX 1

Upsample

Pulse Shape DAC PA

Upconversion

TX RF Chain TX

Upsample

Pulse Shape DAC PA

TX Digital Upconversion

Beamforming AUX TX RF Chain 1

DAC

Upconversion Self-interference

channel

Joint Cancellation AUX TX RF Chain N

and Beamforming DEMUX settings

Design DAC

Upconversion

Analog

Canceller

DEMUX N DEMUX 1

RX Digital

Beamforming RX RF Chain 1 RX 1

Matched Filter

Downsample ADC LNA

Downconversion Adder 1,N Adder 1,1

RX RF Chain RX

Matched Filter

Downsample ADC LNA

Downconversion Adder ,N Adder ,1

Fig. 3 – The FD MIMO architecture at node with the multi‑AUX‑TX analog canceler. The analog canceler consists of AUX TX RF chains that locally

generate the cancellation signal, which are connected via DEMUXs and adders to the inputs of the RX RF chains.

The lexible routing of the outputs of the AUX TXs via DE‑ function [26], like the average sum throughput together

MUXs that enables adjustable processing of the SI signal with an energy ef iciency metric. Our general optimiza‑

is a distinct feature of our multi‑AUX‑TX canceler. The de‑ tion framework for the joint design of C , V , and U at

signs [16, 14] that adopt AUX TX RF chains do not include node is mathematically expressed by the following gen‑

1

DEMUXs and utilize one AUX TX RF chain per RX RF chain eral optimization problem :

(e.g., AUX TX RF chains will be needed for node with

the designs [14, 16]). This means that if the number of RX ∶ max (C , V , U )

RF chains increases, the hardware required for the analog C ,V ,U

H

SI canceler increases as well. In contrast, our proposed s.t. tr{V V } ≤ P , (C1)

multi‑AUX‑TX architecture can have any number ≤ Constraints on C structure, (C2)

of AUX TXs, and the effective use of the available AUX TX ((H + C )V s ) ≤ , (C3)

RF chains will be handled via the joint design of analog 1 , A

cancellation and digital BF, which will be detailed in the (U (H , + C )V s ) ≤ , (C4)

D

2

following section.

where constraint (C1) relates to the total transmit power

budget at node and constraint (C2) refers to the hard‑

4. PROPOSED FD MIMO OPTIMIZATION ware capabilities of the analog canceler, which impose

FRAMEWORK certain limitations on the construction of C . It follows

from the discussion in Section 3.1 that (C2) for the pro‑

In this section, we present an FD MIMO optimization posed multi‑tap canceler architecture speci ies to:

framework for the joint design of the hardware compo‑

nents of our analog canceler architectures described in C = L L L with (7a), (7b), and

3 2 1

Section 3 together with the TX and RX digital BF blocks, [L ] = 0 for , = 1, 2, … , with ≠ , (C2a)

2 ,

as included in our system model in Fig. 1, in order to sat‑

isfy certain performance objectives. Capitalizing on the 1 The proposed optimization framework focuses on the joint design of

signal model introduced in Section 2, we are particularly the core processing blocks at the FD MIMO node for a given power

interested in the joint design of the analog canceler matrix budget P , without considering the processing at nodes and . A

more general problem formulation for the considered system would in‑

C , the digital precoding matrix V , and the digital com‑ clude in the joint optimization the power allocation between downlink

bining matrix U for the FD MIMO node . We de ine the and uplink as well as the RX combining at node and the TX precod‑

general objective function (⋅) having as inputs the lat‑ ing of node . However, in this paper, we study FD MIMO operation

ter matrices and representing either a sole scalar perfor‑ at node with conventional downlink and uplink control communi‑

cations, and we leave the more general joint optimization that would

mance objective, such as the average sum throughput of require additional control phases for the communication of the opti‑

the FD MIMO operation, or a multi‑objective performance mized parameters as future work.

114 © International Telecommunication Union, 2021