ITU Telecommunication Standardization Sector Study Group 15 Experts Group for Video Coding and Systems in ATM and Other Network Environments Document AVC-701 Version 1.0 November 1994

SOURCE: Japan

TITLE: The specification of H.32X hardware for the interconnection experiment

PURPOSE: Proposal

## 1. Introduction

An interconnection experiment is planed to verify the recommendations H.262, H.222.0, H.222.1, H.32X, and H.24X. Document AVC-659 describes the scope of experiment, schedule, testing items and so on. According to the document, we propose the hardware specification.

# 2. Hardware specfications

| Items                    | Mandatory spec.                    | Optional spec.             |

|--------------------------|------------------------------------|----------------------------|

| Video codec              |                                    |                            |

| Coding scheme            | H.262                              |                            |

| Picture format (ENC)     | 525/60                             | 625/50                     |

|                          | 720(pixel) x 240(line) x 60(field) |                            |

| Profile/Level (ENC)      | SP@ML(field or frame structure)    | MP@ML                      |

| Picture format (DEC)     | 525/60                             | 625/50                     |

| Profile/Level (DEC)      | SP@ML(field and frame structure)   |                            |

| Coding rate              | CBR                                | VBR                        |

| Audio codec              |                                    |                            |

| Coding scheme            | MPEG-1 Layer-2                     |                            |

| The number of channel    | 2 channel (stereo)                 |                            |

| Coding rate              | 384 kbps (192kbps x 2channel)      | 192, 224, 256, 320 kbps    |

| Sampling rate            | 48.0 kHz                           | 44.1 kHz                   |

| Multimedia MUX           |                                    |                            |

| MUX scheme               | H.222.0 TS                         | H.222.0 PS                 |

| Information rate         | n/m of network clock               | (n,m)=(47,2430), (47,810), |

| at AAL-SAP (*1)          | (n,m)=(47,1215) [6.016Mbps]        | (94,1215) [3,9,12Mbps]     |

| CSPS                     | -                                  | On/Off                     |

| System clock/Network     | none                               | sync.                      |

| clock synchronism(*2)    |                                    |                            |

| The number of program    | single                             | multiple                   |

| AAL                      |                                    |                            |

| Type (*3)                | Type 1 or Type 5                   | Type 1 and Type 5          |

| Timing recovery          | none                               | Adaptive clock (*4)        |

| Error correction         | none                               | Long interleave /Short     |

|                          |                                    | interleave (I.363) (*4)    |

| Others                   |                                    |                            |

| Physical interface point | none                               | AAL-SAP, ATM-SAP           |

| Data channel             | none                               | multiple                   |

| C&I                      | none                               | sync. to video             |

| Communication            | none                               | H.24X                      |

| procedure, protocol      |                                    |                            |

| Interconnection to the   | none                               | H.32Y (H.320)              |

| different type terminal  |                                    |                            |

#### notes

- \*1: The values of n, m are specified to offer 6.144 Mbps after the AAL1 PDU header (1 byte) is added. These values remain for further study in case that AAL type 5 is employed and/or FEC is employed.

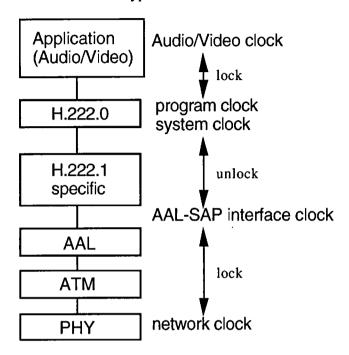

- \*2 : Clock relation is shown in Figure 1.

- \*3: The mapping from TS packet to ATM cell in AAL5 is for further study.

- \*4: These can be selected for AAL type1.

Fig.1 Clock relation in the H.32X protocol stack

# 3. Call for participation

Three Japanese organizations are scheduled to take part in this verification test as of October 1994, and more participants would be welcome. It is possible for a variety of communication equipments to participate, such as an encoder only or decoder only terminal, a video server, and a test signal generator.

### Reference

AVC-659 "A plan of H.32X hardware interconnection experiment in Japan", July 6th, 1994.

**END**