Telecommunication Standardization Sector Study Group 15 Experts Group for ATM Video Coding (Rapporteur's Group on part of Q.2/15)

SOURCE

: JAPAN

TITLE

: Correction method for cell loss and bit error in AAL Type 1

**PURPOSE**

: Proposal

#### 1. Introduction

The cell loss protection method for unidirectional video services in the ATM network is defined in Recommendation I.363. This method relies on an octet interleaving scheme and a FEC using RS(128,124) code (See Annex 1). However, this method introduces a delay of 128 cells at each end, and so this delay may be unacceptable to support H.320 terminals in B-ISDN.

During the last meeting, we presented a forward error correction method in AAL Type 1 (See Annex 2) against cell losses and bit errors with low processing delay (AVC-459). This method, in which an error correction matrix is made up of 16 FEC frames, was supported in principle and encouraged to further reduce the delay.

In this document, further consideration on the following points is described.

- To minimize the processing delay, the size of correction matrix is reduced to 12 cells.

- Service Access Point (SAP) between CS and SAR

- Protection method for successive cells loss

- Capability of the cell loss correction and random bytes error

- Hardware complexity

- Applying to other AAL type

#### 2. Proposed Method

# 2.1 General procedure

To reduce the processing delay, our method consists of Reed-Solomon(48,44) code and FEC frame shuffling. The RS(48,44) code is able to correct up to 2 random errored symbols (bytes) or 4 erasures in the FEC frame. An erasure is an errored byte whose location in the FEC frame is known. The generator polynomial of this RS code is shown in Annex 3.

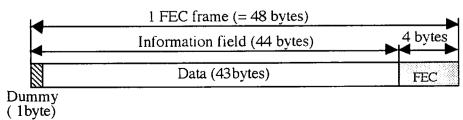

At the transmitting end, 4 bytes RS(48,44) code is appended to 44 bytes of information field. This information field consists of 43 bytes data from Convergence Sublayer and one byte dummy data '11111111'. Figure 1 shows a FEC frame for RS(48,44) code.

As another construction way, information field might be to consist of 43 bytes data from CS layer and one byte SAR-PDU header. It will be a matter for consideration in ITU-TS SG13.

Figure 1 FEC frame for RS(48,44) code.

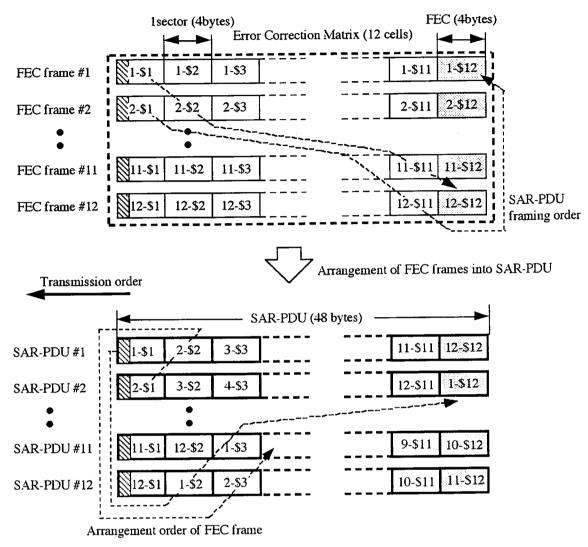

To make a shuffle, an error correction matrix is made up of 12 FEC frames, corresponding to 12 SAR-PDUs, and each FEC frame is divided into 12 sectors. The sector whose length is 4 bytes is numbered from \$1 to \$12. A SAR-PDU is organized from one sector of each FEC frame. The first sector which includes the dummy data is exchanged with one byte SAR-PDU header. The shuffling process is shown in Figure 2.

Figure 2 Shuffle of FEC frames into SAR-PDUs.

When a cell loss occurs, the receiving end can detect the lost cell according to the Sequence Number (SN) information. The loss of one SAR-PDU implies one sector (i.e. 4 bytes) loss for each FEC frame. However, the location of lost sector is known, therefore RS code is able to correct this loss as 4 erasures. This method enables the correction of only one cell among the 12 cells.

## 2.2 Consideration of SAP between CS and SAR

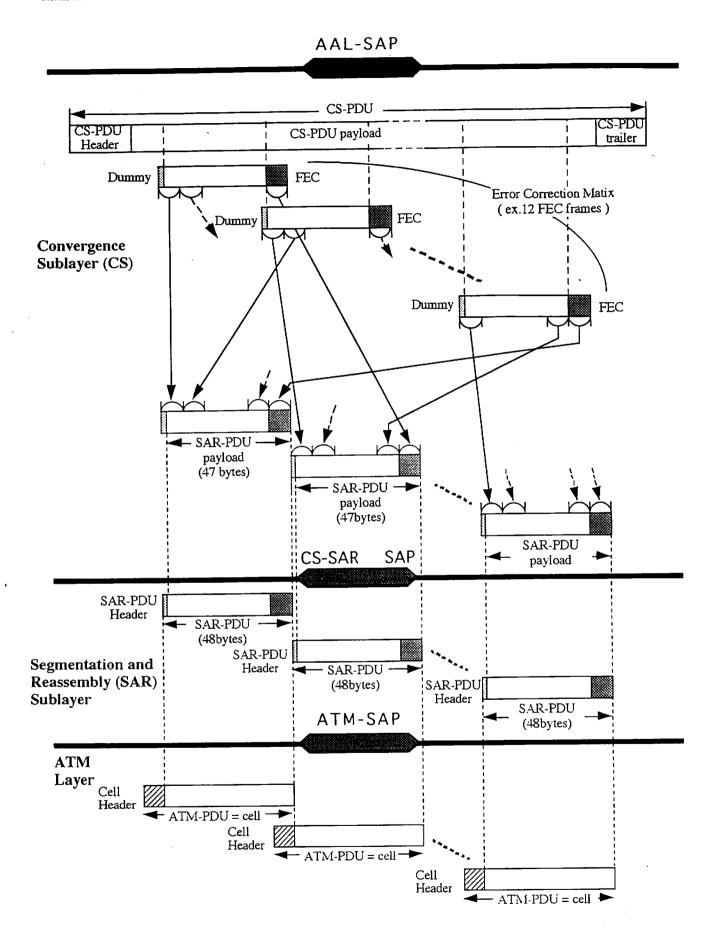

Figure 1 of Annex 4 shows the general data flow of transmitting CS with proposed method. In this case, cell loss correction works as a function of the CS, it is possible to make the SAP between CS and SAR.

#### 2.3 Protection from successive cell losses

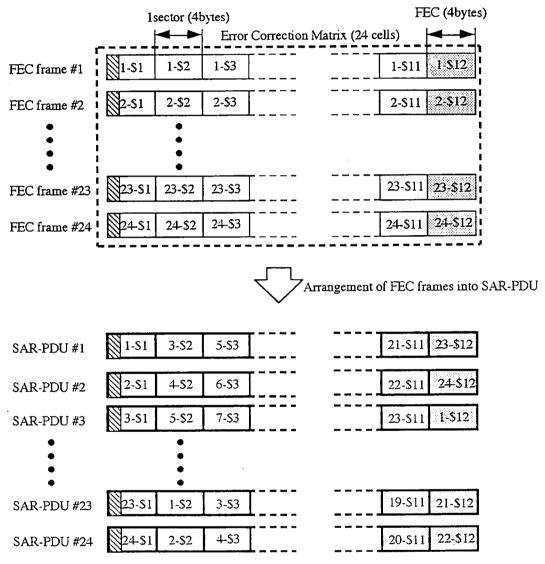

For extension of the proposed method, it is possible to correct successive cell losses by using an isolated shuffle technique. For example, to protect from successive 2 cell losses, an error correction matrix is made up of 24 FEC frames (See figure 3). FEC frames with odd number and those with even number are separately placed at different SAR-PDUs. The loss of successive 2 cells within one error correction matrix implies only one sector loss for each FEC frame. It is noted that this method introduces a delay of 24 cells at each end.

Figure 3 Isolated shuffle for protection from successive 2 cell losses.

#### 3. Performance evaluation

### 3.1 Error Correction Capability and Transmission efficiency

In comparison with I.363 method, error correction capability and transmission efficiency are listed on table 1. It is noted that both methods are correctable against either cell loss or random byte errors.

Table 1 Error Correction Capability and Efficiency

| Forward Error       | Correctable error (either-or) |                     | Efficiency |  |

|---------------------|-------------------------------|---------------------|------------|--|

| Correction Code     | cell loss(es)                 | random bytes errors | (%)        |  |

| RS(48,44)           | 1 cell / 12 cells             | 2 bytes / 48 bytes  | 91.5       |  |

| RS(128,124) [I.363] | 4 cells / 128 cells           | 2 bytes / 128 bytes | 96.9       |  |

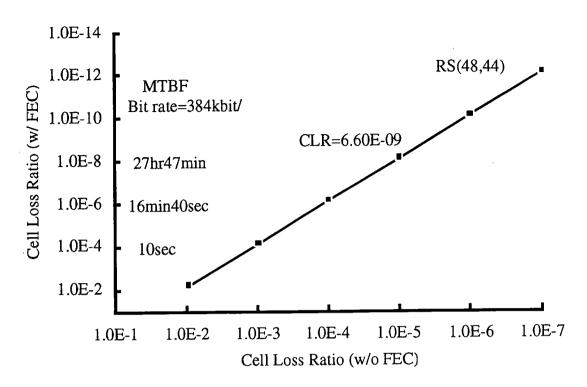

We evaluated correction capability for cell loss. Figure 1 of Annex 5 gives information on the correction performance for cell loss of this method at various cell loss ratios. The cell loss is assumed to be random, i.e. burst length is set to 1. When the CLR is 1.0E-5 (i.e. mean time between failures [MTBF] at 384kb/s is 100 sec), the CLR after correcting is improved to 6.6E-9 (i.e. MTBF at 384kb/s is 42 hours and 5 minutes). From this result, proposed method has enough correction capability against random cell loss.

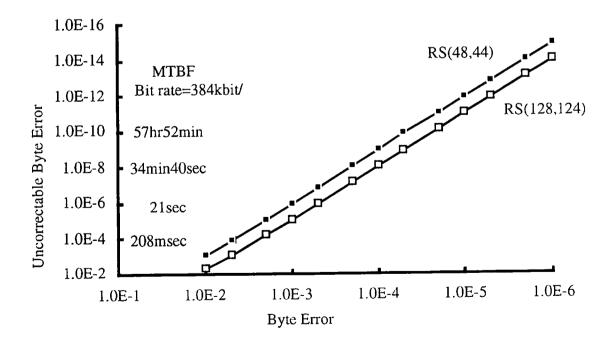

For random byte error correction, Figure 2 of Annex 5 shows the RS(48,44) code performance calculated by weight distribution method. When random byte error probability (BER) is 1.0E-4 (i.e. MTBF at 384kb/s is 208 msec), the BER after correcting is improved to 1.09E-9 (i.e. MTBF at 384kb/s is 6 hours and 18 minutes). From this result, proposed method has also enough correction capability against random byte error.

# 3.2 Processing delay

The total size of error correction matrixes is 48(bytes)\*12(cells)\*2(transmitting and receiving side), i.e. 1152 bytes, therefore the sum of processing delay will be calculated as table 2.

Table 2 Total processing delay at various bit rate

| Forward Error       | Size of Error             | Processing delay (msec) |         |         |

|---------------------|---------------------------|-------------------------|---------|---------|

| Correction Code     | Correction Matrix (cells) | 128kb/s                 | 384kb/s | 1.5Mb/s |

| RS(48,44)           | 12                        | 72                      | 24      | 6       |

| RS(128,124) [I.363] | 128                       | 768                     | 256     | 64      |

(Note) Bit rate is the SAR-PDU rate (i.e. not ATM cell rate).

As the results, the delay is reduced to about 24 msec at 384 kbit/sec, and this delay is acceptable.

At higher bit rate (around 1.5Mbit/sec), the delay becomes more relaxed than 384 kbit/sec. Thus, an error correction matrix can take a large size providing protection for successive cell losses by using isolation technique described in §2.3.

# 4. Synchronization method of Error Correction Matrix

The receiving end must know the first cell of an error correction matrix in order to reconstruct the FEC frames from receiving SAR-PDUs. To realize the synchronization of error correction matrix, the first cell flag will be transmitted. According to the case of clock recovery, there are

some transport methods.

# [Case 1] No use of CSI bit for clock recovery

The CSI bit in the SAR-PDU header is available for transport of the first cell flag. When the first cell of error correction matrix is transmitted, the CSI bit is set to 1. Otherwise, CSI bit always set to 0.

# [Case 2] Use of Synchronous Residual Time Stamp (SRTS) method

The CSI bit in successive SAR-PDU headers with the odd sequence count values of 1, 3, 5 and 7 are used for RTS transport. In this case, the CSI bit in SAR-PDU headers with the even sequence count values of 0, 2, 4 and 6 are available for transport of the first cell indicator.

# [Case 3] Use of Structured Data Transfer (SDT) without SRTS

The CSI bit in successive SAR-PDU headers with the even sequence count value of 0, 2, 4 and 6 are used to indicate the presence of the pointer field. In this case, the CSI bit in SAR-PDU headers with the odd sequence count values of 1, 3, 5 and 7 may be available for transport of the first cell indicator.

## [Case 4] Use of SDT with SRTS

In this case, CSI bit is always used for recovery of the user clock. The first cell indicator may be transport by using the payload type in ATM cell header.

Considering with B-N interworking, the SDT method may be necessary for clock recovery. On this point, we need some suggestion from ITU-TS SG 13.

### 5. H/W Implementation Issue

Logic size of RS encoder and decoder mainly depends on the minimum distance of RS code. RS(48,44) code has the same minimum distance with RS(128,124) code, therefore number of logic gate is almost same. From a viewpoint of buffer size for matrix, RS(48,44) code only needs 1/10 of RS(128,124) code.

### 6. Applying to other AAL type

In I.363, AAL type 2 is not defined yet, however this correction method may apply to low speed VBR services.

## 7. Conclusion

A forward error correction method in AAL Type 1 is proposed. The proposed method can correct either cell loss or random bytes errors within cells with acceptable delay for low speed services. When the network quality in B-N interworking is not sufficiently high, it will be necessary to provide such a forward error correction method as proposed in this document. We request ITU-TS SG 13 to investigate this error resilience method.

END.

#### Annex 1 to AVC-521

Figure of the format of interleave matrix from Recommendation I.363.

|                                         |    | Writing order |            |          |                   |

|-----------------------------------------|----|---------------|------------|----------|-------------------|

| Reading                                 |    | Order         | 124 octets | 4 octets | _                 |

| Reading order                           | 1  | t             | Data       | FEC      | RS(128, 124) code |

|                                         | 2  |               |            |          |                   |

|                                         |    |               |            |          |                   |

| $\blacktriangledown \blacktriangledown$ | 47 |               |            |          |                   |

Within this matrix, I.363 method can perform the following corrections:

- 4 cell losses; or

- 2 cell losses and 1 errored octet in each row; or

- 2 errored octets in each row if there is no cell loss

#### Annex 2 to AVC-521

AAL Type 1 Format (Ref. CCITT SGXVIII-R103-E 'INTEGRATED VIDEO SERVICES (IVS) BASELINE DOCUMENT' July 1992)

|                            | SN field<br>(4bits) |                    | SNP field<br>(4bits) |                 | AAL user information field (47 octets) |

|----------------------------|---------------------|--------------------|----------------------|-----------------|----------------------------------------|

| Cell header<br>(ATM layer) | CSI<br>(1)          | SN<br>count<br>(3) | CRC<br>(3)           | Even parity (1) | P field (8bits)<br>(if necessary)      |

#### Annex 3 to AVC-521

The generator polynomial of the Reed Solomon(48,44) code is given by

$$G(x) = \prod_{i=0}^{3} (X + \alpha^{i})$$

where  $\alpha$  is a root of the binary primitive polynomial

$$g(x) = x^8 + x^4 + x^3 + x^2 + 1$$

The minimum distance of RS(48,44) code is 5. This generator polynomial is widely used as the forward error correction method in AV applications such as Compact Dics and digital VCR.

Figure 1 / Annex 4 General data flow of transmitting CS with the AAL type 1.

Figure 1 / Annex 5 Correction performance for cell loss. (1 cell loss correction per 12 cells)

Figure 2 / Annex 5 Correction performance for random byte error.

8

AVC-521