UIT-T

SECTOR DE NORMALIZACIÓN

DE LAS TELECOMUNICACIONES

DE LA UIT

**G.991.1** (10/98)

SERIE G: SISTEMAS Y MEDIOS DE TRANSMISIÓN, SISTEMAS Y REDES DIGITALES

Sistemas de transmisión digital – Secciones digitales y sistemas digitales de línea – Redes de acceso

Transceptores de línea digital de abonado de alta velocidad binaria

Recomendación UIT-T G.991.1

(Anteriormente Recomendación del CCITT)

## RECOMENDACIONES UIT-T DE LA SERIE G

## SISTEMAS Y MEDIOS DE TRANSMISIÓN, SISTEMAS Y REDES DIGITALES

| CONEXIONES Y CIRCUITOS TELEFÓNICOS INTERNACIONALES                                                                                                        | G.100-G.199 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| SISTEMAS INTERNACIONALES ANALÓGICOS DE PORTADORAS                                                                                                         |             |

| CARACTERÍSTICAS GENERALES COMUNES A TODOS LOS SISTEMAS ANALÓGICOS DE PORTADORAS                                                                           | G.200-G.299 |

| CARACTERÍSTICAS INDIVIDUALES DE LOS SISTEMAS TELEFÓNICOS INTERNACIONALES DE PORTADORAS EN LÍNEAS METÁLICAS                                                | G.300-G.399 |

| CARACTERÍSTICAS GENERALES DE LOS SISTEMAS TELEFÓNICOS INTERNACIONALES EN RADIOENLAÇES O POR SATÉLITE E INTERCONEXIÓN CON LOS SISTEMAS EN LÍNEAS METÁLICAS | G.400–G.449 |

| COORDINACIÓN DE LA RADIOTELEFONÍA Y LA TELEFONÍA EN LÍNEA                                                                                                 | G.450-G.499 |

| EQUIPOS DE PRUEBAS                                                                                                                                        |             |

| CARACTERÍSTICAS DE LOS MEDIOS DE TRANSMISIÓN                                                                                                              | G.600-G.699 |

| SISTEMAS DE TRANSMISIÓN DIGITAL                                                                                                                           |             |

| EQUIPOS TERMINALES                                                                                                                                        | G.700-G.799 |

| REDES DIGITALES                                                                                                                                           | G.800-G.899 |

| SECCIONES DIGITALES Y SISTEMAS DIGITALES DE LÍNEA                                                                                                         | G.900-G.999 |

| Generalidades                                                                                                                                             | G.900-G.909 |

| Parámetros para sistemas en cables de fibra óptica                                                                                                        | G.910-G.919 |

| Secciones digitales a velocidades binarias jerárquicas basadas en una velocidad de 2048 kbit/s                                                            | G.920-G.929 |

| Sistemas digitales de transmisión en línea por cable a velocidades binarias no jerárquicas                                                                | G.930-G.939 |

| Sistemas de línea digital proporcionados por soportes de transmisión MDF                                                                                  | G.940-G.949 |

| Sistemas de línea digital                                                                                                                                 | G.950-G.959 |

| Sección digital y sistemas de transmisión digital para el acceso del cliente a la RDSI                                                                    | G.960-G.969 |

| Sistemas en cables submarinos de fibra óptica                                                                                                             | G.970-G.979 |

| Sistemas de línea óptica para redes de acceso y redes locales                                                                                             | G.980-G.989 |

| Redes de acceso                                                                                                                                           | G.990-G.999 |

|                                                                                                                                                           |             |

Para más información, véase la Lista de Recomendaciones del UIT-T.

## RECOMENDACIÓN UIT-T G.991.1

# TRANSCEPTORES DE LÍNEA DIGITAL DE ABONADO DE ALTA VELOCIDAD BINARIA

#### Resumen

Esta Recomendación especifica una línea digital de abonado de alta velocidad binaria (HDSL), que es un sistema de transmisión bidireccional y simétrico que permite transportar las señales por los pares trenzados de cobre de una red de acceso a las velocidades binarias de 1544 kbit/s o 2048 kbit/s. El trabajo básico se llevó a cabo en el comité T1 del ANSI para señales a 1544 kbit/s. Los resultados de ese trabajo fueron aprovechados por el TM6 del ETSI y se adoptaron para señales a 2048 kbit/s en una especificación técnica que sirvió de base de la presente Recomendación.

El sistema HDSL utiliza la técnica de compensación de eco para separar los sentidos de la transmisión de modo que un solo par trenzado pueda transportar las señales en ambos sentidos. Se recomiendan dos alternativas diferentes para el código de línea, la modulación de amplitud de impulsos 2B1Q y la modulación de amplitud/fase sin portadora (CAP). El código CAP sólo es aplicable para 2048 kbit/s, mientras que para 2B1Q se han definido dos tramas diferentes, una para 1544 kbit/s y otra para 2048 kbit/s.

El código 2B1Q para 2048 kbit/s permite tanto la transmisión dúplex por un único par como la transmisión en paralelo por dos o tres pares. Así es posible distribuir la señal por varios pares, reducir la velocidad de símbolos y aumentar la longitud de la línea. El CAP se define para uno o dos pares solamente y el 2B1Q a 1544 kbit/s exclusivamente para dos pares.

## **Orígenes**

La Recomendación UIT-T G.991.1 ha sido preparada por la Comisión de Estudio 15 (1997-2000) del UIT-T y fue aprobada por el procedimiento de la Resolución N.º 1 de la CMNT el 13 de octubre de 1998.

#### **PREFACIO**

La UIT (Unión Internacional de Telecomunicaciones) es el organismo especializado de las Naciones Unidas en el campo de las telecomunicaciones. El UIT-T (Sector de Normalización de las Telecomunicaciones de la UIT) es un órgano permanente de la UIT. Este órgano estudia los aspectos técnicos, de explotación y tarifarios y publica Recomendaciones sobre los mismos, con miras a la normalización de las telecomunicaciones en el plano mundial.

La Conferencia Mundial de Normalización de las Telecomunicaciones (CMNT), que se celebra cada cuatro años, establece los temas que han de estudiar las Comisiones de Estudio del UIT-T, que a su vez producen Recomendaciones sobre dichos temas.

La aprobación de Recomendaciones por los Miembros del UIT-T es el objeto del procedimiento establecido en la Resolución N.º 1 de la CMNT.

En ciertos sectores de la tecnología de la información que corresponden a la esfera de competencia del UIT-T, se preparan las normas necesarias en colaboración con la ISO y la CEI.

#### **NOTA**

En esta Recomendación, la expresión *empresa de explotación reconocida (EER)* designa a toda persona, compañía, empresa u organización gubernamental que explote un servicio de correspondencia pública. Los términos *Administración*, *EER* y *correspondencia pública* están definidos en la *Constitución de la UIT (Ginebra, 1992)*.

#### PROPIEDAD INTELECTUAL

La UIT señala a la atención la posibilidad de que la utilización o aplicación de la presente Recomendación suponga el empleo de un derecho de propiedad intelectual reivindicado. La UIT no adopta ninguna posición en cuanto a la demostración, validez o aplicabilidad de los derechos de propiedad intelectual reivindicados, ya sea por los miembros de la UIT o por terceros ajenos al proceso de elaboración de Recomendaciones.

En la fecha de aprobación de la presente Recomendación, la UIT ha recibido notificación de propiedad intelectual, protegida por patente, que puede ser necesaria para aplicar esta Recomendación. Sin embargo, debe señalarse a los usuarios que puede que esta información no se encuentre totalmente actualizada al respecto, por lo que se les insta encarecidamente a consultar la base de datos sobre patentes de la TSB.

#### © UIT 1999

Es propiedad. Ninguna parte de esta publicación puede reproducirse o utilizarse, de ninguna forma o por ningún medio, sea éste electrónico o mecánico, de fotocopia o de microfilm, sin previa autorización escrita por parte de la UIT.

# ÍNDICE

| 1   | Alcanc  | e                                                                             |

|-----|---------|-------------------------------------------------------------------------------|

| 2   | Refere  | ncias                                                                         |

| 3   | Abrevi  | aturas                                                                        |

| 4   | Config  | uración de referencia y descripción funcional                                 |

| 5   | Especit | ficación del núcleo HDSL                                                      |

| 5.1 | Funcio  | nes                                                                           |

|     | 5.1.1   | Transporte transparente de tramas núcleo                                      |

|     | 5.1.2   | Relleno y supresión de relleno                                                |

|     | 5.1.3   | Procedimientos CRC-6 y detección de errores de transmisión                    |

|     | 5.1.4   | Informe de errores                                                            |

|     | 5.1.5   | Detección de fallos                                                           |

|     | 5.1.6   | Informe de fallos                                                             |

|     | 5.1.7   | Temporización de bits                                                         |

|     | 5.1.8   | Alineación de trama                                                           |

|     | 5.1.9   | Control de arranque autónomo del transceptor HDSL                             |

|     | 5.1.10  | Control y coordinación de bucles                                              |

|     | 5.1.11  | Correspondencia entre tramas núcleo y tramas HDSL                             |

|     | 5.1.12  | Control del canal de mantenimiento                                            |

|     | 5.1.13  | Sincronización y coordinación de transceptores HDSL                           |

|     | 5.1.14  | Identificación de pares                                                       |

|     | 5.1.15  | Corrección de identificación de pares                                         |

|     | 5.1.16  | Telealimentación                                                              |

|     | 5.1.17  | Corriente de humectación                                                      |

| 5.2 | Medio   | de transmisiónde                                                              |

|     | 5.2.1   | Descripción                                                                   |

|     | 5.2.2   | Requisitos mínimos de la línea local digital (DLL) para las aplicaciones HDSL |

|     | 5.2.3   | Características físicas de la DLL                                             |

|     | 5.2.4   | Características eléctricas de la DLL                                          |

| 5.3 | Método  | o de transmisión                                                              |

|     | 5.3.1   | Generalidades                                                                 |

|     | 5.3.2   | Transmisión por tres pares                                                    |

|     | 5.3.3   | Transmisión por dos pares                                                     |

|     | 5.3.4   | Transmisión por un par                                                        |

|     | 5.3.5   | Transmisión por cuatro pares                                                  |

|     | 5.3.6  | Código de línea                                           |

|-----|--------|-----------------------------------------------------------|

|     | 5.3.7  | Velocidad de símbolo por la línea                         |

| 5.4 | Estruc | tura de trama                                             |

|     | 5.4.1  | Trama núcleo                                              |

|     | 5.4.2  | Trama HDSL 2B1Q                                           |

|     | 5.4.3  | Método de aleatorización                                  |

| 5.5 | Canal  | de operaciones insertadas HDSL (eoc)                      |

|     | 5.5.1  | Funciones de eoc HDSL                                     |

|     | 5.5.2  | Protocolo de acuse de recibo eoc HDSL                     |

|     | 5.5.3  | Modo lectura/escritura de datos eoc HDSL                  |

|     | 5.5.4  | Lista de mensajes eoc HDSL                                |

|     | 5.5.5  | Requisitos del conjunto de mensajes eoc HDSL              |

|     | 5.5.6  | Registro de datos en la NTU y en regeneradores            |

|     | 5.5.7  | Margen de ruido                                           |

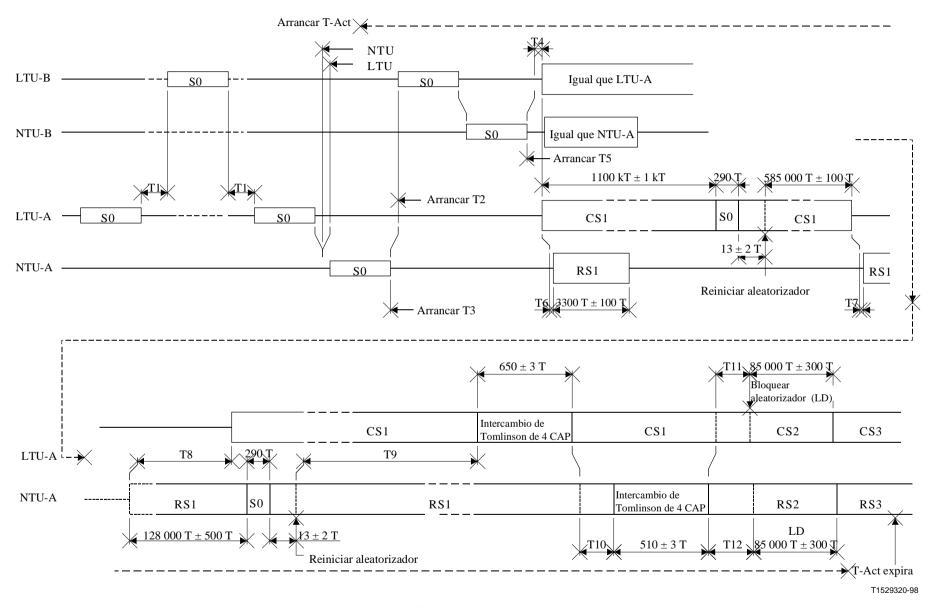

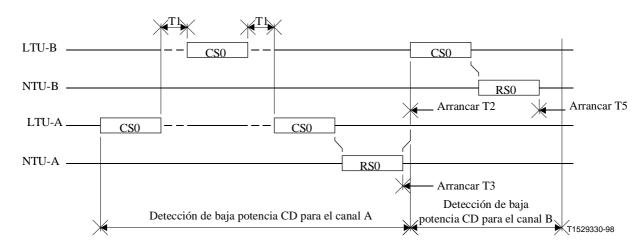

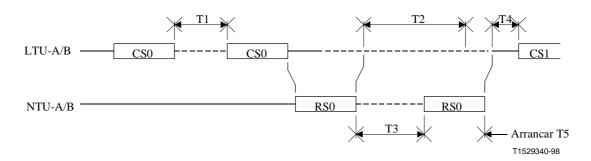

| 5.6 | Proced | dimiento de arranque                                      |

|     | 5.6.1  | Generalidades                                             |

|     | 5.6.2  | Señales de control y estado                               |

|     | 5.6.3  | Señales transmitidas                                      |

|     | 5.6.4  | Temporizadores                                            |

|     | 5.6.5  | Diagramas de estados de activación                        |

|     | 5.6.6  | Procedimientos relacionados con el regenerador            |

| 5.7 | Opera  | ción y mantenimiento                                      |

|     | 5.7.1  | Funciones en el punto de referencia OAM externo a la LTU  |

|     | 5.7.2  | Funciones en el punto de referencia OAM externo a la NTU  |

|     | 5.7.3  | Mensajes OAM y funciones admitidas por el núcleo HDSL     |

|     | 5.7.4  | Funciones OAM relacionadas con la alimentación en energía |

|     | 5.7.5  | Comportamiento del regenerador                            |

| 5.8 | Caract | terísticas eléctricas de un transceptor 2B1Q              |

|     | 5.8.1  | Generalidades                                             |

|     | 5.8.2  | Impedancia y pérdida de retorno del transmisor/receptor   |

|     | 5.8.3  | Reloj de referencia del transceptor                       |

|     | 5.8.4  | Características de salida del transmisor                  |

|     | 5.8.5  | Asimetría con respecto a tierra                           |

| 5.9 | Calida | d de funcionamiento de los transceptores HDSL             |

|     | 5.9.1  | Requisitos de calidad de funcionamiento                   |

|     | 5.9.2  | Modelos físicos de DLL (bucles de prueba)                 |

|     | 5.9.3  | Fluctuación de fase y fluctuación lenta de fase           |

| 6     | Especi | ficación del circuito común                                                                                        |

|-------|--------|--------------------------------------------------------------------------------------------------------------------|

| 6.1   | Memo   | ria intermedia de diferencia de retardo                                                                            |

| 6.2   | Mecan  | ismo de identificación de pares                                                                                    |

|       | 6.2.1  | Valores iniciales de identificación de pares                                                                       |

|       | 6.2.2  | Identificación de pares en la NTU                                                                                  |

|       | 6.2.3  | Identificación de pares en la LTU                                                                                  |

| 6.3   | Medic  | iones de la calidad de funcionamiento en laboratorio                                                               |

|       | 6.3.1  | Generalidades                                                                                                      |

|       | 6.3.2  | Configuración de prueba                                                                                            |

|       | 6.3.3  | Procedimiento de prueba con ruido conformado                                                                       |

|       | 6.3.4  | Procedimiento de prueba para el ruido impulsivo                                                                    |

|       | 6.3.5  | Prueba de rechazo en modo común                                                                                    |

|       | 6.3.6  | Prueba con microinterrupciones                                                                                     |

| 7     | Alime  | ntación en energía                                                                                                 |

| 7.1   | Genera | alidades                                                                                                           |

| 7.2   | Corrie | nte de humectación                                                                                                 |

| 7.3   | Aspect | tos relativos a la telealimentación en energía                                                                     |

|       | 7.3.1  | Aspectos relativos a la telealimentación en energía en la LTU                                                      |

|       | 7.3.2  | Aspectos relativos a la telealimentación en energía en la NTU                                                      |

|       | 7.3.3  | Aspectos relativos a la telealimentación en energía en el regenerador                                              |

| 8     | Requis | sitos ambientales                                                                                                  |

| 8.1   | Condi  | ciones climáticas                                                                                                  |

| 8.2   | Seguri | dad                                                                                                                |

| 8.3   | Protec | ción contra sobretensiones                                                                                         |

| 8.4   | Compa  | atibilidad electromagnética (EMC)                                                                                  |

| Anexo |        | tema de transmisión para aplicaciones basadas en un sistema de dos pares a bit/s                                   |

| A.1   | Estruc | tura de trama del sistema de dos pares para 784 kbit/s                                                             |

| Anexo |        | tema basado en la modulación de amplitud/fase sin portadora de línea de lo digital a alta velocidad binaria (HDSL) |

| B.1   | Alcano | e e información general                                                                                            |

|       | B.1.1  | Alcance                                                                                                            |

| B.2   | Refere | ncias                                                                                                              |

| B.3   | Abrevi | aturas                                                                                                             |

| B.4   | Config | guración de referencia y descripción funcional                                                                     |

| B.5   | Especi     | ficación del núcleo HDSL                                                                                                                |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|       | B.5.1      | Funciones                                                                                                                               |

|       | B.5.2      | Medio de transmisión                                                                                                                    |

|       | B.5.3      | Método de transmisión                                                                                                                   |

|       | B.5.4      | Estructura de trama                                                                                                                     |

|       | B.5.5      | Canal de operaciones insertadas HDSL (eoc)                                                                                              |

|       | B.5.6      | Procedimiento de arranque                                                                                                               |

|       | B.5.7      | Operación y mantenimiento                                                                                                               |

|       | B.5.8      | Características eléctricas de transceptores basados en CAP                                                                              |

|       | B.5.9      | Calidad de funcionamiento de los transceptores HDSL                                                                                     |

| B.6   | Especi     | ficación del circuito común                                                                                                             |

|       | B.6.1      | Memoria intermedia de diferencia de retardo                                                                                             |

|       | B.6.2      | Pruebas de medición de la calidad de funcionamiento en laboratorio                                                                      |

| B.7   | Alime      | ntación en energía                                                                                                                      |

| B.8   | Requis     | sitos ambientales                                                                                                                       |

| Apénd | dice I – E | jemplos específicos de las aplicaciones                                                                                                 |

| I.1   | Requis     | sitos específicos de las aplicaciones AVP RDSI con 2048 kbit/s                                                                          |

|       | I.1.1      | Correspondencia de 2048 bits con HDSL                                                                                                   |

|       | I.1.2      | Correspondencia de las funciones de mantenimiento HDSL con la interfaz                                                                  |

|       | I.1.3      | Calidad de funcionamiento                                                                                                               |

| I.2   |            | sitos específicos de la aplicación para líneas europeas arrendadas que inten información digital no estructurada a 2048 kbit/s (D2048U) |

|       | I.2.1      | Interfaces de aplicación                                                                                                                |

|       | I.2.2      | Correspondencia de la señal D2048U con HDSL                                                                                             |

|       | I.2.3      | Correspondencia de funciones de mantenimiento HDSL con la interfaz                                                                      |

|       | I.2.4      | Calidad de funcionamiento                                                                                                               |

| I.3   |            | sitos específicos de la aplicación para líneas europeas arrendadas que inten información digital no estructurada a 2048 kbit/s (D2048S) |

|       | I.3.1      | Interfaces de aplicación                                                                                                                |

|       | I.3.2      | Correspondencia de la señal D2048S con HDSL                                                                                             |

|       | I.3.3      | Correspondencia de funciones de mantenimiento con la HDSL con la interfaz                                                               |

|       | I.3.4      | Calidad de funcionamiento                                                                                                               |

| I.4   | Requis     | sitos específicos de las aplicaciones para instalación fraccional                                                                       |

|       | I.4.1      | Correspondencia de servicios fraccionales con HDSL                                                                                      |

|       | I.4.2      | Correspondencia de las funciones de mantenimiento HDSL con la interfaz                                                                  |

|       | I.4.3      | Calidad de funcionamiento                                                                                                               |

| I.5  | Requi      | sitos específicos de la aplicación para funcionamiento parcial                                      |

|------|------------|-----------------------------------------------------------------------------------------------------|

|      | I.5.1      | Correspondencia de la trama de aplicación para aplicación con funcionamiento parcial                |

|      | I.5.2      | Correspondencia de las funciones de mantenimiento HDSL con la interfaz                              |

|      | I.5.3      | Calidad de funcionamiento                                                                           |

|      | I.5.4      | Telealimentación                                                                                    |

|      | I.5.5      | Criterios de fallo parcial                                                                          |

|      | I.5.6      | Acción subsiguiente al fallo parcial                                                                |

|      | I.5.7      | Prioridad/reasignación de intervalos de tiempo                                                      |

| I.6  |            | sitos específicos de las aplicaciones para señales a 2048 kbit/s que ponden con la estructura TU-12 |

|      | I.6.1      | Configuración de referencia                                                                         |

|      | I.6.2      | Interfaces de aplicación                                                                            |

|      | I.6.3      | Correspondencia entre la trama de aplicación y el HDSL utilizando la estructura TU-12               |

|      | I.6.4      | Correspondencia de funciones de mantenimiento HDSL con la interfaz                                  |

|      | I.6.5      | Calidad de funcionamiento                                                                           |

| Apén | dice II –  | Definición detallada de las características de los cables y bucles de prueba                        |

| II.1 | Carac      | terísticas típicas de los cables                                                                    |

| II.2 | Carac      | terísticas teóricas de los bucles de prueba para Y = 31 dB en 150 kHz                               |

| Anén | dice III – | - Bibliografía                                                                                      |

#### Recomendación G.991.1

# TRANSCEPTORES DE LÍNEA DIGITAL DE ABONADO DE ALTA VELOCIDAD BINARIA

(Ginebra, 1998)

#### 1 Alcance

La presente Recomendación describe una técnica de transmisión denominada línea digital de abonado de alta velocidad binaria (HDSL, *high bit rate digital subscriber line*), como un medio para transportar varios tipos de aplicaciones. La Recomendación define los requisitos del sistema de transmisión HDSL, la calidad de funcionamiento y los requisitos y procedimientos de mantenimiento HDSL.

Un sistema de transceptor HDSL es un transceptor bidireccional de dos hilos para hilos metálicos que utiliza el método de compensación de eco. Se pueden emplear tres sistemas, uno que transporta una velocidad binaria de 784 kbit/s por cada uno de los dos o tres pares utilizados en paralelo, un segundo sistema con una velocidad binaria mayor de 1168 kbit/s y sólo dos pares en paralelo y un tercero con una velocidad binaria aún mayor de 2320 kbit/s por un par solamente.

El código de línea de sistema especificado en la presente Recomendación es 2B1Q y la modulación de amplitud/fase sin portadora (CAP). El implementador puede elegir una u otra de estas alternativas, sólo hay que emplear un código de línea en un sistema de transmisión.

En el cuerpo principal de la presente Recomendación se describen aplicaciones del sistema con 2B1Q para 2048 kbit/s. En el anexo A se describe la recomendación de la Comisión T1 para la estructura de trama de aplicaciones a 1544 kbit/s por dos pares. Los sistemas que utilizan un código de línea CAP se describen en el anexo B.

La presente Recomendación define el circuito común para combinar y controlar uno, dos o tres sistemas de transceptor HDSL, dependiendo de la velocidad binaria del sistema transceptor utilizado. El circuito común y el número necesario de sistemas de transceptor HDSL forman el núcleo HDSL, que es independiente de las aplicaciones posibles.

La presente Recomendación no especifica todos los requisitos para la implementación de la unidad de terminación de red, de la unidad de terminación de línea o del regenerador. Sólo describe la funcionalidad necesaria.

En el apéndice I se dan ejemplos de aplicaciones HDSL.

#### 2 Referencias

Las siguientes Recomendaciones del UIT-T y otras referencias contienen disposiciones que, mediante su referencia en este texto, constituyen disposiciones de la presente Recomendación. Al efectuar esta publicación, estaban en vigor las ediciones indicadas. Todas las Recomendaciones y otras referencias son objeto de revisiones por lo que se preconiza que los usuarios de esta Recomendación investiguen la posibilidad de aplicar las ediciones más recientes de las Recomendaciones y otras referencias citadas a continuación. Se publica periódicamente una lista de las Recomendaciones UIT-T actualmente vigentes.

[1] Recomendación UIT-T G.962 (1993), Sección digital de acceso a la velocidad primaria de 2048 kbit/s a la red digital de servicios integrados.

- [2] Recomendación UIT-T G.960 (1993), Sección digital para el acceso a velocidad básica a la red digital de servicios integrados.

- [3] Recomendación UIT-T I.431 (1993), Especificación de la capa 1 de la interfaz usuario-red a velocidad primaria.

- [4] Fascículo I.3 del CCITT (1988), *Términos y definiciones*.

- [5] CEI 60721-3 (1984), Classification of environmental conditions. Part 3: Classification of groups of environmental parameters and their severities. Introduction.

- [6] CEI 60950 (1991), Safety of information technology equipment.

- [7] Recomendación CCITT K.17 (1988), Pruebas de los repetidores telealimentados equipados de dispositivos de estado sólido para verificar la eficacia de las medidas de protección contra las perturbaciones exteriores.

- [8] Recomendación UIT-T K.20 (1996), Inmunidad del equipo de conmutación de telecomunicaciones contra las sobretensiones y sobrecorrientes.

- [9] Recomendación UIT-T K.21 (1996), Inmunidad de los terminales de abonado a las sobretensiones y sobrecorrientes.

- [10] Publicación 22 del CISPR (1997), Information technology Radio disturbance characteristics Limits and methods of measurement.

#### 3 Abreviaturas

En esta Recomendación se utilizan las siguientes siglas.

2B1Q Código de línea 2 binario 1 cuaternario (two binary one quaternary line code)

AB de RDSI Acceso básico a la red digital de servicios integrados

AIS Señal de indicación de alarma (alarm indication signal)

AVP de RDSI Acceso de velocidad primaria a la red digital de servicios integrados

BER Tasa de errores en los bits (bit error ratio)

BERTS Conjunto de prueba de la tasa de errores en los bits (*bit error ratio test set*)

BT Derivación de puente, rama múltiple; una sección de pares torcidos no terminada

puenteada a través de la línea (bridged tap)

c.c. Corriente continua

CAP Modulación de amplitud/fase sin portadora (carrierless amplitude/phase

*modulation*)

CRC Verificación por redundancia cíclica (cyclic redundancy check)

DLL Línea local digital (digital local line)

EMC Compatibilidad electromagnética (electromagnetic compatibility)

eoc Canal de operaciones insertadas (embedded operations channel)

ETS Norma Europea de Telecomunicación (European Telecommunication Standard)

ETSI Instituto Europeo de Normas de las Telecomunicaciones (European

*Telecommunication Standards Institute*)

HDSL Línea digital de abonado de alta velocidad binaria (high bit rate digital subscriber

line)

HOH Tara HDSL (HDSL overhead)

IUT Elemento sometido a prueba (*item under test*)

LCL Atenuación de conversión longitudinal (longitudinal conversion loss)

LFA Pérdida de alineación de trama (loss of frame alignment)

LOS Pérdida de señal (loss of signal)

LSB Bit menos significativo (least significant bit)

LTU Unidad de terminación de línea (line termination unit)

MSB Bit más significativo (most significant bit)

MTIE Error de intervalo de tiempo máximo (maximum time interval error)

NEXT Paradiafonía (near end crosstalk)

NNI Interfaz de nodo de red (network node interface)

NTU Unidad de terminación de red (network termination unit)

OAM Operación y mantenimiento (operation and maintenance)

PRBS Secuencia de bits pseudoaleatoria (pseudo-random bit sequence)

PSD Densidad espectral de potencial (power spectral density)

PSL Pérdida evaluada por suma de potencias (power sum loss)

REG Regenerador

REG-C Lado NTU del regenerador REG-R Lado LTU del regenerador

RGT Red de gestión de las telecomunicaciones rms Valor cuadrático medio (*root mean square*)

SDH Jerarquía digital síncrona (synchronous digital hierarchy)

TS Intervalo de tiempo (time slot)

TU-12 Unidad afluente 12 (*tributary unit-12*)

UI Intervalo unitario (*unit interval*)

UIT-T Unión Internacional de Telecomunicaciones – Sector de Normalización de las

Telecomunicaciones

UNI Interfaz de red de usuario (*user network interface*)

UTC Incapacidad de realizar (*unable to comply*)

VC-12 Contenedor virtual 12 (*virtual container-12*)

## 4 Configuración de referencia y descripción funcional

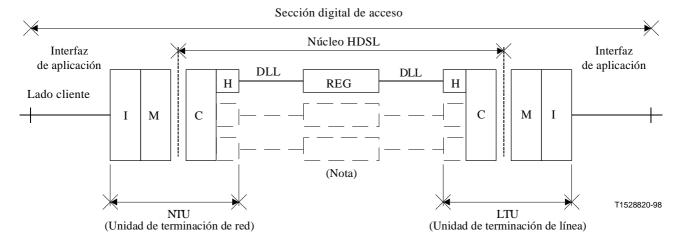

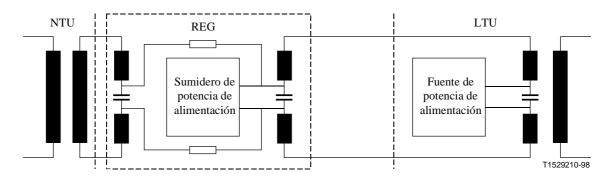

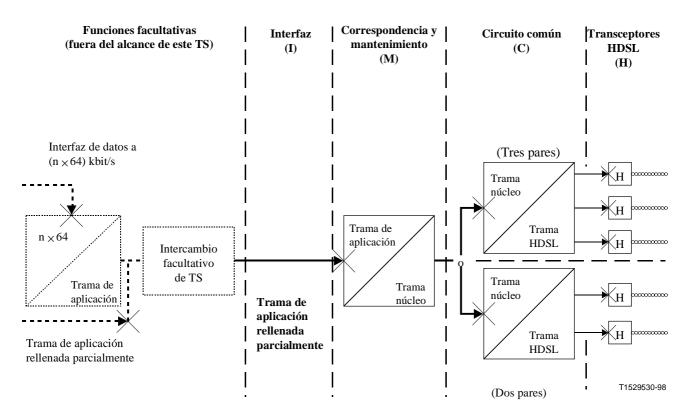

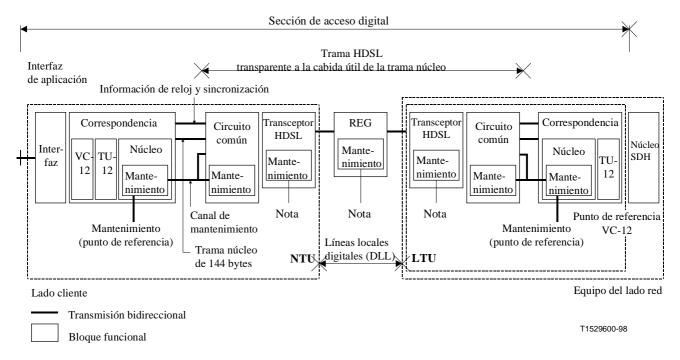

Una sección digital de acceso que utiliza la tecnología HDSL puede ser considerada como varios bloques funcionales, véase la figura 1. De acuerdo con la velocidad de transmisión (H) del transceptor HDSL, un núcleo HDSL totalmente equipado está formado por un par de transceptores HDSL a 2320 kbit/s, dos pares a 1168 kbit/s o dos o tres pares a 784 kbit/s conectados por líneas locales digitales (DLL, *digital local line*) [que están enlazadas por algún circuito común (C)]. El núcleo HDSL es independiente de la aplicación. El sistema puede funcionar también con un núcleo HDSL no equipado totalmente.

Si se requiere una gama de transmisión mayor, el núcleo HDSL puede contener regeneradores (REG) facultativos. La pérdida de inserción global del núcleo HDSL con regenerador será inferior a 1,8 veces el valor Y del núcleo HDSL sin regenerador. El regenerador se puede insertar en cualquier punto intermedio conveniente en el núcleo HDSL con la limitación de que la pérdida de inserción de la DLL de cada parte será inferior a 0,9 veces Y. Además, puede haber otras restricciones de la longitud de línea debido a la alimentación.

Una aplicación es definida por la interfaz (I) y las funcionalidades de correspondencia y mantenimiento (M).

Las funcionalidades en el lado de la central constituyen la unidad de terminación de línea (LTU, *line termination unit*) y actúan como directoras con respecto a las funcionalidades del lado del cliente (subordinadas), que forman colectivamente la unidad de terminación de red (NTU, *network termination unit*) y los REG, cuando son aplicables.

Descripción de bloques funcionales:

C Circuitos comunes

H Transceptor HDSL

I Interfaz

M Correspondencia

REG Regenerador

DLL Línea local digital

NOTA – Un núcleo HDSL totalmente equipado está formado por una combinación de uno, dos o tres H, REG y DLL, dependiendo de la velocidad de transmisión de datos del transceptor HDSL. Los REG son facultativos.

Figura 1/G.991.1 – Sección digital de acceso que emplea la tecnología HDSL (configuración simplificada)

Cabe señalar que en toda la presente Recomendación, se emplean los términos REG-C, REG-R y sistemas de transmisión HDSL. REG-R identifica las funcionalidades situadas en el lado LTU del regenerador, REG-C identifica las funcionalidades situadas en el lado NTU del regenerador.

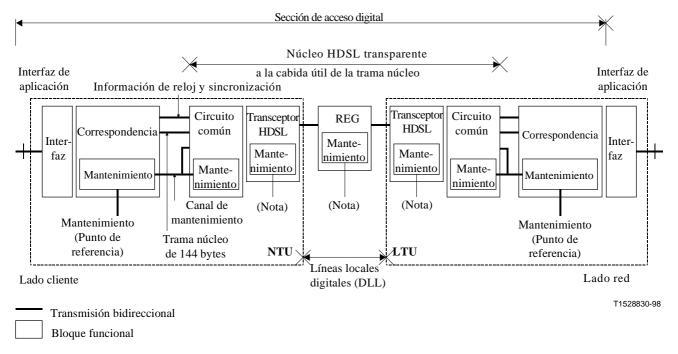

La figura 2 describe más claramente las funcionalidades de mantenimiento y de comunicación.

NOTA – Un núcleo HDSL totalmente equipado está formado por una combinación de uno, dos o tres H, REG y DLL, dependiendo de la velocidad de transmisión de datos del transceptor HDSL. Los REG son facultativos.

Figura 2/G.991.1 – Sección digital de acceso que emplea la tecnología HDSL (configuración detallada)

La información transmitida entre el lado NTU (lado subordinado) y el lado LTU (lado director) se trata como sigue:

En la interfaz de aplicación (I), el flujo de datos se agrupa en tramas de aplicación (por ejemplo, tramas a velocidad primaria RDSI de 32 intervalos de tiempo, como se especifica en la Recomendación I.431 [3]).

Para las aplicaciones a 2048 kbit/s, la función de correspondencia (parte del bloque funcional M) toma la trama de aplicación y la inserta en una trama núcleo de 144 bytes. (En algunas aplicaciones no todos los bytes de datos contendrán información válida y se pueden fijar a esquemas de reposo.) Para las aplicaciones a 1544 kbit/s, sólo el bit de alineación de trama se proporciona dos veces.

La trama núcleo se entrega al circuito común (C) donde se combina con cualesquiera bits de alineación, bits de mantenimiento y bits de tara necesarios, para ser enviada transparentemente en tramas HDSL por las DLL. La utilización de los REG es facultativa.

En el lado receptor, los datos dentro de las tramas HDSL son multiplexados por el circuito común para formar de nuevo la trama núcleo que es transferida a la función de correspondencia donde se hace corresponder con la trama de aplicación y es transmitida por la interfaz de aplicación (I).

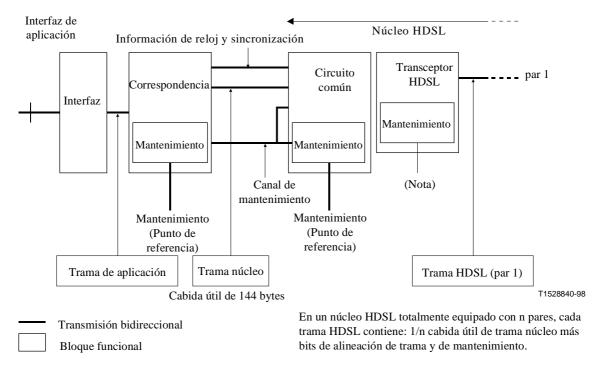

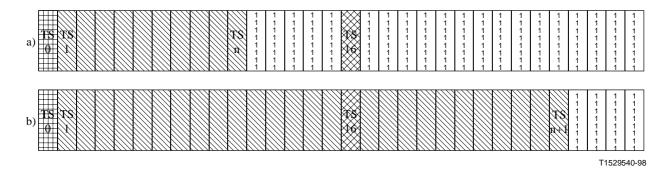

En la figura 3 se muestra una sinopsis de los diferentes procedimientos de alineación de trama.

NOTA – Un núcleo HDSL totalmente equipado está formado por una combinación de uno, dos o tres H, REG y DLL, dependiendo de la velocidad de transmisión de datos del transceptor HDSL. Los REG son facultativos.

Figura 3/G.991.1 – Visión general de los procedimientos de alineación de trama

Además, puede haber funciones de mantenimiento y/o de alimentación de energía asociadas con el núcleo HDSL para sustentar la identificación y localización de fallos y el control de arranque HDSL, aunque la presentación de esta información en el punto de referencia de mantenimiento está fuera del alcance de la presente Recomendación.

La finalidad de la especificación del núcleo HDSL es la interoperabilidad de dos equipos de fabricantes diferentes.

## 5 Especificación del núcleo HDSL

#### 5.1 Funciones

Las funciones enumeradas a continuación son necesarias para el funcionamiento correcto del núcleo HDSL.

| Funciones relacionadas con el núcleo HDSL                                            | LTU | NTU/REG           |

|--------------------------------------------------------------------------------------|-----|-------------------|

| Transporte transparente de tramas núcleo (144 bytes para aplicaciones a 2048 kbit/s) |     | $\leftrightarrow$ |

| Relleno y supresión de relleno                                                       |     | $\leftrightarrow$ |

| Procedimientos CRC-6 y detección de errores de transmisión                           |     | $\leftrightarrow$ |

| Informe de errores                                                                   |     | $\leftrightarrow$ |

| Detección de fallos                                                                  |     | $\leftrightarrow$ |

| Informe de fallos                                                                    |     | $\leftrightarrow$ |

| Temporización de bits                                                                |     | $\leftrightarrow$ |

| Alineación de trama                                                                  |     | $\leftrightarrow$ |

| Control de arranque autónomo del transceptor HDSL                                    |     | $\rightarrow$     |

| Funciones relacionadas con el núcleo HDSL                                      | LTU | NTU/REG           |

|--------------------------------------------------------------------------------|-----|-------------------|

| Control y coordinación de bucles                                               |     | $\rightarrow$     |

| Correspondencia de tramas núcleo con tramas HDSL                               |     | $\leftrightarrow$ |

| Control del canal de mantenimiento                                             |     | $\leftrightarrow$ |

| Sincronización y coordinación de transceptores HDSL                            |     | $\rightarrow$     |

| Identificación de pares (disponible solamente para aplicaciones a 2048 kbit/s) |     | $\leftrightarrow$ |

| Corrección de identificación de pares                                          |     | Nota              |

| NOTA – La corrección de pares es una función de la NTU.                        |     |                   |

| Funciones relacionadas con la alimentación de energía | LTU | NTU/REG       |

|-------------------------------------------------------|-----|---------------|

| Telealimentación (facultativa)                        |     | $\rightarrow$ |

| Corriente de humectación (facultativa)                |     | $\rightarrow$ |

## 5.1.1 Transporte transparente de tramas núcleo

Esta función proporciona la transmisión bidireccional de las tramas núcleo – por ejemplo con 144 bytes para aplicaciones de 2048 kbit/s – por uno, dos o tres sistemas de transceptor HDSL paralelos conectados por pares separados.

## 5.1.2 Relleno y supresión de relleno

Esta función proporciona la sincronización del reloj de datos de la aplicación con el reloj del sistema del transceptor HDSL, mediante la adición de ninguno o dos quats de relleno por trama HDSL.

## 5.1.3 Procedimientos CRC-6 y detección de errores de transmisión

Esta función proporciona la supervisión de la característica de error de los sistemas de transceptores HDSL en cada trama HDSL.

#### **5.1.4** Informe de errores

Esta función proporciona el informe de los errores detectados por medio del procedimiento CRC-6.

#### 5.1.5 Detección de fallos

Esta función proporciona la detección de los fallos en el sistema de transceptor HDSL.

#### 5.1.6 Informe de fallos

Esta función proporciona el informe de los fallos detectados en los sistemas del transceptor HDSL por medio de mensajes en el canal de mantenimiento es decir, mediante bits de tara de trama HDSL.

## 5.1.7 Temporización de bits

Esta función proporciona la temporización de bits (elemento de señal) para que los sistemas de transceptor HDSL puedan recuperar la información del tren de bits compuesto.

#### 5.1.8 Alineación de trama

Esta función proporciona información para que los sistemas de transceptor HDSL puedan recuperar la trama HDSL y la tara de trama HDSL.

## 5.1.9 Control de arranque autónomo del transceptor HDSL

Esta función proporciona la recuperación del estado operacional después de la primera alimentación de energía o interrupción de los sistemas de transceptor HDSL.

## 5.1.10 Control y coordinación de bucles

Esta función proporciona la activación y liberación de bucles en la LTU, el REG y la NTU.

## 5.1.11 Correspondencia entre tramas núcleo y tramas HDSL

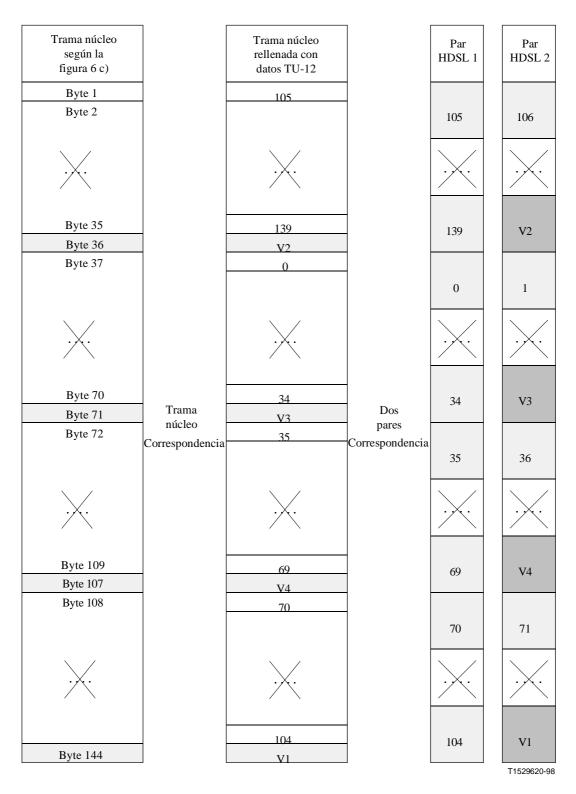

Esta función proporciona la correspondencia entre la trama núcleo – por ejemplo con 144 bytes para aplicaciones de 2048 kbit/s – y la trama o tramas HDSL.

#### 5.1.12 Control del canal de mantenimiento

Esta función proporciona el control del canal de mantenimiento formado por los bits de tara de la trama HDSL.

## 5.1.13 Sincronización y coordinación de transceptores HDSL

Esta función proporciona la sincronización de los sistemas de transceptor HDSL, la igualación de diferentes retardos de señal en los pares y la secuencia correcta de las señales que vienen de pares distintos.

## 5.1.14 Identificación de pares

Esta función proporciona la marca de los pares en la LTU/NTU – por ejemplo para aplicaciones de 2048 kbit/s que utilicen código de línea 2B1Q o CAP – por medio de dos o tres bits Z por par para permitir la identificación correcta de los pares.

#### 5.1.15 Corrección de identificación de pares

Esta función proporciona la realineación de la identificación de pares si se produce un intercambio no intencionado de pares y es detectado por la NTU.

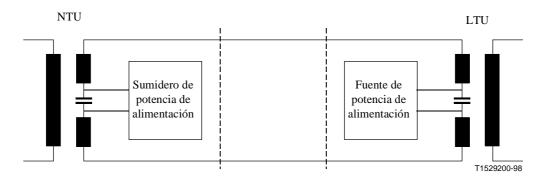

#### 5.1.16 Telealimentación

Esta función facultativa proporciona la telealimentación de la NTU, si no se proporciona ningún REG, o del REG de la LTU a través de los pares.

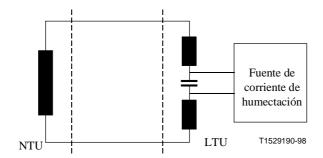

#### 5.1.17 Corriente de humectación

Esta función facultativa proporciona la alimentación de una corriente baja en los pares para mitigar el efecto de corrosión de contactos.

#### 5.2 Medio de transmisión

## 5.2.1 Descripción

El medio por el cual ha de funcionar el sistema de transmisión digital es la red de distribución de línea local.

Una red de distribución de línea local emplea cables de pares para proporcionar servicios a los clientes.

En la red de distribución de línea local, los clientes están conectados a la central local por líneas locales.

Una línea local metálica puede transportar simultáneamente información digital bidireccional en el formato HDSL apropiado.

Para simplificar la provisión de HDSL, un sistema de transmisión digital debe ser capaz de funcionar satisfactoriamente por la mayoría de las líneas locales metálicas sin necesidad de ningún acondicionamiento especial. Con el fin de poder utilizar los sistemas de transmisión HDSL por el

mayor número posible de líneas locales, las restricciones impuestas por los requisitos HDSL se mantienen en el mínimo necesario para garantizar un funcionamiento aceptable.

## 5.2.2 Requisitos mínimos de la línea local digital (DLL) para las aplicaciones HDSL

- ninguna bobina de carga;

- sólo pares torcidos o cable en cuadrete;

- ningún apantallamiento adicional necesario;

- cuando están presentes derivaciones de puente, el número máximo se limitará a 2 y la longitud de cada una a 500 metros.

#### 5.2.3 Características físicas de la DLL

Una DLL está formada por una o más secciones de cable que están empalmados o interconectados juntos.

El cable de distribución o principal está estructurado como sigue:

- cascada de secciones de cable de diferentes diámetros y longitudes;

- puede haber hasta dos derivaciones de puente (BT, bridged tap) en distintos puntos en los cables de instalación y distribución.

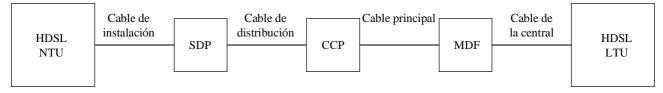

En la figura 4 se muestra una descripción general del modelo físico de la DLL y en el cuadro 1 se dan ejemplos típicos de las características de los cables, de conformidad con la Recomendación G.960 [2].

T1528850-98

- SDP Punto de distribución de abonado (subscriber distribution point)

- CCP Punto de transconexión (cross connect point)

- MDF Repartidor principal (main distribution frame)

Figura 4/G.991.1 – Modelo físico de DLL

Cuadro 1/G.991.1 – Características del cable

|                                                                                                                                                                                                                                                                                                                                                                                                                | Cable de la central                                                  | Cable principal                 | Cable de<br>distribución | Cable de la<br>instalación                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|--------------------------|---------------------------------------------------|--|

| Diámetro del hilo (mm)                                                                                                                                                                                                                                                                                                                                                                                         | 0,5; 0,6;<br>0,32; 0,4                                               | 0,3-1,4                         | 0,3-1,4                  | 0,4; 0,5;<br>0,6; 0,8;<br>0,9; 0,63               |  |

| Estructura                                                                                                                                                                                                                                                                                                                                                                                                     | SQ (B) o<br>TP (L)                                                   | SQ (B) o TP (L)                 | SQ (B) o TP (L)          | SQ o TP o UP                                      |  |

| Número máximo de pares                                                                                                                                                                                                                                                                                                                                                                                         | 1200                                                                 | 2400 (0,4 mm)<br>4800 (0,32 mm) | 600 (0,4 mm)             | 2 (aéreo)<br>600 (encastrado)                     |  |

| Instalación                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      | Enterrado en conductos          | Enterrado o aéreo        | Aéreo (acometida)<br>En conductos<br>(encastrado) |  |

| Capacidad<br>(nF/km en 800 Hz)                                                                                                                                                                                                                                                                                                                                                                                 | 55 120                                                               | 25 60                           | 25 60                    | 35 120                                            |  |

| Aislamiento del hilo                                                                                                                                                                                                                                                                                                                                                                                           | niento del hilo PVC, FRPE PE, pulpa de papel, PE, PE PE, PVC celular |                                 | PE, PVC                  |                                                   |  |

| TP Pares torcidos PE Polietileno SQ Cuadretes en estrella PVC Cloruro de polivinilo UP Pares no torcidos Pulpa Pulpa de papel L Capa PE cel. Polietileno celular B Haces (unidades) FRPE PE resistente al fuego NOTA – La finalidad de este cuadro es describir los cables actualmente instalados en el bucle local. No todos los tipos de cable indicados anteriormente son adecuados para los sistemas HDSL. |                                                                      |                                 |                          |                                                   |  |

## 5.2.4 Características eléctricas de la DLL

La señal transmitida sufrirá degradaciones debido a diafonía, ruido impulsivo y las características de la variación no lineal en función de la frecuencia de la DLL. Estas degradaciones se describen más detalladamente en las subcláusulas siguientes.

#### **5.2.4.1** Principales características

Las principales características eléctricas que varían no linealmente en función de la frecuencia son:

- pérdida de inserción;

- retardo de grupo;

- impedancia característica, que comprende partes reales e imaginarias.

El valor máximo de pérdida de inserción especificado para los sistemas de transmisión HDSL se define en la cláusula 6, para sistemas de uno, dos y tres pares.

NOTA – El término retardo de grupo se define en el Fascículo I.3 [4].

#### 5.2.4.2 Diferencias de las características de transmisión físicas entre pares en la DLL

Entre la LTU y la NTU las características de los pares pueden diferir. Esta diferencia puede estribar en el diámetro del hilo, el tipo de aislamiento, la longitud, el número y longitud de derivaciones puenteadas y la exposición a degradaciones. Estas diferencias de las características de transmisión pueden variar con el tiempo.

El circuito común compensará cualesquiera diferencias en el tiempo de transmisión debido a estas diferencias de pares (véase la cláusula 6).

Se recomienda que la diferencia de retardo de transferencia de la señal entre cada uno de los dos o tres pares esté limitada a un máximo de 50 µs en 150 kHz, lo que corresponde a una diferencia de 10 km en la longitud de línea entre la LTU y la NTU.

#### 5.2.4.3 Características de la diafonía

En general, el ruido de diafonía se debe a la pérdida por acoplamiento finita entre pares que comparten el mismo cable, especialmente los pares que están físicamente adyacentes. La pérdida por acoplamiento finita entre pares origina un vestigio de la señal que le fluye por una DLL (DLL perturbadora) para acoplarse en una DLL adyacente (DLL perturbada). Este vestigio se conoce como ruido de diafonía.

Se supone que la paradiafonía (NEXT, near-end crosstalk) sea el tipo de diafonía predominante.

La NEXT entre sistemas se produce cuando los pares que transportan sistemas de transmisión digital diferentes interfieren entre sí.

La NEXT dentro del sistema o NEXT propia se produce cuando todos los pares que interfieren entre sí en un cable transportan el mismo sistema de transmisión digital. El ruido de NEXT dentro del sistema acoplado en una DLL perturbada por varias DLL perturbadoras se puede representar como causado por una sola DLL perturbadora equivalente con una pérdida de acoplamiento en función de las características de frecuencia, que se conoce como pérdida evaluada por suma de potencias (PSL, power sum loss). Los valores para la pérdida por NEXT del caso más desfavorable de 1% varían de 40 dB a 70 dB en 150 kHz, dependiendo del tipo de cable, del número de perturbaciones y del entorno.

Para probar los sistemas HDSL, la NEXT se representa mediante un ruido artificial definido en la cláusula 6.

## 5.2.4.4 Asimetría con respecto a tierra

La DLL tendrá asimetría finita con respecto a tierra. Esta asimetría se describe como la atenuación de conversión longitudinal (LCL, *longitudinal conversion loss*). El valor del caso más desfavorable previsto es 42,5 dB en 150 kHz disminuyendo en función de la frecuencia en 5 dB/década.

## 5.2.4.5 Ruido impulsivo

La DLL tendrá ruido impulsivo resultante de otros sistemas que comparten los mismos cables, así como de otras fuentes. Los requisitos de tolerancia al ruido impulsivo se describen detalladamente en la cláusula 6.

#### **5.2.4.6** Microinterrupciones

Una microinterrupción es una interrupción temporal de la línea debida a una acción mecánica externa en los hilos de cobre que constituyen el trayecto de transmisión, por ejemplo, en un empalme del cable. Los empalmes pueden ser uniones de hilo a hilo hechas manualmente y durante la vida del cable, los fenómenos de oxidación y las vibraciones mecánicas pueden inducir microinterrupciones en estos puntos críticos.

El efecto de una microinterrupción en el sistema de transmisión puede ser un fallo del enlace de transmisión digital, junto con un fallo de la alimentación (si se proporciona) durante la microinterrupción.

El objetivo es que en presencia de una microinterrupción de una longitud máxima especificada, el sistema no debe reiniciarse, y debe reactivarse automáticamente con un procedimiento de arranque completo si se produce una reiniciación debida a una interrupción. Los requisitos de tolerancia a las

microinterrupciones, junto con las directrices para un conjunto de pruebas de sensibilidad en laboratorio, se indican en la cláusula 6.

#### 5.3 Método de transmisión

#### 5.3.1 Generalidades

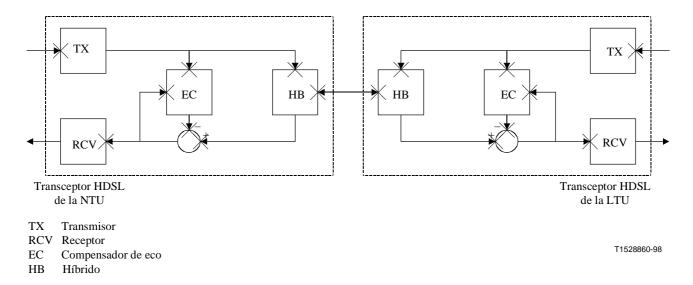

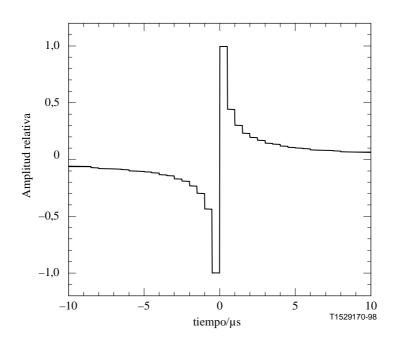

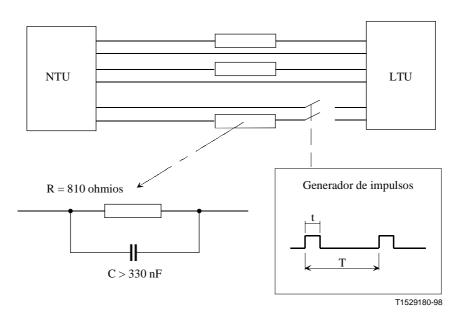

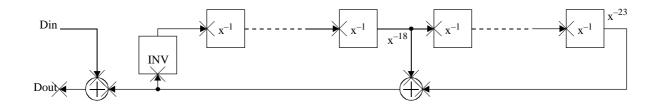

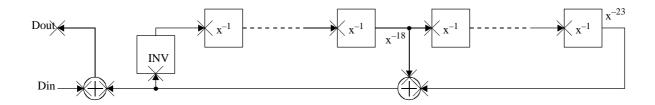

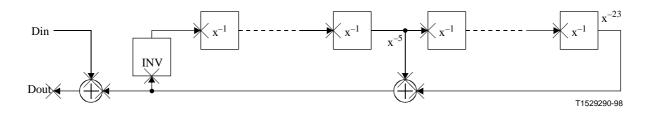

El sistema proporciona la transmisión dúplex por líneas locales metálicas a 2 hilos. La transmisión dúplex se logrará mediante el uso de un híbrido de compensación de eco (ECH, *echo cancellation hybrid*). Con el método de compensación de eco, ilustrado en la figura 5, el compensador de eco (EC, *echo canceller*) produce una réplica del eco de la señal transmitida que se substrae de la señal recibida total. El eco es el resultado de la simetría imperfecta del híbrido y de las discontinuidades de impedancia causadas, por ejemplo, por el empalme de diferentes clases de cables.

Figura 5/G.991.1 – Diagrama funcional del método de compensación de eco

## 5.3.2 Transmisión por tres pares

La transmisión por tres DLL se proporciona mediante tres transceptores HDSL paralelos, cada uno de los cuales funciona a 784 kbit/s y utiliza el código de línea 2B1Q.

## 5.3.3 Transmisión por dos pares

La transmisión por dos DLL se proporciona mediante dos transceptores HDSL paralelos, cada uno de los cuales funciona a 1168 kbit/s empleando el código de línea 2B1Q o CAP para aplicaciones de 2048 kbit/s o a 784 kbit/s empleando el código de línea 2B1Q para aplicaciones de 1544 kbit/s.

## 5.3.4 Transmisión por un par

La transmisión por una DLL se proporciona mediante un transceptor HDSL que funciona a 2320 kbit/s y utiliza el código de línea 2B1Q o CAP.

## 5.3.5 Transmisión por cuatro pares

No se excluye la transmisión de la trama núcleo completa por cuatro pares, pero actualmente no se trata aquí.

#### 5.3.6 Código de línea

El código de línea descrito en la parte principal de la presente Recomendación es el 2B1Q (dos binario, uno cuaternario). En el anexo B figura una descripción detallada del CAP.

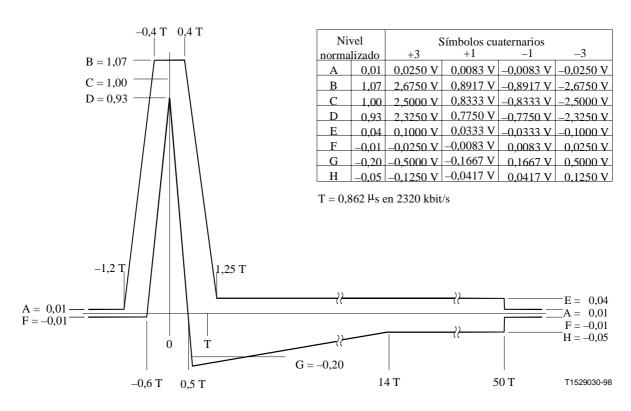

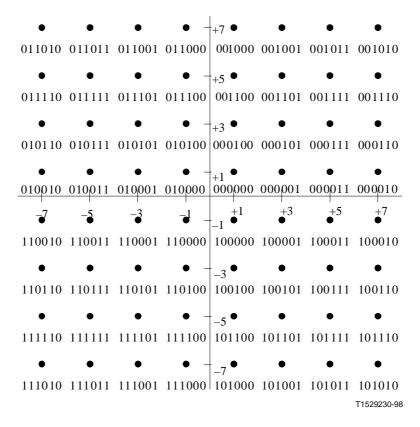

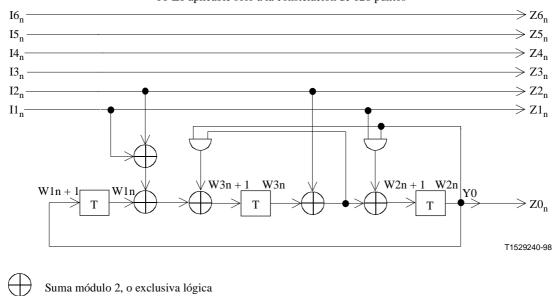

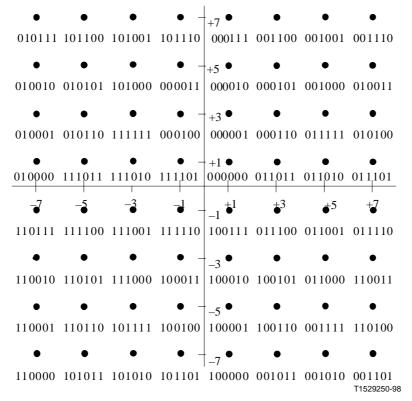

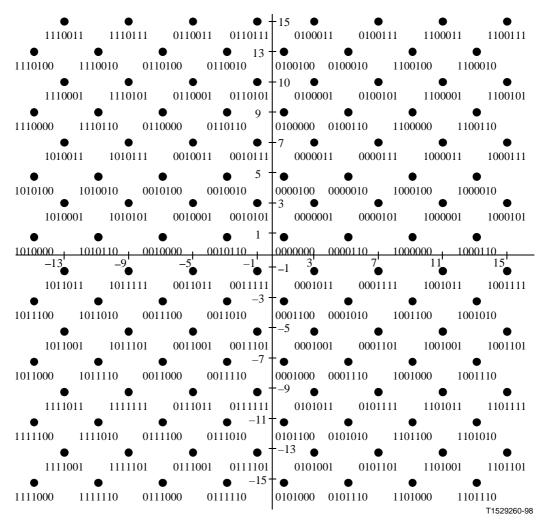

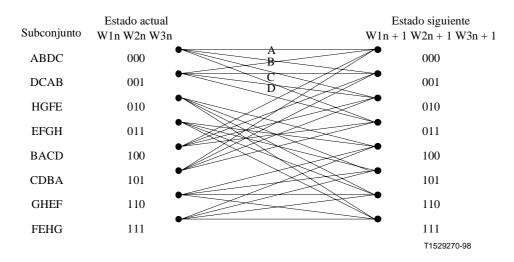

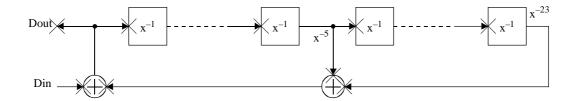

Antes de la transmisión, el tren de bits en cada transceptor HDSL de la figura 1, salvo la palabra de sincronización que tiene un esquema fijo, se agrupará en pares de bits que son convertidos a símbolos cuaternarios (quats), como se especifica en el cuadro 2. En el receptor, se realizan las operaciones inversas.

Primer bit Segundo bit Símbolo (Signo) (Magnitud) cuaternario 1 0 +3 1 1 +10 1 -10 0 -3

Cuadro 2/G.991.1 – Codificación 2B1Q

## 5.3.7 Velocidad de símbolo por la línea

La velocidad de símbolo del transceptor HDSL será:

- 392 kbaudios  $\pm$  32 ppm para un sistema de tres pares,

- 584 kbaudios  $\pm$  32 ppm para un sistema de dos pares,

- 1160 kbaudios  $\pm$  32 ppm para un sistema de un par.

#### 5.4 Estructura de trama

#### 5.4.1 Trama núcleo

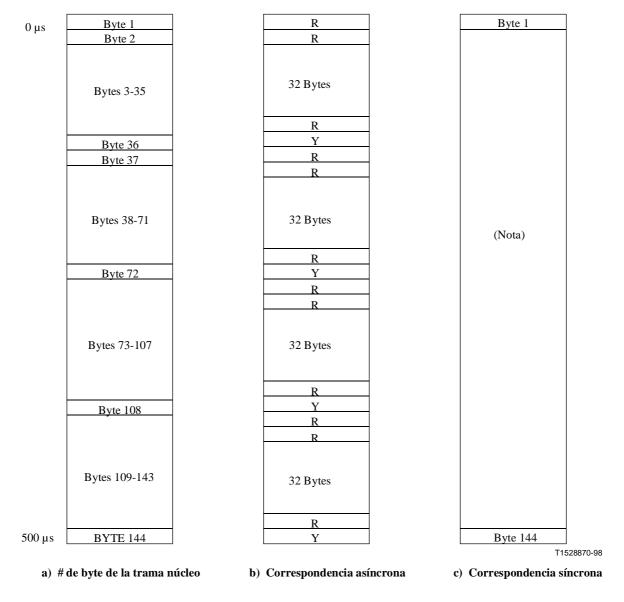

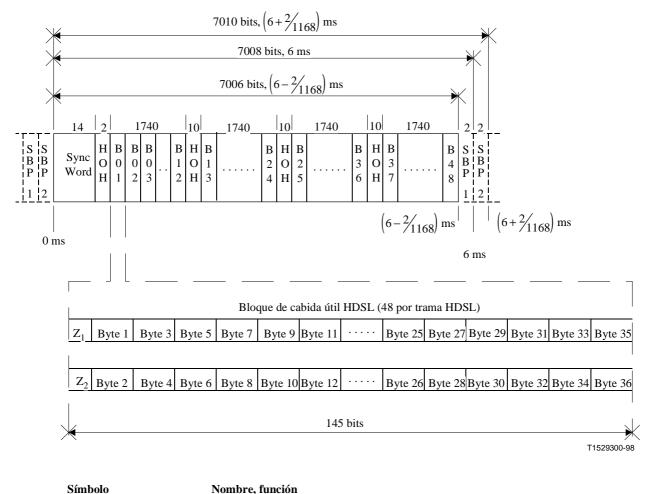

Dentro del bloque funcional de correspondencia, como se indica en la figura 3 de la configuración de referencia, la trama dependiente de la aplicación que contiene la cabida útil se inserta en una trama núcleo que dura 500 µs y que contiene 144 bytes, como se muestra en la figura 6. Existen diferentes opciones de correspondencias que dependen de las aplicaciones especiales, como se muestra también en la figura 6. Los detalles de los procedimientos de correspondencia para las diferentes aplicaciones se describen en la apéndice I. Las tramas núcleo con 144 bytes/500 µs forman un tren de bits continuo con una velocidad binaria de 2304 kbit/s que en sistemas de dos o tres pares se dividen byte por byte en tramas HDSL paralelas que se transmiten por cada uno de los sistemas de transceptor HDSL.

R, Y Relleno fijo

NOTA – La trama núcleo y la cabida útil están sincronizadas. Los detalles de la asignación de intervalos de tiempo que son dependientes de la aplicación se indican en las subcláusulas pertinentes de la cláusula 7.

Figura 6/G.991.1 – Trama núcleo

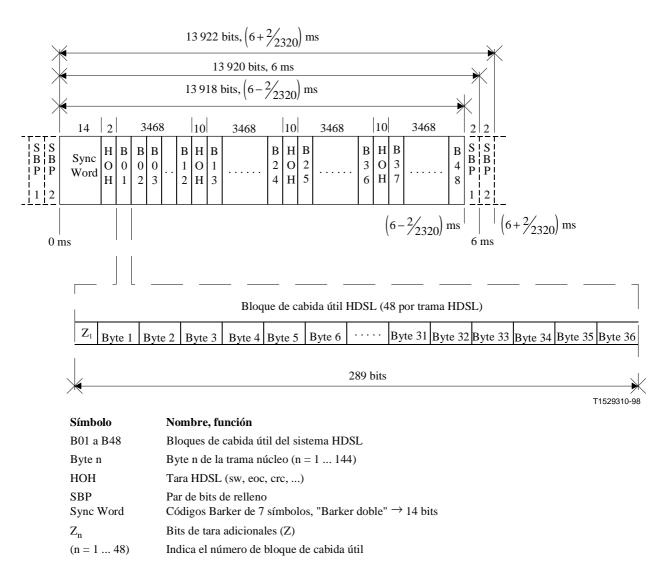

## 5.4.2 Trama HDSL 2B1Q

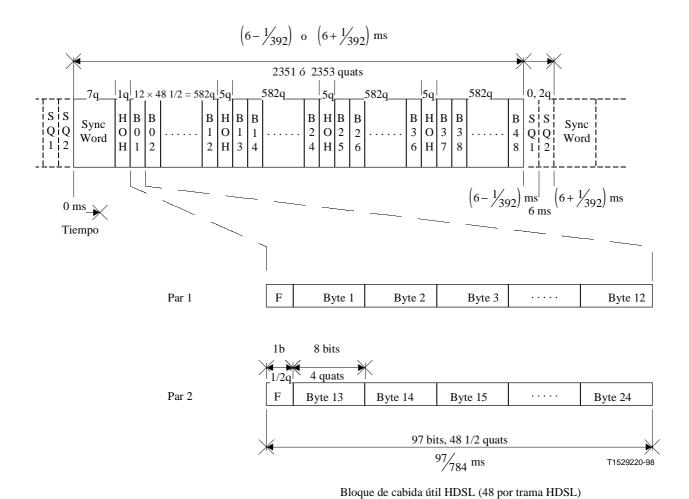

A continuación se describe la estructura propuesta de la trama HDSL en el formato binario antes de la aleatorización y codificación. Esta estructura es válida durante el funcionamiento normal después de la sincronización de temporización de símbolos, la alineación de trama y después que todos los coeficientes internos del transceptor han sido estabilizados suficientemente para permitir el transporte fiable de las señales a través de los sistemas de transceptor HDSL.

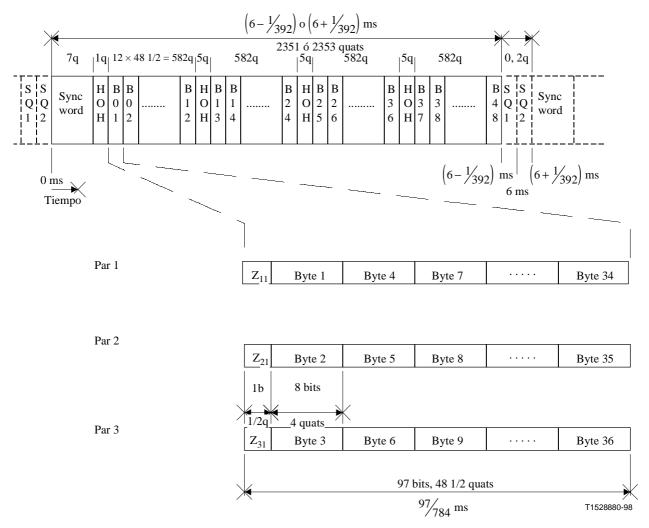

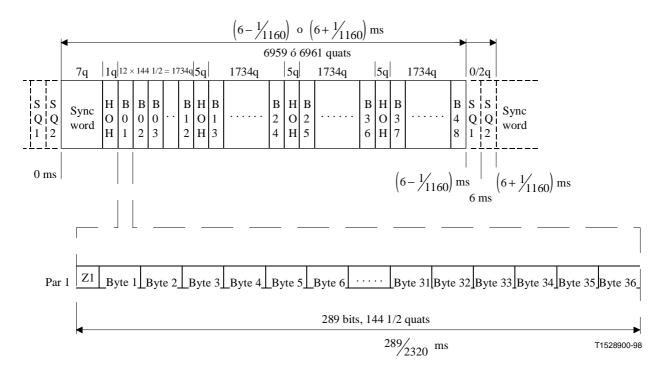

- La duración nominal de la trama HDSL es 6 ms.

- La longitud media de la trama HDSL para el sistema de tres pares es 2352 quats (equivalentes a 4704 bits) en 6 ms. Cada trama contiene 0 ó 2 quats de relleno, lo que da una longitud real de 2351 quats en  $6 \frac{1}{3}$ 92 ms o 2353 quats en  $6 + \frac{1}{3}$ 92 ms.

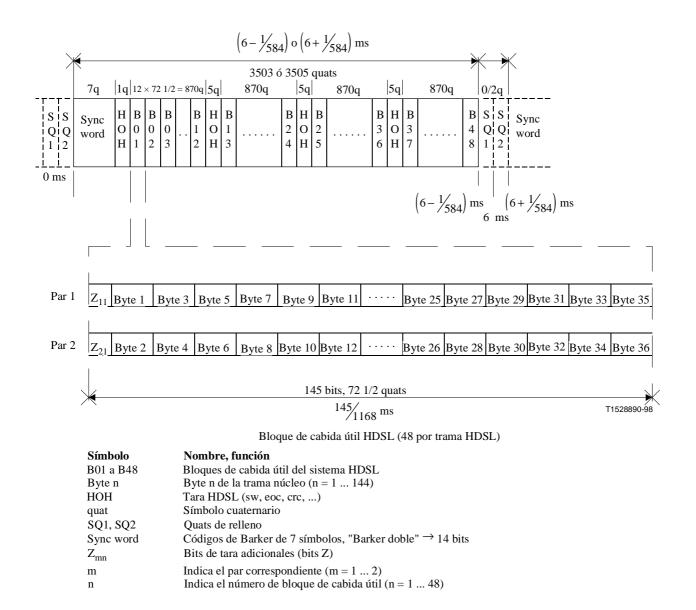

- La longitud media de la trama HDSL para el sistema de dos pares es 3504 quats (equivalentes a 7008 bits) en 6 ms. Cada trama contiene 0 ó 2 quats de relleno, lo que da una longitud real de 3503 quats en  $6 \frac{1}{584}$  ms o 3505 quats en  $6 + \frac{1}{584}$  ms.

- La longitud media de la trama HDSL para el sistema de dos pares es 6960 quats (equivalentes a 13 920 bits) en 6 ms. Cada trama contiene 0 ó 2 quats de relleno lo que da una longitud real de 6959 quats en  $6 \frac{1}{1160}$  ms o 6961 quats en  $6 + \frac{1}{1160}$  ms.

- La asignación de bits en cada trama HDSL en cada sentido de transmisión para todos los pares se muestra en los cuadros 3, 4 y 5.

- Los sistemas de transceptor HDSL acomodarán cada uno independientemente diferencias en la temporización de bits en los dos sentidos de transmisión o de los datos de aplicación y el sistema de transceptor HDSL incluyendo ninguno o dos quats de relleno al final de la trama HDSL.

- En la LTU, la velocidad de trama en los diferentes pares se derivará de la misma fuente. La colocación de la palabra de sincronización, es decir, el comienzo de las tramas HDSL en los diferentes pares, estará sincronizada. El retardo máximo entre el comienzo de las tramas será inferior a un periodo de símbolo, medido en el lado de la línea de cada transceptor HDSL.

- La inserción de quats de relleno, si es necesaria, será idéntica para todos los pares.

Cuadro 3/G.991.1 – Estructura de trama HDSL para el sistema de tres pares

| Tiempo | Bit de<br>trama # | Bit<br>HOH# | Nombre<br>abreviado | Nombre completo                                                                     | Notas                                                         |

|--------|-------------------|-------------|---------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 0 ms   | 1-14              | 1-14        | SW 1-14             | Palabra de sincronización                                                           | Código Barker doble                                           |

|        | 15                | 15          | losd                | Pérdida de entrada de señal<br>en la interfaz de aplicación<br>del extremo distante |                                                               |

|        | 16                | 16          | febe                | Error de bloque de extremo distante                                                 | Cabida útil HDSL incluidos Z <sub>m1</sub> -Z <sub>m12</sub>  |

|        | 17-1180           | _           | B01-B12             | Bloques de cabida útil 1-12                                                         |                                                               |

|        | 1181              | 17          | eoc01               | Dirección eoc                                                                       |                                                               |

|        | 1182              | 18          | eoc02               | Dirección eoc                                                                       |                                                               |

|        | 1183              | 19          | eoc03               | Datos eoc/código<br>operacional                                                     |                                                               |

|        | 1184              | 20          | eoc04               | Byte impar/par eoc                                                                  |                                                               |

|        | 1185              | 21          | crc1                | Verificación redundancia cíclica                                                    | CRC-6                                                         |

|        | 1186              | 22          | crc2                | Verificación redundancia cíclica                                                    | CRC-6                                                         |

|        | 1187              | 23          | ps1                 | Bit estado potencia NTU 1                                                           | Sólo NTU → LTU                                                |

|        | 1188              | 24          | ps2                 | Bit estado potencia NTU 2                                                           | Sólo NTU → LTU                                                |

|        | 1189              | 25          | bpv                 | Violación bipolar                                                                   |                                                               |

|        | 1190              | 26          | eoc05               | eoc no especificado                                                                 |                                                               |

|        | 1191-2354         | _           | B13-B24             | Bloques de cabida útil 13-24                                                        | Cabida útil HDSL incluidos Z <sub>m13</sub> -Z <sub>m24</sub> |

Cuadro 3/G.991.1 – Estructura de trama HDSL para el sistema de tres pares (fin)

| Tiempo                 | Bit de<br>trama # | Bit<br>HOH# | Nombre<br>abreviado | Nombre completo                   | Notas                                                         |

|------------------------|-------------------|-------------|---------------------|-----------------------------------|---------------------------------------------------------------|

|                        | 2355              | 27          | eoc06               | Bit de mensaje eoc 1              |                                                               |

|                        | 2356              | 28          | eoc07               | Bit de mensaje eoc 2              |                                                               |

|                        | 2357              | 29          | eoc08               | Bit de mensaje eoc 3              |                                                               |

|                        | 2358              | 30          | eoc09               | Bit de mensaje eoc 4              |                                                               |

|                        | 2359              | 31          | crc3                | Verificación redundancia cíclica  | CRC-6                                                         |

|                        | 2360              | 32          | crc4                | Verificación redundancia cíclica  | CRC-6                                                         |

|                        | 2361              | 33          | hrp                 | Regenerador presente              | $LTU \leftarrow REG \rightarrow NTU$                          |

|                        | 2362              | 34          | rrbe                | Error bloque distante regenerador | $LTU \leftarrow REG \rightarrow NTU$                          |

|                        | 2363              | 35          | rcbe                | Error bloque central regenerador  | $LTU \leftarrow REG \rightarrow NTU$                          |

|                        | 2364              | 36          | rega                | Alarma de regenerador             | $LTU \leftarrow REG \rightarrow NTU$                          |

|                        | 2365-3528         | _           | B25-B36             | Bloques de cabida útil 25-36      | Cabida útil HDSL incluidos Z <sub>m25</sub> -Z <sub>m36</sub> |

|                        | 3529              | 37          | eoc10               | Bit de mensaje eoc 5              |                                                               |

|                        | 3530              | 38          | eoc11               | BIt de mensaje eoc 6              |                                                               |

|                        | 3531              | 39          | eoc12               | Bit de mensaje eoc 7              |                                                               |

|                        | 3532              | 40          | eoc13               | Bit de mensaje eoc 8              |                                                               |

|                        | 3533              | 41          | crc5                | Verificación redundancia cíclica  | CRC-6                                                         |

|                        | 3534              | 42          | crc6                | Verificación redundancia cíclica  | CRC-6                                                         |

|                        | 3535              | 43          | rta                 | Alarma terminal distante          | Sólo NTU → LTU                                                |

|                        | 3536              | 44          | indc/indr           | Preparado para recibir            | $indc = LTU \rightarrow NTU$                                  |

|                        |                   |             |                     |                                   | $indr = NTU \rightarrow LTU$                                  |

|                        | 3537              | 45          | uib                 | Bit indicador no especificado     |                                                               |

|                        | 3538              | 46          | uib                 | Bit indicador no especificado     |                                                               |

| $6 - \frac{1}{392}$ ms | 3539-4702         | _           | B37-B48             | Bloques de cabida útil 37-48      | Cabida útil HDSL incluidos Z <sub>m37</sub> -Z <sub>m48</sub> |

|                        | 4703              | 47          | stq1s               | Signo quat de relleno 1           | Relleno de trama                                              |

| 6 ms nominal           | 4704              | 48          | stq1m               | Magnitud quat de relleno 1        | Relleno de trama                                              |

|                        | 4705              | 49          | stq2s               | Signo quat de relleno 2           | Relleno de trama                                              |

| $6 + \frac{1}{392}$ ms | 4706              | 50          | stq2m               | Magnitud quat de relleno 2        | Relleno de trama                                              |

Cuadro 4/G.991.1 – Estructura de trama HDSL para el sistema de dos pares

| Tiempo | Bit de<br>trama # | Bit<br>HOH# | Nombre<br>abreviado | Nombre completo                                                                     | Notas                                                         |

|--------|-------------------|-------------|---------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 0 ms   | 1-14              | 1-14        | SW 1-14             | Palabra de sincronización                                                           | Código Barker doble                                           |

|        | 15                | 15          | losd                | Pérdida de entrada de señal<br>en la interfaz de aplicación<br>del extremo distante |                                                               |

|        | 16                | 16          | febe                | Error de bloque de extremo distante                                                 |                                                               |

|        | 17-1756           | _           | B01-B12             | Bloques de cabida útil 1-12                                                         | Cabida útil HDSL incluidos $Z_{m1}$ - $Z_{m12}$               |

|        | 1757              | 17          | eoc01               | Dirección eoc                                                                       |                                                               |

|        | 1758              | 18          | eoc02               | Dirección eoc                                                                       |                                                               |

|        | 1759              | 19          | eoc03               | Datos eoc/código<br>operacional                                                     |                                                               |

|        | 1760              | 20          | eoc04               | Byte impar/par eoc                                                                  |                                                               |

|        | 1761              | 21          | crc1                | Verificación redundancia cíclica                                                    | CRC-6                                                         |

|        | 1762              | 22          | crc2                | Verificación redundancia cíclica                                                    | CRC-6                                                         |

|        | 1763              | 23          | ps1                 | Bit estado potencia NTU 1                                                           | Sólo NTU → LTU                                                |

|        | 1764              | 24          | ps2                 | Bit estado potencia NTU 2                                                           | Sólo NTU → LTU                                                |

|        | 1765              | 25          | bpv                 | Violación bipolar                                                                   |                                                               |

|        | 1766              | 26          | eoc05               | eoc no especificado                                                                 |                                                               |

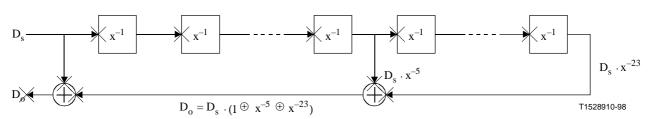

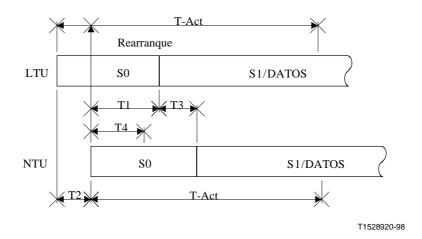

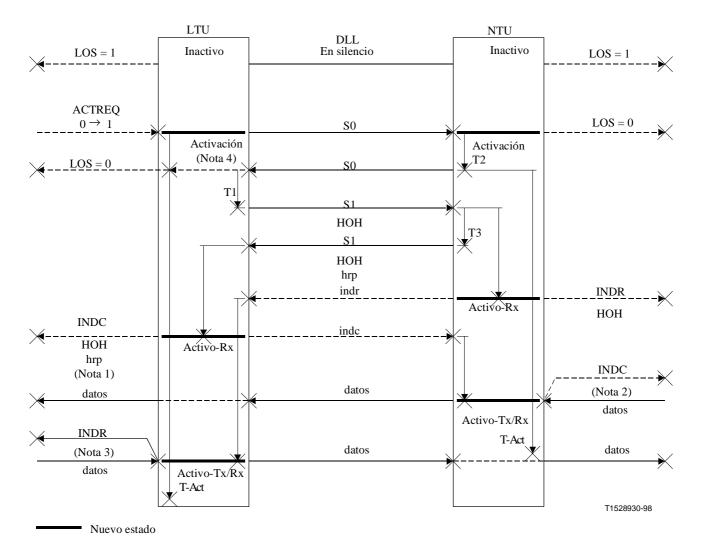

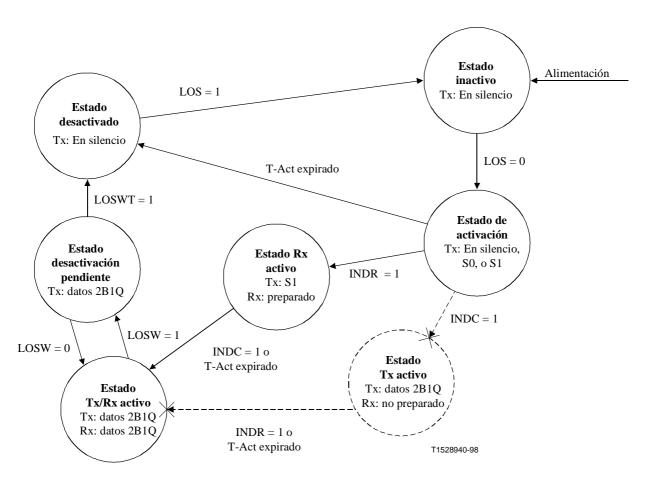

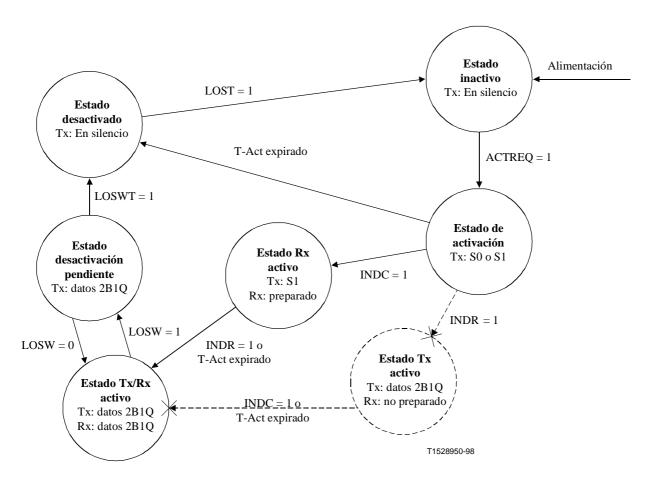

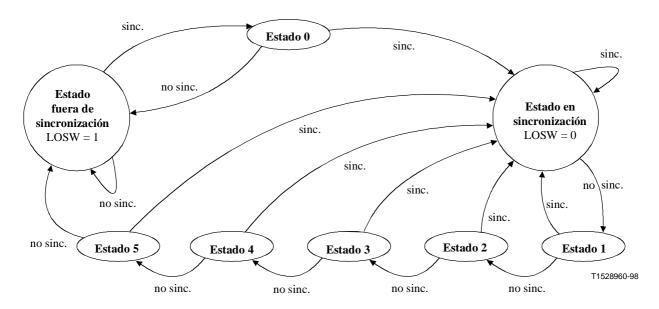

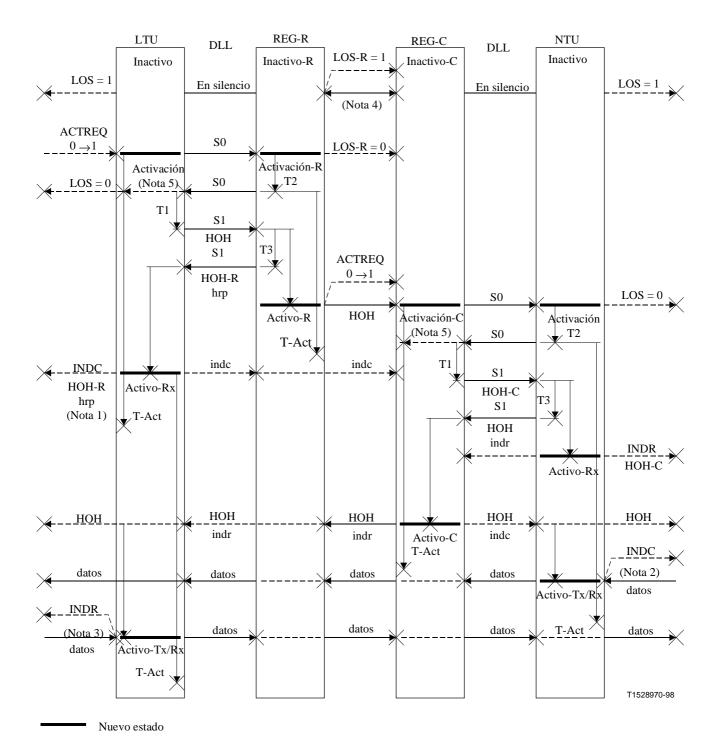

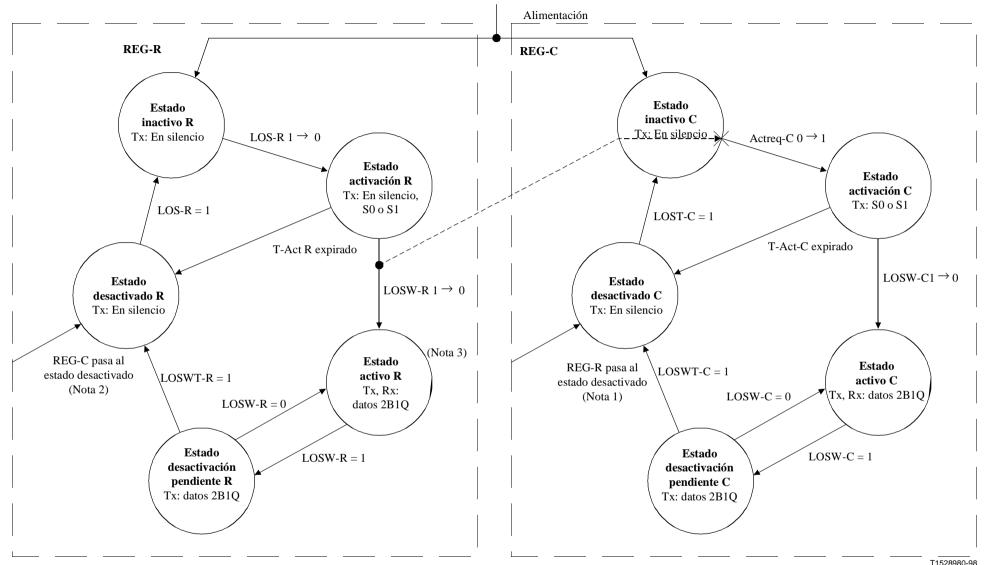

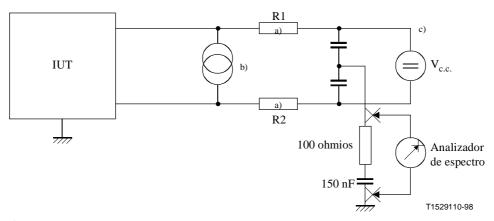

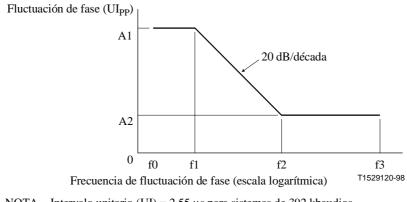

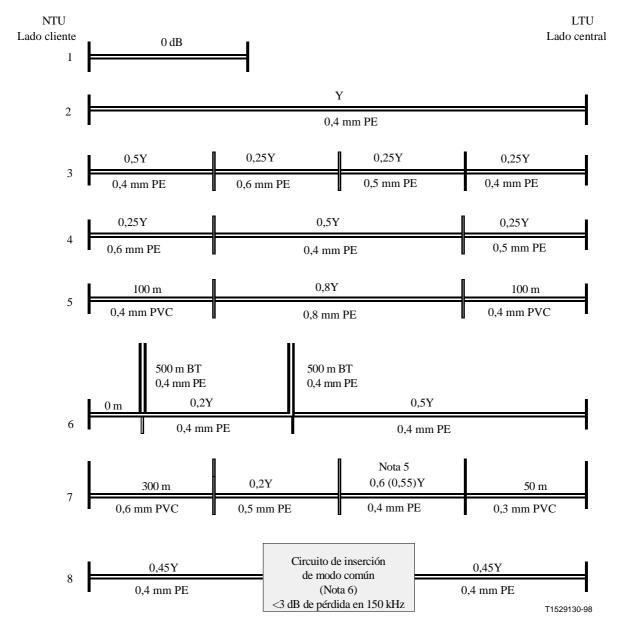

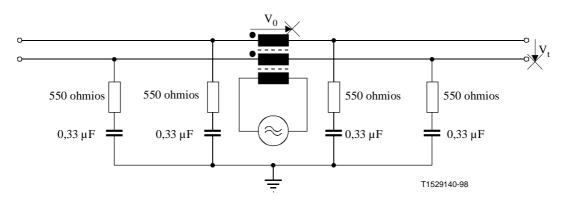

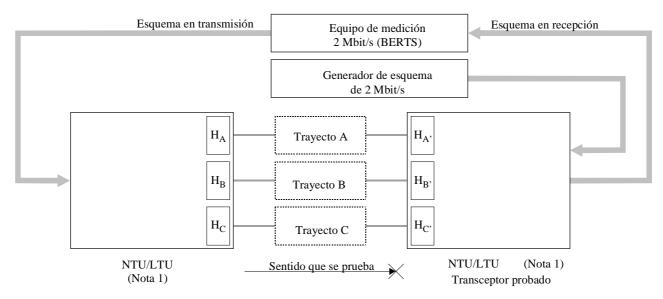

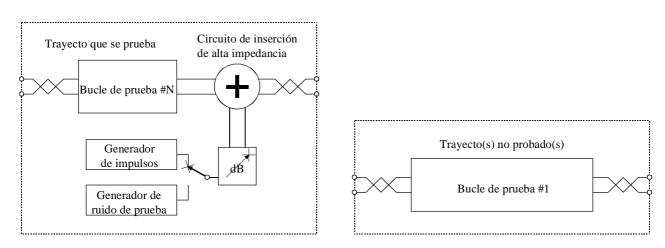

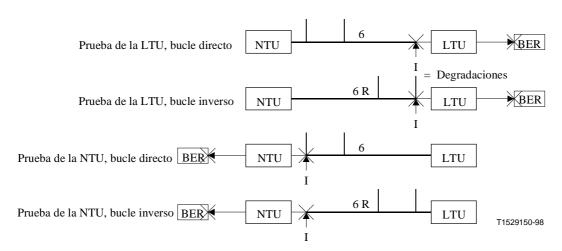

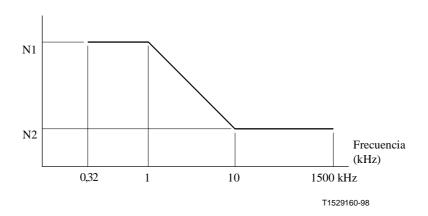

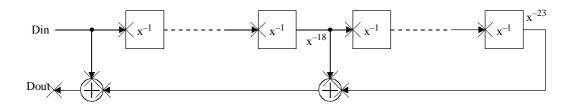

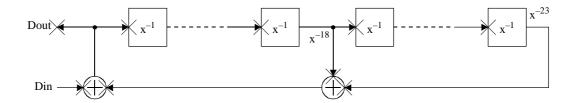

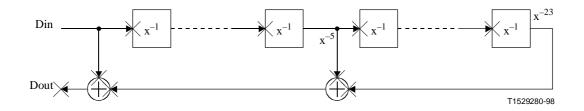

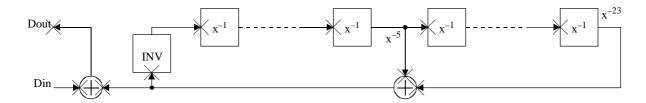

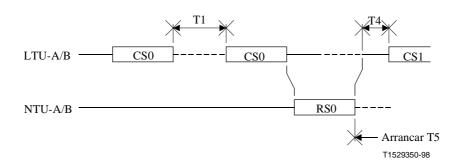

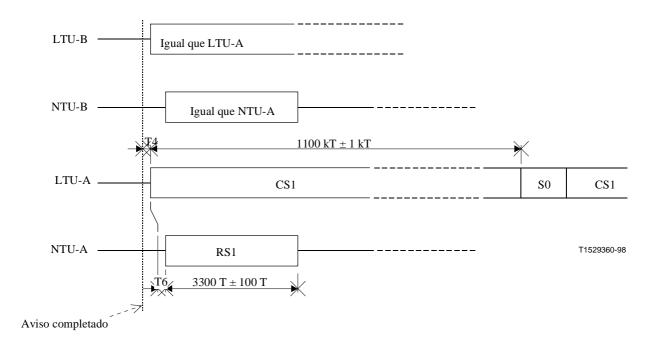

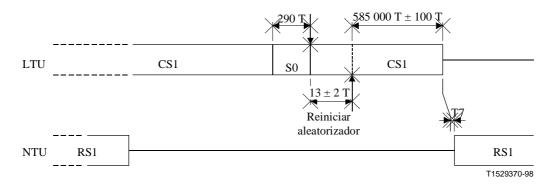

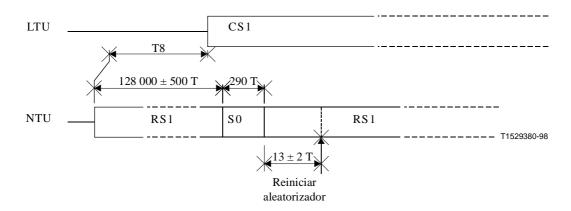

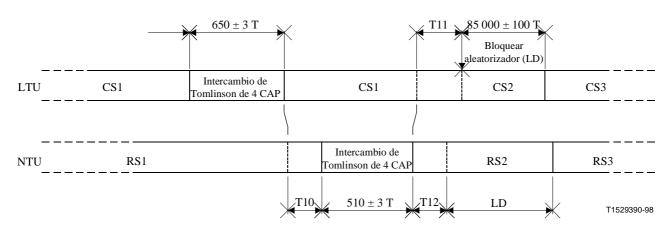

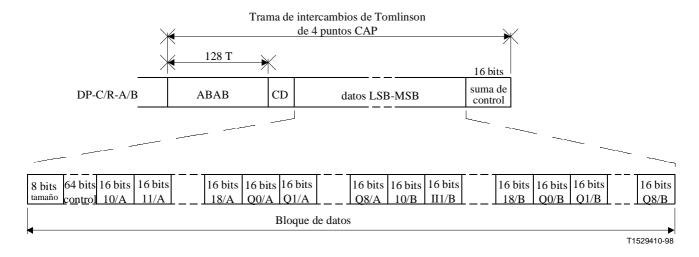

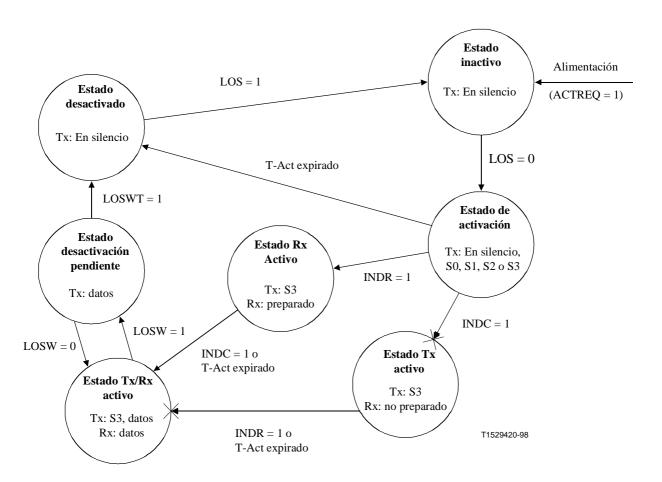

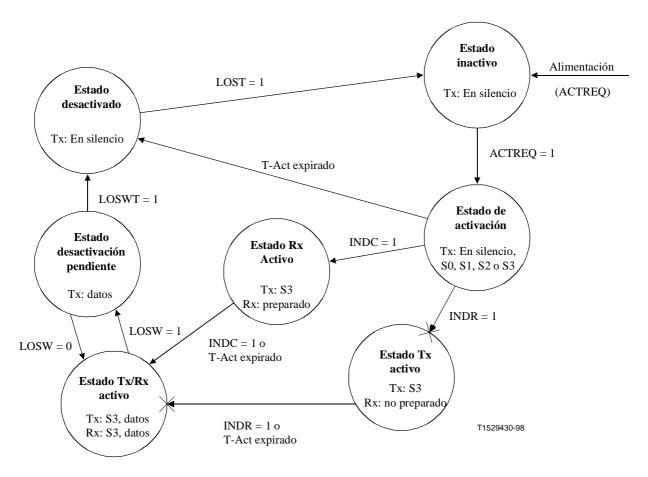

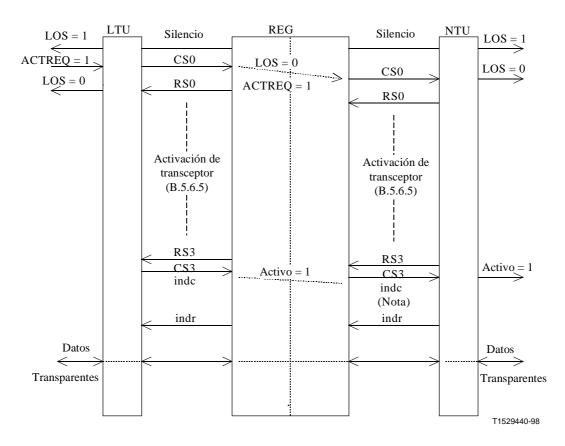

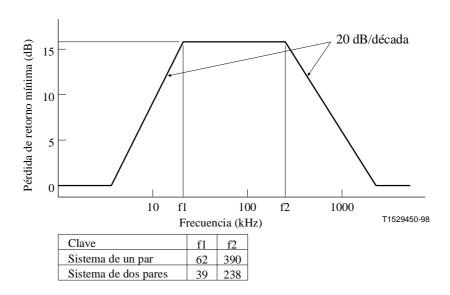

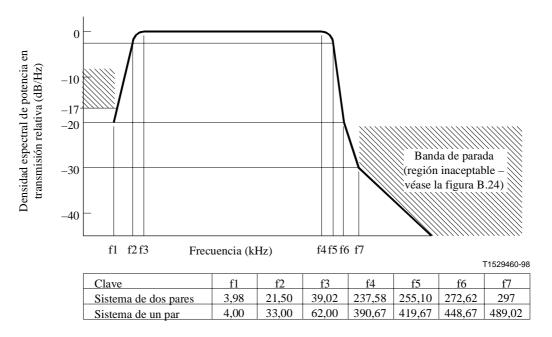

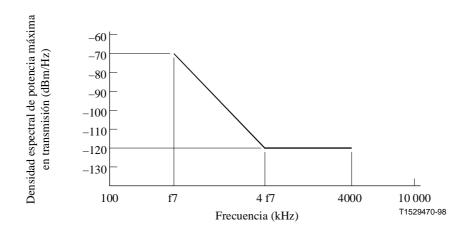

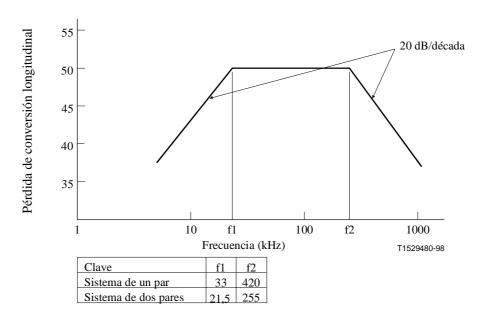

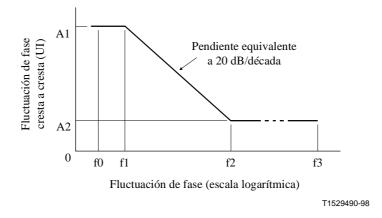

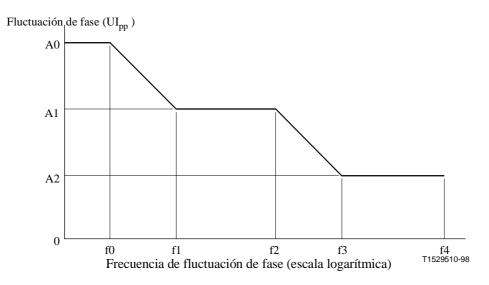

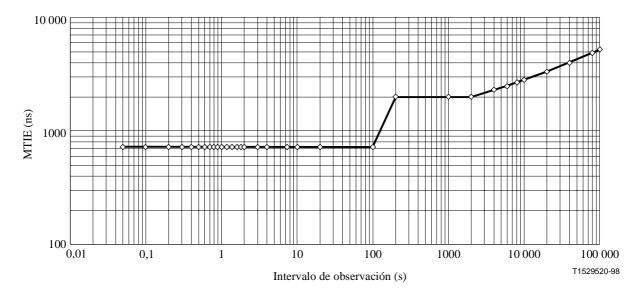

|        | 1767-3506         | _           | B13-B24             | Bloques de cabida útil 13-24                                                        | Cabida útil HDSL incluidos Z <sub>m13</sub> -Z <sub>m24</sub> |