ITU-T

G.781

TELECOMMUNICATION STANDARDIZATION SECTOR OF ITU (08/2017)

SERIES G: TRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKS

Digital terminal equipments – Principal characteristics of multiplexing equipment for the synchronous digital hierarchy

# Synchronization layer functions

Recommendation ITU-T G.781

# ITU-T G-SERIES RECOMMENDATIONS

# TRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKS

| INTERNATIONAL TELEPHONE CONNECTIONS AND CIRCUITS                                                                                             | G.100-G.199   |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| GENERAL CHARACTERISTICS COMMON TO ALL ANALOGUE CARRIER-<br>TRANSMISSION SYSTEMS                                                              | G.200–G.299   |

| INDIVIDUAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONE SYSTEMS ON METALLIC LINES                                                      | G.300-G.399   |

| GENERAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONE SYSTEMS ON RADIO-RELAY OR SATELLITE LINKS AND INTERCONNECTION WITH METALLIC LINES | G.400–G.449   |

| COORDINATION OF RADIOTELEPHONY AND LINE TELEPHONY                                                                                            | G.450-G.499   |

| TRANSMISSION MEDIA AND OPTICAL SYSTEMS CHARACTERISTICS                                                                                       | G.600-G.699   |

| DIGITAL TERMINAL EQUIPMENTS                                                                                                                  | G.700-G.799   |

| General                                                                                                                                      | G.700-G.709   |

| Coding of voice and audio signals                                                                                                            | G.710-G.729   |

| Principal characteristics of primary multiplex equipment                                                                                     | G.730-G.739   |

| Principal characteristics of second order multiplex equipment                                                                                | G.740-G.749   |

| Principal characteristics of higher order multiplex equipment                                                                                | G.750-G.759   |

| Principal characteristics of transcoder and digital multiplication equipment                                                                 | G.760-G.769   |

| Operations, administration and maintenance features of transmission equipment                                                                | G.770-G.779   |

| Principal characteristics of multiplexing equipment for the synchronous digital hierarchy                                                    | G.780-G.789   |

| Other terminal equipment                                                                                                                     | G.790-G.799   |

| DIGITAL NETWORKS                                                                                                                             | G.800-G.899   |

| DIGITAL SECTIONS AND DIGITAL LINE SYSTEM                                                                                                     | G.900-G.999   |

| MULTIMEDIA QUALITY OF SERVICE AND PERFORMANCE – GENERIC AND USER-<br>RELATED ASPECTS                                                         | G.1000–G.1999 |

| TRANSMISSION MEDIA CHARACTERISTICS                                                                                                           | G.6000-G.6999 |

| DATA OVER TRANSPORT – GENERIC ASPECTS                                                                                                        | G.7000-G.7999 |

| PACKET OVER TRANSPORT ASPECTS                                                                                                                | G.8000-G.8999 |

| ACCESS NETWORKS                                                                                                                              | G.9000-G.9999 |

|                                                                                                                                              |               |

For further details, please refer to the list of ITU-T Recommendations.

# **Recommendation ITU-T G.781**

# Synchronization layer functions

# **Summary**

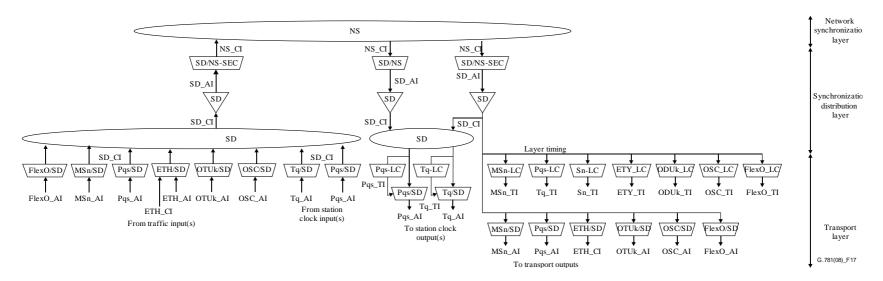

Recommendation ITU-T G.781 defines the atomic functions that are part of the two synchronization layers, the synchronization distribution (SD) layer and the network synchronization (NS) layer. It also defines some atomic functions, part of the transport layer, which are related to synchronization.

These functions describe the synchronization of SDH, Ethernet, and OTN NEs and how these NEs are involved in network synchronization.

The specifications in this Recommendation are the superset of functionality of three regional standards bodies. Care should be taken when selecting from this Recommendation.

Not every atomic function defined in this Recommendation is required for every application. Different subsets of atomic functions may be assembled in different ways according to the combination rules given in Recommendations ITU-T G.783, ITU-T G.705, ITU-T G.8021, ITU-T G.8121 and ITU-T G.798 to provide a variety of different capabilities. Network operators and equipment suppliers may choose which functions must be implemented for each application.

# **History**

| Edition | Recommendation            | Approval   | Study Group | Unique ID*         |

|---------|---------------------------|------------|-------------|--------------------|

| 1.0     | ITU-T G.781               | 1999-07-02 | 15          | 11.1002/1000/4717  |

| 1.1     | ITU-T G.781 (1999) Cor. 1 | 2004-06-13 | 15          | 11.1002/1000/7327  |

| 2.0     | ITU-T G.781               | 2008-09-22 | 15          | 11.1002/1000/9414  |

| 2.1     | ITU-T G.781 (2008) Cor.1  | 2009-11-13 | 15          | 11.1002/1000/10399 |

| 3.0     | ITU-T G.781               | 2017-08-29 | 15          | 11.1002/1000/13299 |

#### **Keywords**

Atomic function, functional model, network synchronization, network synchronization layer, synchronization distribution layer, quality level.

<sup>\*</sup> To access the Recommendation, type the URL http://handle.itu.int/ in the address field of your web browser, followed by the Recommendation's unique ID. For example, <a href="http://handle.itu.int/11.1002/1000/11830-en">http://handle.itu.int/11.1002/1000/11830-en</a>.

#### **FOREWORD**

The International Telecommunication Union (ITU) is the United Nations specialized agency in the field of telecommunications, information and communication technologies (ICTs). The ITU Telecommunication Standardization Sector (ITU-T) is a permanent organ of ITU. ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.

The World Telecommunication Standardization Assembly (WTSA), which meets every four years, establishes the topics for study by the ITU-T study groups which, in turn, produce Recommendations on these topics.

The approval of ITU-T Recommendations is covered by the procedure laid down in WTSA Resolution 1.

In some areas of information technology which fall within ITU-T's purview, the necessary standards are prepared on a collaborative basis with ISO and IEC.

#### **NOTE**

In this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.

Compliance with this Recommendation is voluntary. However, the Recommendation may contain certain mandatory provisions (to ensure, e.g., interoperability or applicability) and compliance with the Recommendation is achieved when all of these mandatory provisions are met. The words "shall" or some other obligatory language such as "must" and the negative equivalents are used to express requirements. The use of such words does not suggest that compliance with the Recommendation is required of any party.

# INTELLECTUAL PROPERTY RIGHTS

ITU draws attention to the possibility that the practice or implementation of this Recommendation may involve the use of a claimed Intellectual Property Right. ITU takes no position concerning the evidence, validity or applicability of claimed Intellectual Property Rights, whether asserted by ITU members or others outside of the Recommendation development process.

As of the date of approval of this Recommendation, ITU had received notice of intellectual property, protected by patents, which may be required to implement this Recommendation. However, implementers are cautioned that this may not represent the latest information and are therefore strongly urged to consult the TSB patent database at <a href="http://www.itu.int/ITU-T/ipr/">http://www.itu.int/ITU-T/ipr/</a>.

#### © ITU 2017

All rights reserved. No part of this publication may be reproduced, by any means whatsoever, without the prior written permission of ITU.

# **Table of Contents**

| Sc  | ope                                                                                      |

|-----|------------------------------------------------------------------------------------------|

| Re  | ferences                                                                                 |

| Te  | rms and definitions                                                                      |

| Al  | obreviations and acronyms                                                                |

| Sy  | nchronization principles                                                                 |

| 5.  | Network synchronization                                                                  |

| 5.2 | Synchronization distribution trails                                                      |

| 5.3 | Synchronization interfaces                                                               |

| 5.4 | Clock-source quality-level                                                               |

| 5.5 | Synchronization status messages (SSMs), extended QL-TLV, and timing marker (TM) channels |

| 5.0 | Selection process                                                                        |

| 5.  | Signal fail                                                                              |

| 5.8 | Hold-off time                                                                            |

| 5.9 | Wait-to-restore time                                                                     |

| 5.  | 0 Synchronization source priorities                                                      |

| 5.  | 1 External commands                                                                      |

| 5.  | 2 Automatic reference selection process                                                  |

| 5.  | 3 Timing loop prevention                                                                 |

| 5.  | 4 Delay times for NEs with SEC/ST3/SIC                                                   |

| 5.  | 5 Delay times for NEs with SSU/ST2 or for SASE/BITS                                      |

| 5.  | 6 Synchronization layer functions                                                        |

| 5.  | 7 Overview of the processes performed within the atomic functions                        |

| 5.  | 8 Interworking between option I, II and III synchronization networks                     |

| Sy  | nchronization distribution layer atomic functions                                        |

| 6.  | SD connection function (SD_C)                                                            |

| 6.2 | SD trail termination functions                                                           |

| 6.3 | SD adaptation functions                                                                  |

| Ne  | etwork synchronization layer atomic functions                                            |

| 7.  | NS_connection functions (NS_C)                                                           |

| Tr  | ansport layer to SD layer atomic functions                                               |

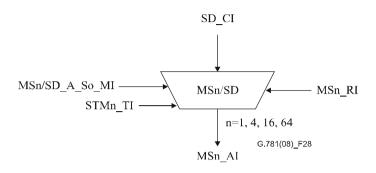

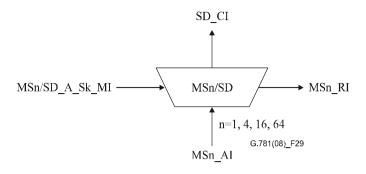

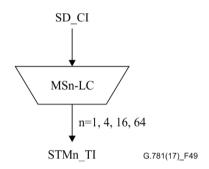

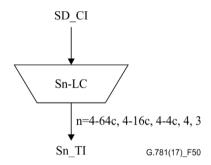

| 8.  | STM-n multiplex section adaptation functions                                             |

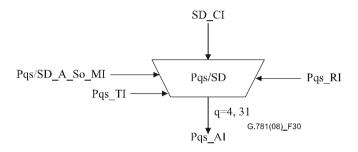

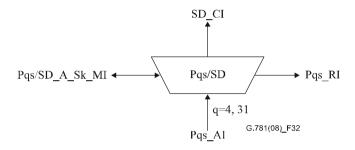

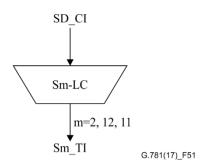

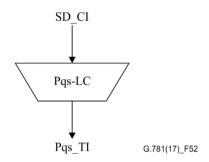

| 8.2 | Pqs adaptation functions                                                                 |

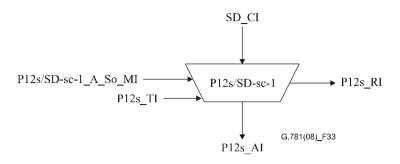

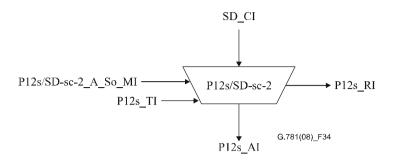

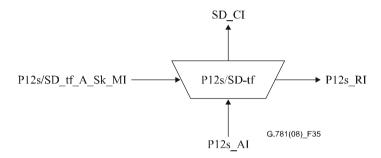

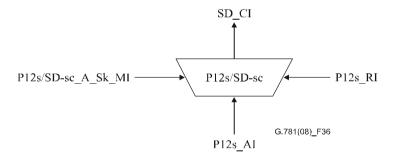

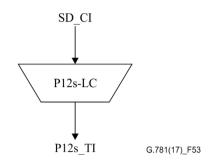

| 8.3 | P12s layer adaptation functions                                                          |

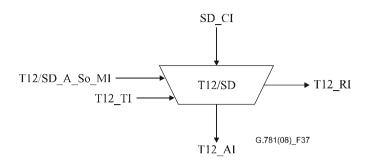

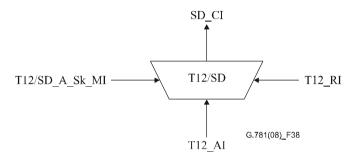

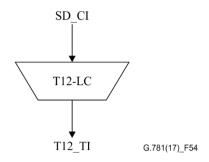

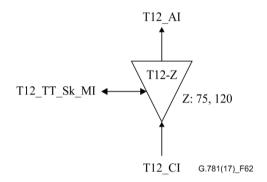

| 8.4 | T12 layer adaptation functions                                                           |

| 8.5 |                                                                                          |

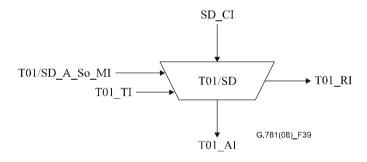

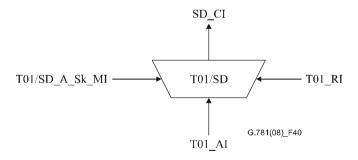

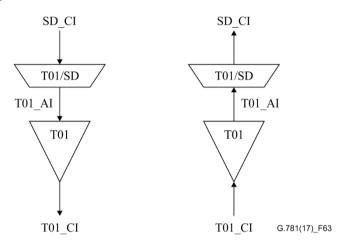

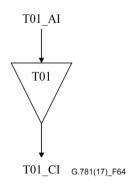

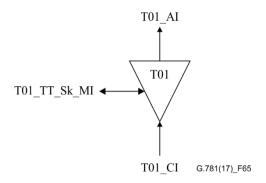

| 8.6 | T01 layer adaptation functions                                                           |

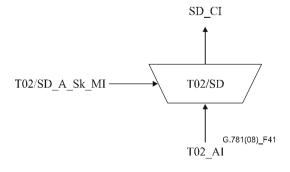

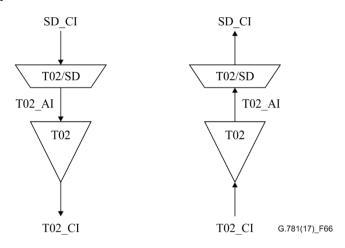

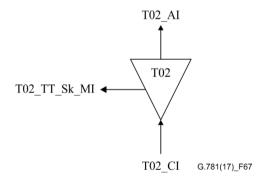

| 8.  | T02 layer adaptation functions                                                           |

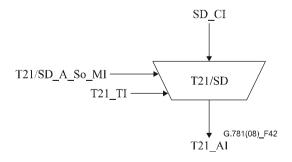

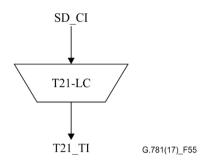

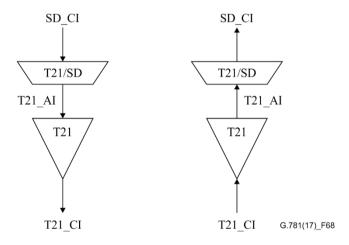

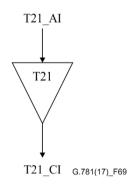

|      | 8.8     | T21 layer adaptation functions                                              |

|------|---------|-----------------------------------------------------------------------------|

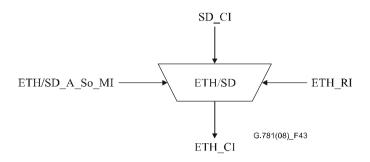

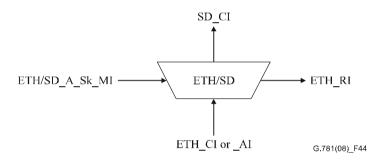

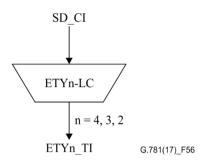

|      | 8.9     | ETH layer adaptation functions                                              |

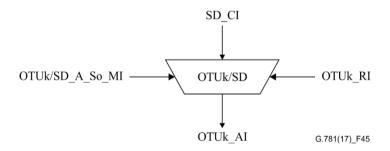

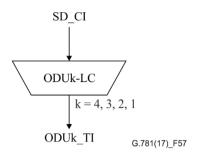

|      | 8.10    | OTUk layer adaptation functions                                             |

|      | 8.11    | OSC                                                                         |

|      | 8.12    | FlexO                                                                       |

| 9    | Equipm  | nent clock to transport layers clock adaptation functions                   |

|      | 9.1     | STM-N layer                                                                 |

|      | 9.2     | VC layers                                                                   |

|      | 9.3     | Pxx layers                                                                  |

|      | 9.4     | T12 layer                                                                   |

|      | 9.5     | T01 layer                                                                   |

|      | 9.6     | T02 layer                                                                   |

|      | 9.7     | T21 layer                                                                   |

|      | 9.8     | ETYn layer                                                                  |

|      | 9.9     | ODU layer                                                                   |

|      | 9.10    | OSC layer                                                                   |

|      | 9.11    | FlexO layer                                                                 |

| 10   | T12 sec | ction layer functions                                                       |

|      | 10.1    | T12 connection function T12_C                                               |

|      | 10.2    | T12 trail termination functions                                             |

| 11   | T01 sec | ction layer functions                                                       |

|      | 11.1    | T01 connection function T01_C                                               |

|      | 11.2    | T01 trail termination functions                                             |

| 12   | T02 sec | ction layer functions                                                       |

|      | 12.1    | T02 connection function T02_C                                               |

|      | 12.2    | T02 trail termination functions                                             |

| 13   |         | ction layer functions                                                       |

|      | 13.1    | T21 connection function T21_C                                               |

|      | 13.2    | T21 trail termination functions                                             |

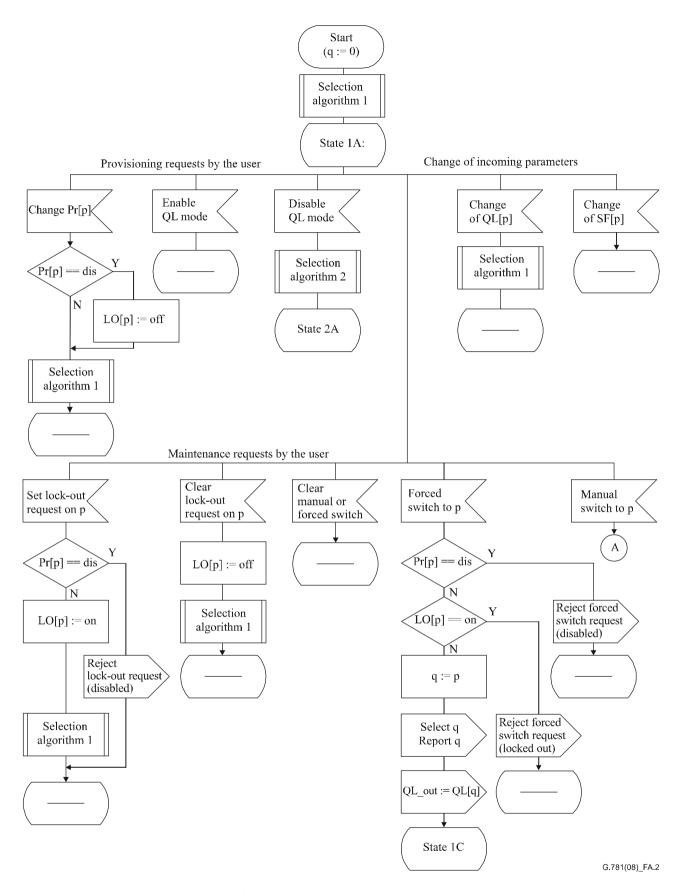

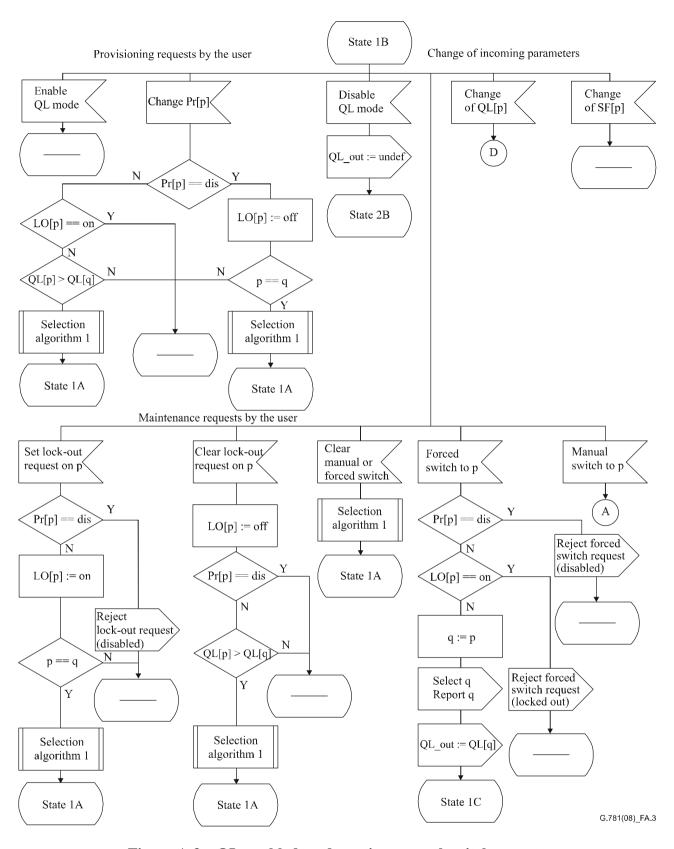

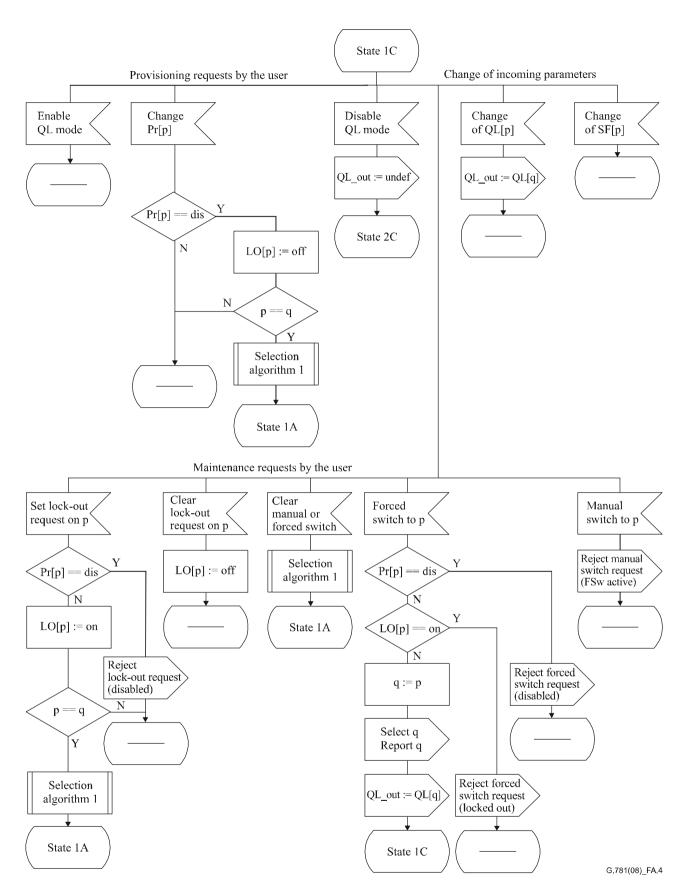

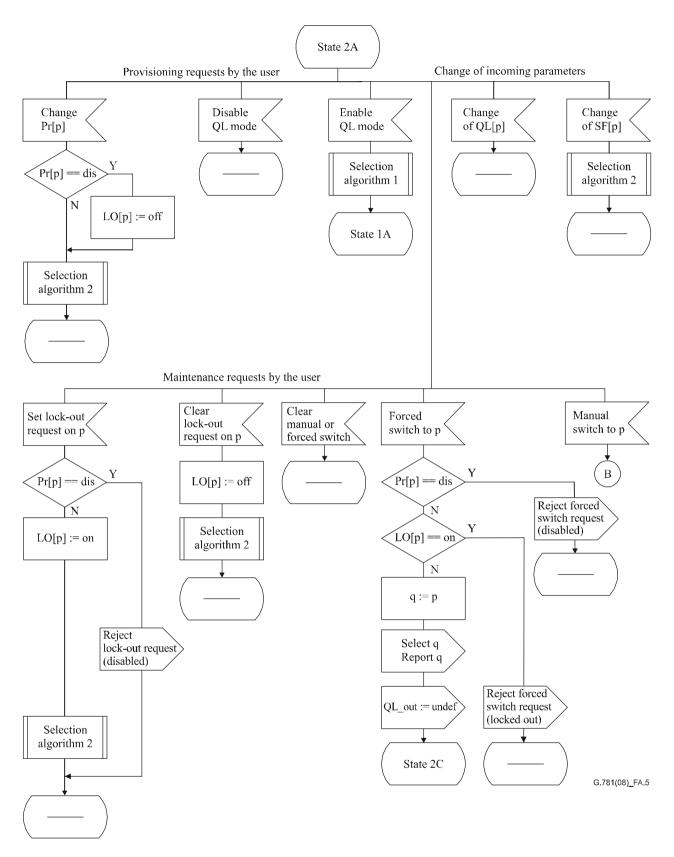

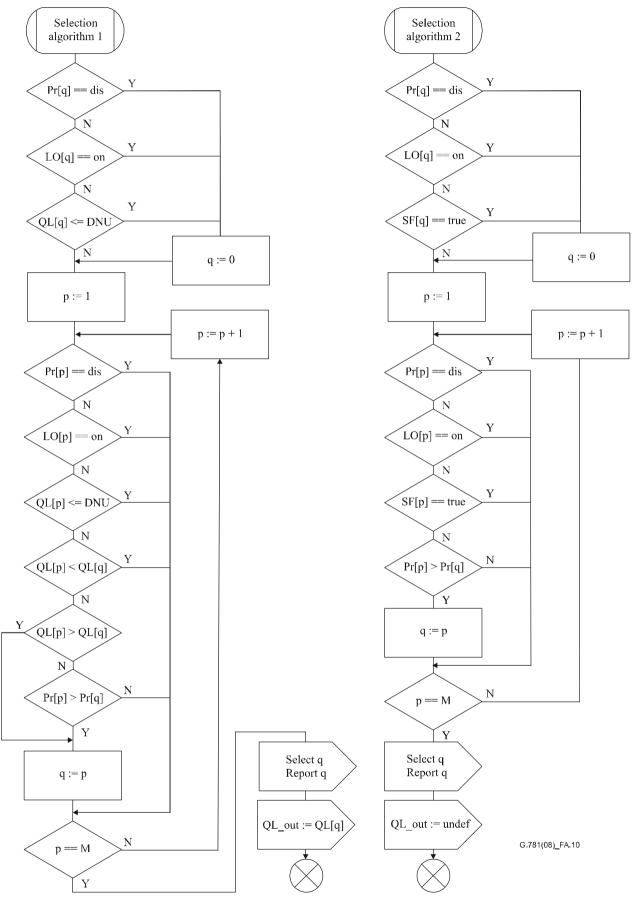

| Anne |         | nchronization selection process                                             |

|      | -       |                                                                             |

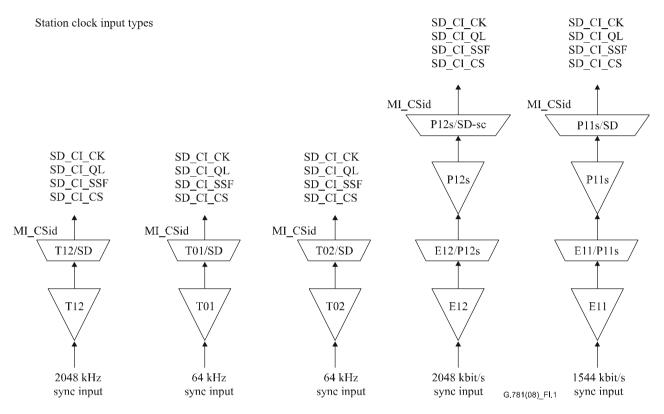

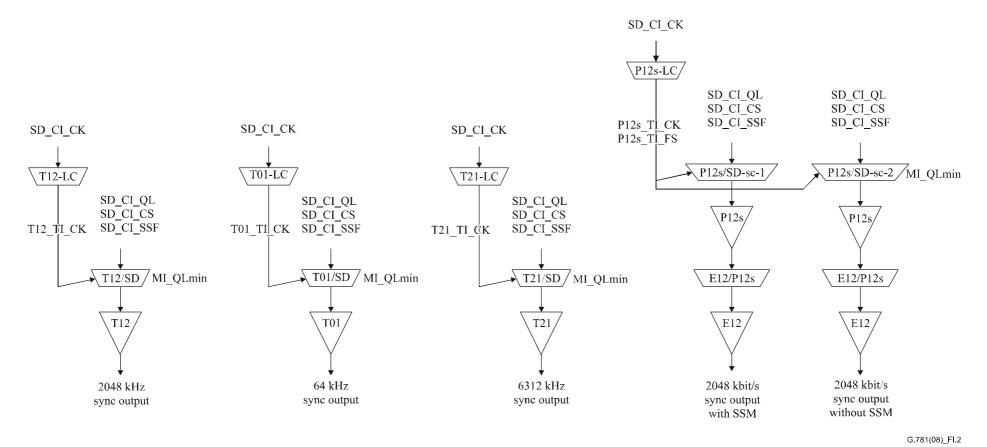

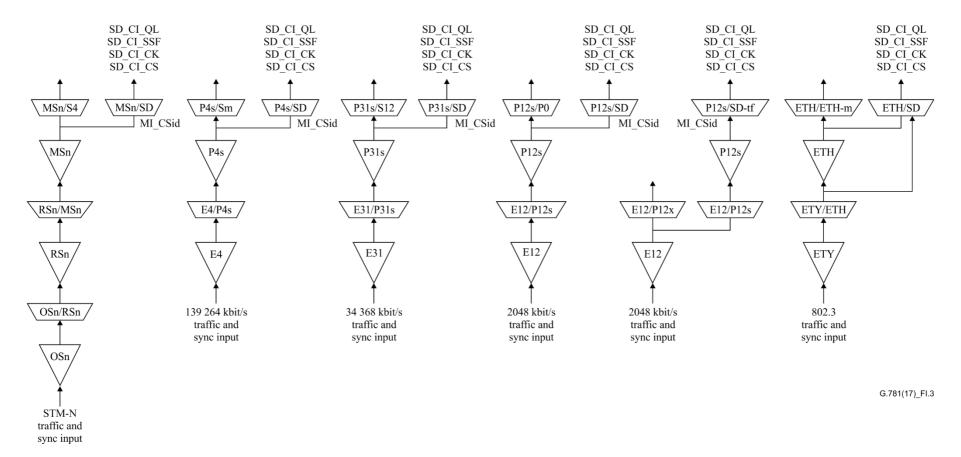

|      |         | Fransport layer models for synchronization information                      |

| Appe |         | Examples of synchronization functionality in the NE                         |

|      | II.1    | Examples of synchronization functionality in the NE for option I networks   |

|      | II.2    | Examples of synchronization functionality in the NE for option II           |

|      |         | networks                                                                    |

|      | II.3    | Examples of synchronization functionality in the NE for option III networks |

|                                                                                                                                          | Page |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| Appendix III – Delay time allocation for option I and III networks                                                                       | 123  |

| III.1 Delay and processing times for the synchronization selection process                                                               | 123  |

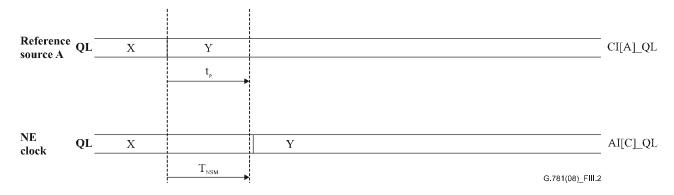

| III.2 Non-switching message delay TNSM                                                                                                   | 123  |

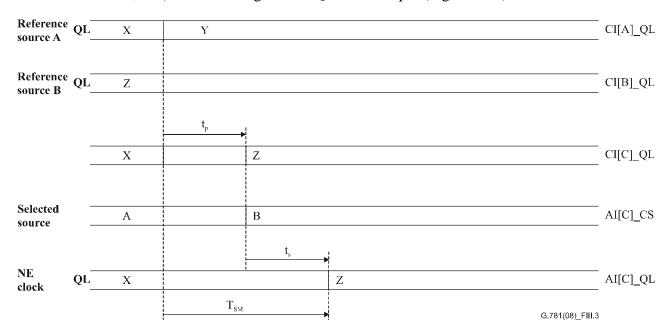

| III.3 Switching message delay TSM                                                                                                        | 124  |

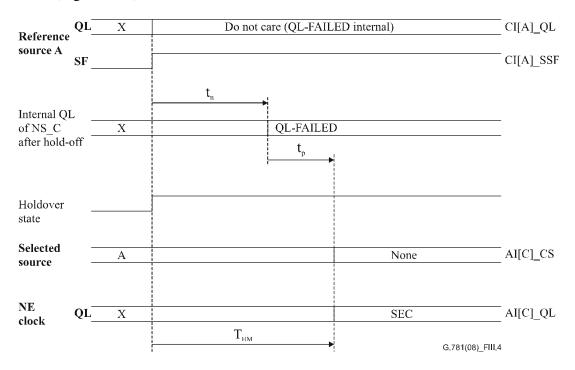

| III.4 Holdover message delay THM                                                                                                         | 125  |

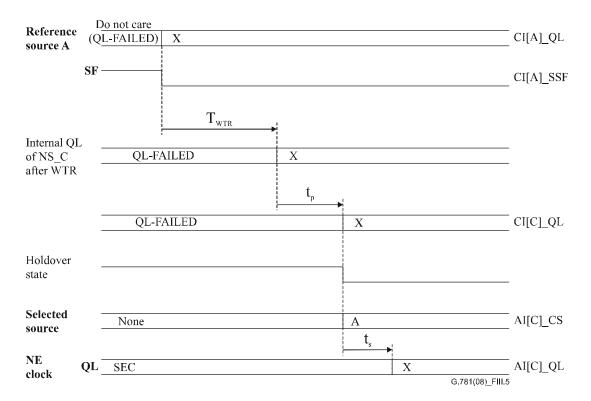

| III.5 Wait-to-restore time TWTR                                                                                                          | 125  |

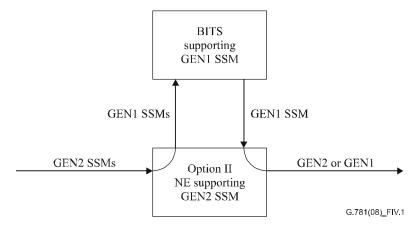

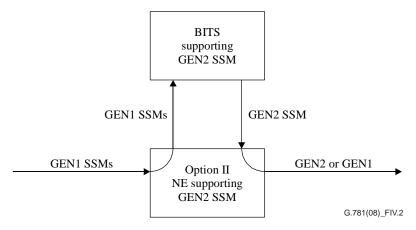

| Appendix IV – Interworking of option II equipment supporting second-generation SSM and first-generation SSM using a translation function | 127  |

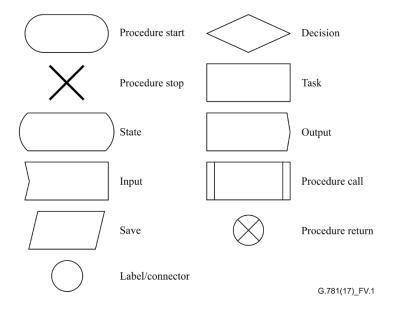

| Appendix V – SDL descriptions                                                                                                            | 129  |

| Appendix VI – Clarification of the use of the acronym 'SEC'                                                                              | 130  |

# **Recommendation ITU-T G.781**

# **Synchronization layer functions**

## 1 Scope

This Recommendation specifies a library of basic synchronization distribution building blocks, referred to as "atomic functions" and a set of rules by which they are combined in order to describe a digital transmission equipment's synchronization functionality. The library defined in this Recommendation forms part of the set of libraries defined furthermore in Recommendations [ITU-T G.783], [ITU-T G.705], [ITU-T G.798], [ITU-T G.8021] and [ITU-T G.8121]. The library comprises the functional building blocks needed to completely specify the generic functional structure of the ITU-T digital transmission hierarchy. Equipment that is compliant with these Recommendations should be describable as an interconnection of a subset of these functional blocks contained within these Recommendations. The interconnection of these blocks should obey the combination rules given in [ITU-T G.806]. The generic functionality is described in [ITU-T G.806].

The specifications in this Recommendation are the superset of functionality of three regional standards bodies. When different processing within a single atomic function is required to support the specific regional processing, this is identified by means of options I, II and III processing. "Option I" applies to networks optimized for the 2048 kbit/s hierarchy. "Option II" applies to networks optimized for the 1544 kbit/s hierarchy that includes the rates 1544 kbit/s, 6312 kbit/s and 44 736 kbit/s. "Option III" applies to networks optimized for the 1544 kbit/s hierarchy that includes the rates 1544 kbit/s, 6312 kbit/s, 33 064 kbit/s, 44 736 kbit/s and 97 728 kbit/s.

As a general rule, this Recommendation does not specify the atomic functions that are specific to PRC ([ITU-T G.811]) and SSU ([ITU-T G.812]) clock equipment; the SSM selection algorithm specified in this Recommendation is only generally applicable to SEC ([ITU-T G.813] and [ITU-T G.8262]) clock equipment. However, strictly for option II networks, there are some specific topologies listed containing both SEC and SSU clock equipment, for which the application of the SSM selection algorithm is described. The general case of using the SSM selection algorithm simultaneously in SSU and SEC clock equipment is for further study for all options.

Full integration of the ePRTC, PRTC, and eEEC is for further study.

# 2 References

The following ITU-T Recommendations and other references contain provisions which, through reference in this text, constitute provisions of this Recommendation. At the time of publication, the editions indicated were valid. All Recommendations and other references are subject to revision; users of this Recommendation are therefore encouraged to investigate the possibility of applying the most recent edition of the Recommendations and other references listed below. A list of the currently valid ITU-T Recommendations is regularly published. The reference to a document within this Recommendation does not give it, as a stand-alone document, the status of a Recommendation.

| Recommendation ITU-T G.703 (2016), Physical/electrical characteristics of |

|---------------------------------------------------------------------------|

| hierarchical digital interfaces.                                          |

| <http: rec="" t-rec-g.703="" www.itu.int=""></http:>                      |

|                                                                           |

[ITU-T G.704] Recommendation ITU-T G.704 (1998), Synchronous frame structures used at 1544, 6312, 2048, 8448 and 44 736 kbit/s hierarchical levels.

<a href="http://www.itu.int/rec/T-REC-G.704">http://www.itu.int/rec/T-REC-G.704</a>

[ITU-T G.705] Recommendation ITU-T G.705 (2000), Characteristics of plesiochronous digital hierarchy (PDH) equipment functional blocks.

<a href="http://www.itu.int/rec/T-REC-G.705">http://www.itu.int/rec/T-REC-G.705</a>

| [110-1 G./06]   | check (CRC) procedures relating to basic frame structures defined in Recommendation G.704. <a href="http://www.itu.int/rec/T-REC-G.706">http://www.itu.int/rec/T-REC-G.706</a>                                                                                           |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ITU-T G.707]   | Recommendation ITU-T G.707/Y.1322 (2007), <i>Network node interface for the synchronous digital hierarchy (SDH)</i> . <a href="http://www.itu.int/rec/T-REC-G.707">http://www.itu.int/rec/T-REC-G.707</a> >                                                              |

| [ITU-T G.709]   | Recommendation G.709/Y.1331 (2016), <i>Interfaces for the optical transport network</i> .                                                                                                                                                                                |

|                 | <http: rec="" t-rec-g.709="" www.itu.int=""></http:>                                                                                                                                                                                                                     |

| [ITU-T G.709.1] | Recommendation G.709.1/Y.1331.1 (2017), <i>Flexible OTN short-reach interface</i> . <a href="http://www.itu.int/rec/T-REC-G.709.1">http://www.itu.int/rec/T-REC-G.709.1</a> >                                                                                            |

| [ITU-T G.775]   | Recommendation ITU-T G.775 (1998), Loss of Signal (LOS), Alarm Indication Signal (AIS) and Remote Defect Indication (RDI) defect detection and clearance criteria for PDH signals. <a href="http://www.itu.int/rec/T-REC-G.775">http://www.itu.int/rec/T-REC-G.775</a> > |

| [ITU-T G.783]   | Recommendation ITU-T G.783 (2006), <i>Characteristics of synchronous digital hierarchy (SDH) equipment functional blocks</i> . <a href="http://www.itu.int/rec/T-REC-G.783">http://www.itu.int/rec/T-REC-G.783</a> >                                                     |

| [ITU-T G.798]   | Recommendation ITU-T G.798 (2012), <i>Characteristics of optical transport network hierarchy equipment functional blocks</i> . <a href="http://www.itu.int/rec/T-REC-G.798">http://www.itu.int/rec/T-REC-G.798</a> >                                                     |

| [ITU-T G.803]   | Recommendation ITU-T G.803 (2000), <i>Architecture of transport networks based on the synchronous digital hierarchy (SDH)</i> . <a href="http://www.itu.int/rec/T-REC-G.803">http://www.itu.int/rec/T-REC-G.803</a> >                                                    |

| [ITU-T G.806]   | Recommendation ITU-T G.806 (2012), <i>Characteristics of transport equipment – Description methodology and generic functionality</i> . <a href="http://www.itu.int/rec/T-REC-G.806">http://www.itu.int/rec/T-REC-G.806</a> >                                             |

| [ITU-T G.810]   | Recommendation ITU-T G.810 (1996), <i>Definitions and terminology for synchronization networks</i> . <a href="http://www.itu.int/rec/T-REC-G.810">http://www.itu.int/rec/T-REC-G.810</a> >                                                                               |

| [ITU-T G.811]   | Recommendation ITU-T G.811 (1997), <i>Timing characteristics of primary reference clocks</i> . <a href="http://www.itu.int/rec/T-REC-G.811">http://www.itu.int/rec/T-REC-G.811</a> >                                                                                     |

| [ITU-T G.812]   | Recommendation ITU-T G.812 (2004), <i>Timing requirements of slave clocks suitable for use as node clocks in synchronization networks</i> . <a href="http://www.itu.int/rec/T-REC-G.812">http://www.itu.int/rec/T-REC-G.812</a> >                                        |

| [ITU-T G.813]   | Recommendation ITU-T G.813 (2003), <i>Timing characteristics of SDH equipment slave clocks (SEC)</i> . <a href="http://www.itu.int/rec/T-REC-G.813">http://www.itu.int/rec/T-REC-G.813</a> >                                                                             |

| [ITU-T G.832]   | Recommendation ITU-T G.832 (1998), <i>Transport of SDH elements on PDH networks: Frame and multiplexing structures</i> . <a href="http://www.itu.int/rec/T-REC-G.832">http://www.itu.int/rec/T-REC-G.832</a> >                                                           |

| [ITU-T G.7041]  | Recommendation ITU-T G.7041/Y.1303 (2016), <i>Generic framing procedure</i> . <a href="http://www.itu.int/rec/T-REC-G.7041">http://www.itu.int/rec/T-REC-G.7041</a> >                                                                                                    |

| [ITU-T G.8021]  | Recommendation ITU-T G.8021/Y.1341 (2016), <i>Characteristics of Ethernet transport network equipment functional blocks</i> . <a href="http://www.itu.int/rec/T-REC-G.8021">http://www.itu.int/rec/T-REC-G.8021</a> >                                                    |

- [ITU-T G.8121] Recommendation ITU-T G.8121/Y.1381 (2016), Characteristics of MPLS-TP equipment functional blocks. <a href="http://www.itu.int/rec/T-REC-G.8121">http://www.itu.int/rec/T-REC-G.8121</a> [ITU-T G.8251] Recommendation ITU-T G.8251 (2010), The control of jitter and wander within the optical transport network (OTN). <http://www.itu.int/rec/T-REC-G.8251> [ITU-T G.8261] Recommendation ITU-T G.8261/Y.1361 (2013), Timing and synchronization aspects in packet networks. <a href="http://www.itu.int/rec/T-REC-G.8261">http://www.itu.int/rec/T-REC-G.8261</a> [ITU-T G.8262] Recommendation ITU-T G.8262/Y.1362 (2015), Timing characteristics of synchronous Ethernet equipment slave clock. <a href="http://www.itu.int/rec/T-REC-G.8262">http://www.itu.int/rec/T-REC-G.8262</a> Recommendation ITU-T G.8264/Y.1364 (2017), Distribution of timing [ITU-T G.8264] information through packet networks. <http://www.itu.int/rec/T-REC-G.8264> [ITU-T G.8272] Recommendation ITU-T G.8272/Y.1367 (2015), Timing characteristics of primary reference time clocks. <http://www.itu.int/rec/T-REC-G.8272> [ITU-T G.8272.1] Recommendation ITU-T G.8272.1 (2016), Timing characteristics of enhanced

- primary reference time clocks.

<a href="http://www.itu.int/rec/T-REC-G.8272.1">http://www.itu.int/rec/T-REC-G.8272.1</a>

- [ITU-T Z.100] Recommendation ITU-T Z.100 (2016), Specification and Description Language Overview of SDL-2010.

<a href="http://www.itu.int/rec/T-REC-Z.100">http://www.itu.int/rec/T-REC-Z.100</a>>

- [IEEE 802.3] IEEE Standard 802.3-2015, IEEE Standard for Ethernet. <a href="http://ieeexplore.ieee.org/document/7428776/">http://ieeexplore.ieee.org/document/7428776/</a>

#### 3 Terms and definitions

This Recommendation defines the following terms:

- **3.1 timing loop**: This is a network condition where a slave clock providing synchronization becomes locked to its own timing signal. It is generally created when the slave clock timing information is looped back to its own input, either directly or via other network equipments. Timing loops should be prevented in networks by careful network design.

- **3.2 QL\_minimum**: QL\_minimum is a configurable parameter used in the squelching of clock output signals. If the quality level of the signal used to derive the output falls below QL\_minimum then the output will be squelched (cut-off or set to AIS).

- **3.3 clock-source quality-level**: The clock-source quality-level of an SEC or SASE is defined as the grade of clock to which it is ultimately traceable, i.e., the grade of clock to which it is synchronized directly or indirectly via a chain of SECs and SASEs, however long this chain of clocks is. For example, the clock-source quality-level may be a primary reference clock complying with [ITU-T G.811], or it may be a slave clock in holdover-mode, complying with [ITU-T G.812], or a [ITU-T G.813] or [ITU-T G.8262] clock in holdover or freerun.

The clock-source quality-level is essentially, therefore, an indication only of the long-term accuracy of the NE clock.

**3.4 station clock**: This is a node clock as defined in [ITU-T G.810].

The functional definitions are given in [ITU-T G.783].

The symbols and diagrammatic conventions are given in [ITU-T G.783].

- **3.5 squelch**: An action that cuts off (i.e., shuts down) an output signal. For some signals (e.g., 2 Mbit/s), squelching may be realized by means of inserting AIS instead of shutting down the signal.

- **3.6 synchronous equipment clock**: A generic term representing the SDH equipment clock ([ITU-T G.813]), the Ethernet equipment clock (EEC) ([ITU-T G.8262]), and the OTN equipment clock (OEC, for further study).

# 4 Abbreviations and acronyms

This Recommendation uses the following abbreviations and acronyms:

AI Adapted Information

AIS Alarm Indication Signal

AP Access Point

BITS Building Integrated Timing Supply

CI Characteristic Information

CK Clock signal (timing information)

CLR Clear

CP Connection Point

CS Clock Source (timing information)

CSid Clock Source identifier

DL Data Link

DNU Do Not Use

DUS Do not Use for Sync

ES1 Electrical Section, level 1

ESF Extended SuperFrame

ESMC Ethernet Synchronization Messaging Channel

EEC Ethernet Equipment Clock

EXTCMD EXTernal COMmand messaging channel

FS Frame Start (timing information)

FSw Forced Switch

HO Hold-Off time

HO HoldOver mode

ID IDentifier

INVx INValid x

LC Layer Clock

LO Locked mode

LO LockOut

LOS Loss Of Signal

LSB Least Significant Bit

LTI Loss of Timing Information

MA Maintenance and Adaptation

MFP MultiFrame Present

MFS MultiFrame Start

MI Management Information

MON Monitored

MS Multiplex Section

MSB Most Significant Bit

MSw Manual Switch

MTIE Maximum Time Interval Error

NE Network Element

NS Network Synchronization

NSUPP Not SUPPorted

OSn Optical Section layer (STM-n)

P12s 2048 kbit/s PDH path layer with synchronous 125 µs frame structure according to

[ITU-T G.704]

P31s 34 368 kbit/s PDH path layer with synchronous 125 µs frame structure according to

[ITU-T G.832]

P4s 139 264 kbit/s PDH path layer with synchronous 125 µs frame structure according to

[ITU-T G.832]

PDH Plesiochronous Digital Hierarchy

PRC Primary Reference Clock

PRS Primary Reference Source

QL Quality Level

RES REServed for network synchronization use

RI Remote Information

RSn Regenerator Section layer STM-n

SASE Stand Alone Synchronization Equipment

SD Synchronization Distribution

SDH Synchronous Digital Hierarchy

SDL Specification and Description Language

SEC Synchronous Equipment Clock

SF Signal Fail

Sk Sink

SMC SONET Minimum Clock

So Source SQLCH Squelch SSF Server Signal Fail

SSM Synchronization Status Message

SSU Synchronization Supply Unit

SSU-A primary level SSU

SSU-B secondary level SSU

ST2 STratum 2

ST3 STratum 3

ST3E STratum 3 Enhanced

ST4 STratum 4

STM-N Synchronous Transport Module, level N

STU Synchronization Traceability Unknown

TCP Termination Connection Point

TDEV Time DEViation

TI Timing Information

TL Transport Layer

TM Timing Marker

TNC Transit Node Clock

TSF Trail Signal Fail

TT Trail Termination

UNC UNConnected

UNK UNKnown

VC-n Virtual Container, level n

WTR Wait-To-Restore

# **5** Synchronization principles

# 5.1 Network synchronization

Synchronization network architecture is specified in [ITU-T G.803].

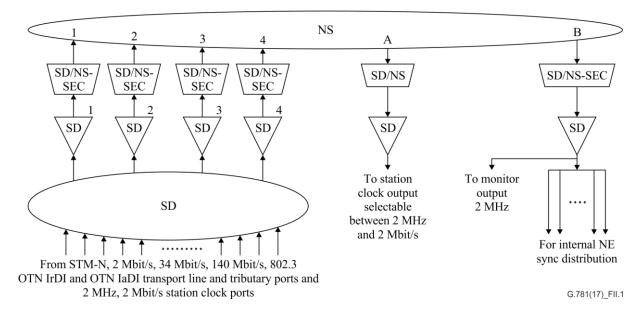

Synchronization information is transmitted through the network via synchronization network connections. These synchronization network connections can transport different synchronization levels. Each synchronization network connection is provided by one or more synchronization link connection(s), each supported by a synchronized PDH trail, SDH multiplex section trail, OTN OTU trail, OTN OSC trail, or IEEE 802.3 physical media trail.

Some of these synchronized PDH trail, SDH multiplex section trail, OTN OTU trail, OTN OSC trail, or IEEE 802.3 physical media trail signals contain a communication channel, the synchronization status message (SSM), the timing marker (TM), the OTN synchronization message channel (OSMC), or the ethernet synchronization message channel (ESMC) transporting a quality-level identifier. This quality-level identifier can be used to select the highest synchronization level incoming reference signal from a set of nominated synchronization references available at the network element.

Synchronization network connections are unidirectional and generally point-to-multipoint. [ITU-T G.803] specifies a master-slave synchronization technique for synchronizing SDH and OTN

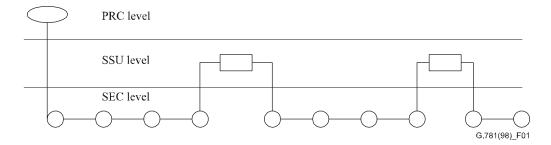

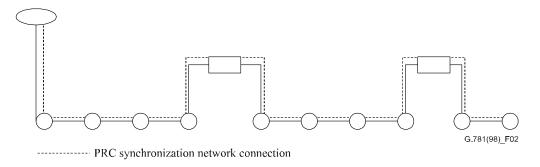

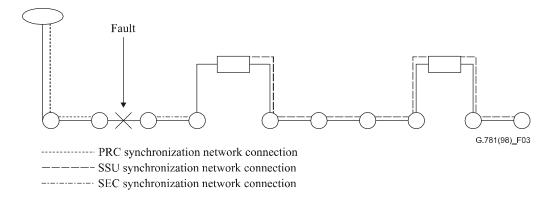

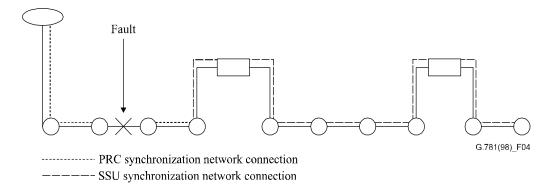

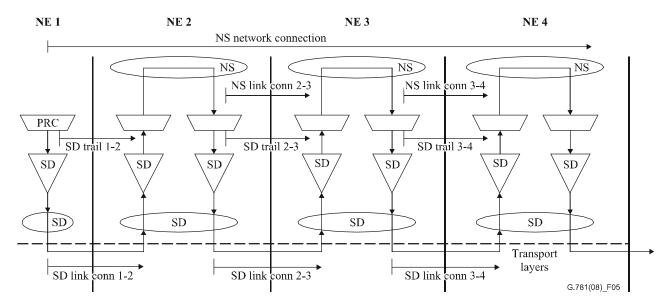

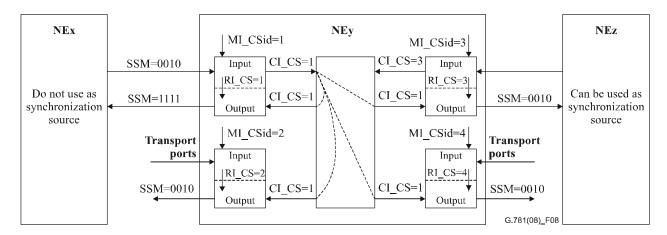

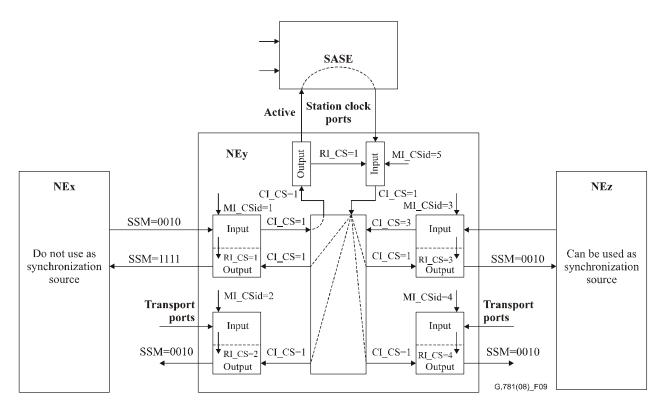

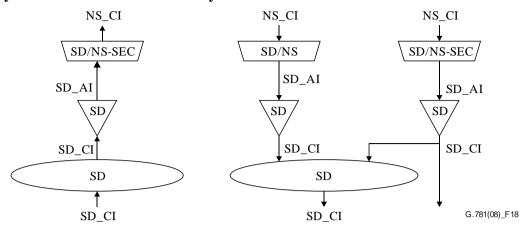

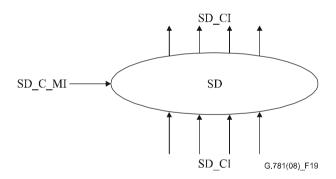

networks and [ITU-T G.8261] specifies it for packet transport networks. Figures 1 to 4 illustrate the synchronization network connection model.

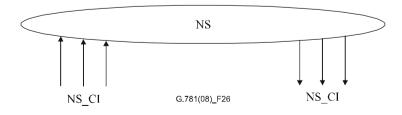

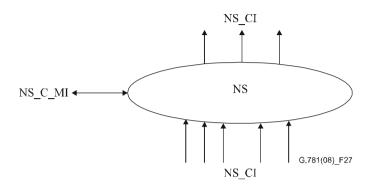

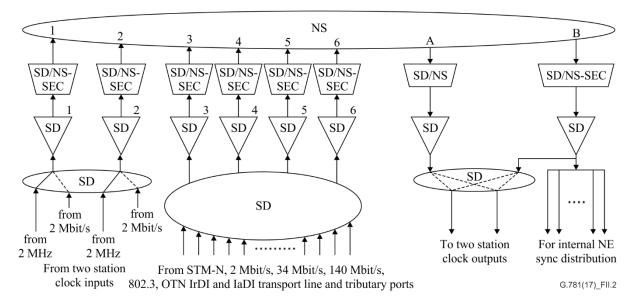

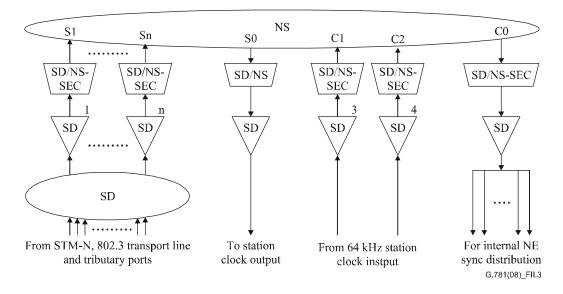

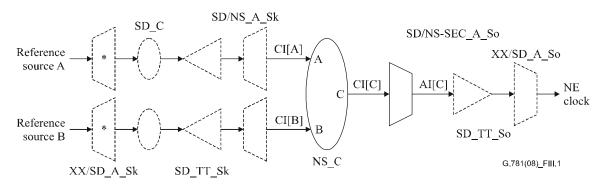

Figure 1 – General representation of a synchronization network

Figure 2 – Representation of the PRC network connection

Figure 3 – Representation of the synchronization network connection in case of failure

Figure 4 – Example of restoration of the synchronization

# 5.2 Synchronization distribution trails

Synchronization distribution trails transport timing between two adjacent equipments.

From a synchronization view point, adjacent network elements are those network elements that are interconnected via section signals. Between two such adjacent network elements (NEs), a unidirectional synchronization distribution trail exists.

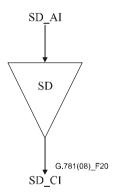

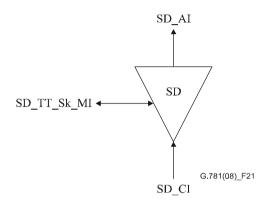

An **SD trail** starts at the input of the SD\_TT\_So function and ends at the output of the SD\_TT\_Sk function.

An **SD** link connection transports synchronization timing information between two adjacent connection points (CPs) of the NS\_C function.

An **NS** network connection transports synchronization timing information over a series of synchronization link connection (see Figure 5).

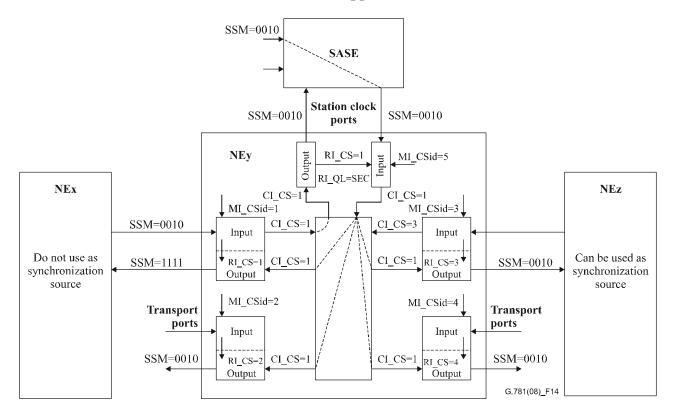

Figure 5 – Example of series of synchronization distribution network connection transporting PRC quality timing reference information

# **5.3** Synchronization interfaces

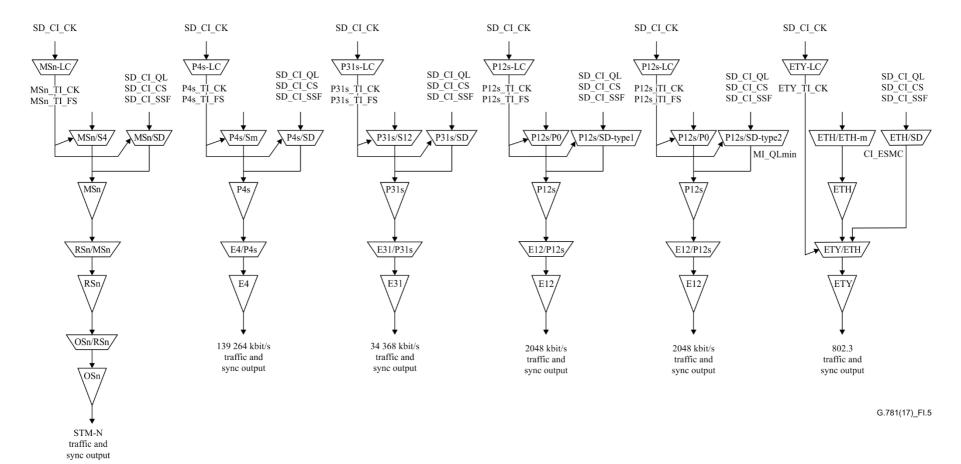

Synchronization trails can be carried through the network by a number of interfaces. Currently, the following signals are defined for such transport (refer also to Figures I.1 to I.4):

## 5.3.1 Overview

# 5.3.1.1 Option I synchronization networking

- Without traffic:

- 2048 kHz (T12);

- 2048 kbit/s (E12+P12s).

- With traffic:

- 9 953 280 kbit/s (OS64+RS64+MS64);

- 2 488 320 kbit/s (OS16+RS16+MS16);

- 622 080 kbit/s (OS4+RS4+MS4);

- 155 520 kbit/s (OS1 (or ES1)+RS1+MS1);

- 139 264 kbit/s (E4+P4s);

- 34 368 kbit/s (E31+P31s);

- 2048 kbit/s (E12+P12s);

- 100 000 kbit/s (ETY2[+ETH]);

- 1 000 000 kbit/s (ETY3[+ETH]);

- 10 000 000 kbit/s (ETY4[+ETH]);

- 40 000 000 kbit/s (ETY5[+ETH]);

- 100 000 000 kbit/s (ETY6[+ETH]);

- 255/238 x 2 488 320 kbit/s (OPSn+OChr+OTU1+ODU1);

- 255/237 x 9 953 280 kbit/s (OPSn+OChr+OTU2+ODU2);

- 255/236 x 39 813 120 kbit/s (OPSn+OChr+OTU3+ODU3):

- 255/227 x 99 532 800 kbit/s (OPSM44+OTU4+ODU4);

- X kbit/s (OSC).

NOTE – The ETYn synchronization interfaces are full duplex ones with continuous bit stream, as specified in [ITU-T G.8262].

# 5.3.1.2 Option II synchronization networking

- Without traffic:

- 64 kHz (T01);

- 1544 kbit/s (E11+P11s).

- With traffic:

- 9 953 280 kbit/s (OS64+RS64+MS64);

- 2 488 320 kbit/s (OS16+RS16+MS16);

- 622 080 kbit/s (OS4+RS4+MS4);

- 155 520 kbit/s (OS1 (or ES1)+RS1+MS1);

- 1544 kbit/s (E11+P11s);

- 100 000 kbit/s (ETY2[+ETH]);

- 1 000 000 kbit/s (ETY3[+ETH]);

- 10 000 000 kbit/s (ETY4[+ETH]);

- 40 000 000 kbit/s (ETY5[+ETH]);

- 100 000 000 kbit/s (ETY6[+ETH]);

- 255/238 x 2 488 320 kbit/s (OPSn+OChr+OTU1+ODU1);

- 255/237 x 9 953 280 kbit/s (OPSn+OChr+OTU2+ODU2);

- 255/236 x 39 813 120 kbit/s (OPSn+OChr+OTU3+ODU3);

- 255/227 x 99 532 800 kbit/s (OPSM44+OTU4+ODU4);

- X kbit/s (OSC).

NOTE – The ETYn synchronization interfaces are full duplex ones with continuous bit stream, as specified in [ITU-T G.8262].

# 5.3.1.3 Option III synchronization networking

- Without traffic:

- 64 kHz (T02) [from SASE/BITS to NE];

- 6312 kHz (T21) [from NE to SASE/BITS].

- With traffic:

- 9 953 280 kbit/s (OS64+RS64+MS64);

- 2 488 320 kbit/s (OS16+RS16+MS16);

- 622 080 kbit/s (OS4+RS4+MS4);

- 155 520 kbit/s (OS1 (or ES1)+RS1+MS1);

- 100 000 kbit/s (ETY2[+ETH]);

- 1 000 000 kbit/s (ETY3[+ETH]);

- 10 000 000 kbit/s (ETY4[+ETH]);

- 40 000 000 kbit/s (ETY5[+ETH]);

- 100 000 000 kbit/s (ETY6[+ETH]);

- 255/238 x 2 488 320 kbit/s (OPSn+OChr+OTU1+ODU1);

- 255/237 x 9 953 280 kbit/s (OPSn+OChr+OTU2+ODU2);

- 255/236 x 39 813 120 kbit/s (OPSn+OChr+OTU3+ODU3);

- 255/227 x 99 532 800 kbit/s (OPSM44+OTU4+ODU4);

- X kbit/s (OSC).

NOTE – The ETYn synchronization interfaces are full duplex ones with continuous bit stream, as specified in [ITU-T G.8262].

#### 5.3.2 STM-N

The STM-N transport signals carry (in addition to the payload) reference timing information and an indication of the quality level of the source generating this timing information, via the synchronization status message (SSM) as defined in [ITU-T G.707].

NOTE – Old equipment may not be able to support SSM via their STM-N interfaces.

#### 5.3.3 2 Mbit/s

The 2 Mbit/s transport signals may carry (in addition to the payload) reference timing information.

The 2 Mbit/s timing reference signals (without payload) carry reference timing information to specific synchronization ports.

Both signals can carry an indication of the quality level of the source generating the timing information via the SSM as specified in [ITU-T G.704].

NOTE 1 – Old equipment may not be able to support SSM on their 2 Mbit/s interfaces.

NOTE 2 – The 2 Mbit/s timing reference signal can be connected to either a SASE/BITS or another NE. The SSM specifications in this version of this Recommendation include the interconnect between two NEs. The SSM processing with respect to the interface between NE and SASE is for further study.

#### 5.3.4 2 MHz

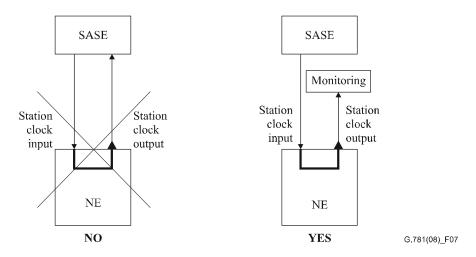

Synchronization can be carried through 2 MHz signals to specific synchronization ports (so-called station clock ports). This signal does not carry an indication of the quality level of the source generating the timing information.

NOTE – The 2 MHz timing reference signal can be connected to either a SASE/BITS or another NE.

# 5.3.5 34 Mbit/s and 140 Mbit/s with 125 µs frame structure

34 Mbit/s and 140 Mbit/s signals with 125  $\mu$ s frame structure as defined in [ITU-T G.832] carry a full 4-bit SSM code.

NOTE – For interworking with equipments compliant with the initial edition of [ITU-T G.832], new equipments should be able to be configured to recognize and generate the timing marker which is located in bit 8 of the MA (maintenance and adaptation) byte: the timing marker is set to "0" to indicate that the timing source is traceable to a primary reference clock (PRC), and is otherwise set to "1".

#### 5.3.6 1.5 Mbit/s

The 1.5 Mbit/s transport signals may carry (in addition to the payload) reference timing information.

The 1.5 Mbit/s timing reference signals (without payload) carry reference timing information to specific synchronization ports.

Both signals can carry an indication of the quality level of the source generating the timing information via the SSM transported within the 1544 kbit/s signal's extended super frame (ESF) data link (DL) as specified in [ITU-T G.704].

NOTE 1 – The format of the data link messages in ESF frame format is "0xxx xxx0 1111 1111", transmitted right-most bit first. The 6 bits denoted "xxx xxx" contain the actual message; some of these messages are reserved for synchronization messaging. It takes 32 frames (i.e., 4 ms) to transmit all 16 bits of a complete DL word. Note that [ITU-T G.704] presents the data link messages in reverse order "1111 1111 0xxx xxx0".

NOTE 2 – Old equipment may not be able to support SSM on their 1.5 Mbit/s interfaces.

#### 5.3.7 64 kHz

Within option II networks, synchronization can be carried through 64 kHz (T01) interface signals (see clause 4.2.2 of [ITU-T G.703] composite timing signal) to specific synchronization input ports (so-called station clock ports). This signal does not carry an indication of the quality level of the source generating the timing information.

Within option III networks, synchronization can be carried through 64 kHz (T02) interface signals (see Appendix II of [ITU-T G.703] composite timing signal) from the SASE to specific synchronization input ports (so-called station clock ports) on an NE. This signal does not carry an indication of the quality level of the source generating the timing information.

#### 5.3.8 6312 kHz

Within option III networks, synchronization can be carried through 6312 kHz signals (see Appendix II of [ITU-T G.703]) from specific synchronization output ports (so-called station clock ports) on an NE to inputs of the SASE. This signal does not carry an indication of the quality level of the source generating the timing information.

#### 5.3.9 100 Mbit/s, 1 Gbit/s, 10 Gbit/s, 40 Gbit/s, 100 Gbit/s

The IEEE 802.3 transport signals may carry (in addition to the payload) reference timing information, and an indication of the quality level of the source generating this timing information, via the synchronization status message (SSM) and the extended QL-TLV, as defined in [ITU-T G.8264].

NOTE – It is possible that equipment is equipped with both non-synchronous and synchronous IEEE 802.3 interfaces as defined in [ITU-T G.8264]. Non-synchronous IEEE 802.3 interfaces are excluded from the synchronization distribution process.

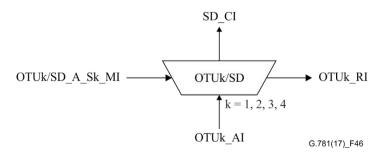

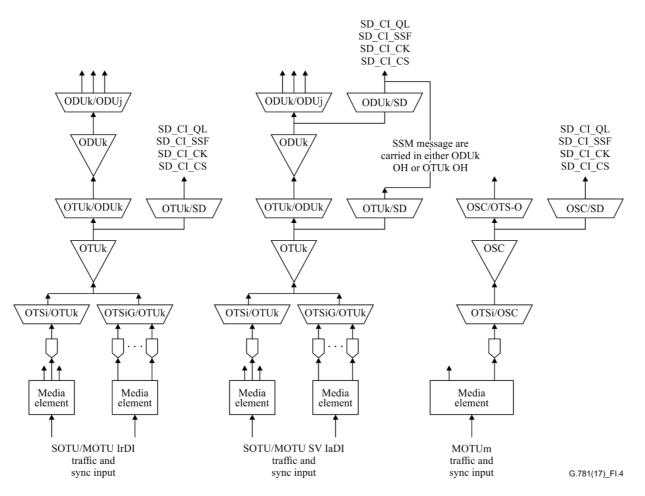

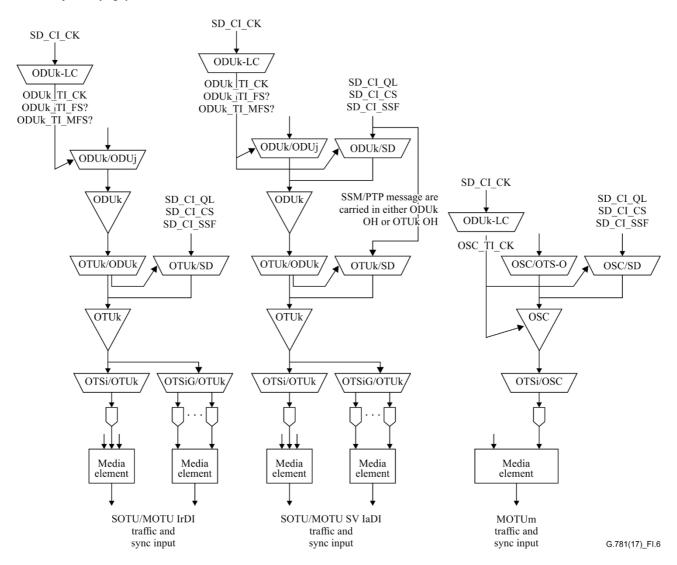

#### 5.3.10 Single OTU (SOTU) and Multi OTU (MOTU) interfaces

The SOTU and MOTU interface signals may carry (in addition to the payload) reference timing information in the OTUk (k = 1, 2, 3, 4) and FlexO, and an indication of the quality level of the source generating this timing information, via the synchronization status message (SSM) and, optionally, the extended QL-TLV, as defined in [ITU-T G.709] and [ITU-T G.8264].

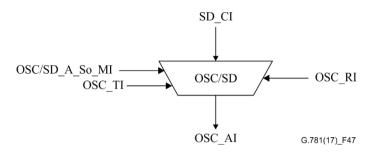

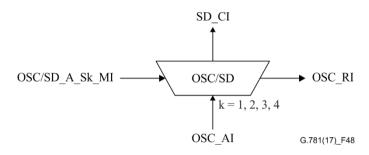

# 5.3.11 Multi OTU with management (MOTUm) interfaces

The MOTUm interface signals may carry (in addition to the payload):

- a) reference timing information in the optical supervisory channel (OSC) signal in case of an MOTUm interface, and

- b) an indication of the quality level of the source generating this timing information, via the synchronization status message (SSM) and, optionally, the extended QL-TLV, as defined in [ITU-T G.709] and [ITU-T G.8264].

NOTE 1 – In cases where the OCh goes through a ROADM, the OTUk within the OCh cannot be used to carry time synchronization because, due to optical switching or cross-connecting, its latency cannot be controlled (and could produce delay asymmetry, which could result in time synchronization error). However, the OSC is

terminated at every optical node (including OAs and ROADMs), so this is not an issue for the OSC. Note also that, in principle, delay asymmetry is not an issue for frequency synchronization; however, it is unlikely that one would want a link that is suitable for carrying frequency synchronization but not time synchronization.

NOTE 2 – Equipment developed prior to Edition 3.0 of this Recommendation may not be able to carry reference timing information and/or support SSM or extended QL-TLV via an OTUk signal in its SOTU and MOTU interfaces or via an OSC signal in its MOTUm interfaces.

NOTE 3 – It is possible that equipment is equipped with both non-synchronous and synchronous SOTU, MOTU and/or MOTUm intra-domain interfaces. Non-synchronous SOTU, MOTU and MOTUm intra-domain interfaces are excluded from the synchronization distribution process.

# 5.4 Clock-source quality-level

# **5.4.1** Clock-source quality-level definitions

SDH and packet transport networks throughout the world are based on different synchronization philosophies. Those differences are identified in this Recommendation as three options: I, II and III.

# **5.4.1.1** Option I synchronization networking

The following clock-source quality-levels are defined in the synchronization process of option I networks.

QL-ePRTC: This synchronization trail transports a timing quality generated by an enhanced

primary reference time clock, which is defined in [ITU-T G.8272.1].

QL-PRTC: This synchronization trail transports a timing quality generated by a primary

reference time clock, which is defined in [ITU-T G.8272].

QL-PRC: This synchronization trail transports a timing quality generated by a primary

reference clock, which is defined in [ITU-T G.811].

QL-SSU-A: This synchronization trail transports a timing quality generated by a type I or V slave

clock, which is defined in [ITU-T G.812].

QL-SSU-B: This synchronization trail transports a timing quality generated by a type VI slave

clock, which is defined in [ITU-T G.812].

QL-eEEC: This synchronization trail transports a timing quality generated by an enhanced EEC.

QL-SEC: This synchronization trail transports a timing quality generated by a synchronous

equipment clock (SEC), which is defined in [ITU-T G.813] or [ITU-T G.8262],

option I.

QL-DNU: This signal should not be used for synchronization.

NOTE – The "unknown" quality level was defined to characterize the quality of an existing network. This QL is no longer supported by the SSM algorithm in option I networks. Instead, a synchronization reference input port which receives a signal without SSM can be provisioned to assume a quality level for that received signal (see clause 5.4.3).

# 5.4.1.2 Option II synchronization networking

The following clock-source quality-levels are defined in the synchronization selection process of an option II network.

QL-ePRTC: This synchronization trail transports a timing quality generated by an enhanced

primary reference time clock, which is defined in [ITU-T G.8272.1].

QL-PRTC: This synchronization trail transports a timing quality generated by a primary

reference time clock, which is defined in [ITU-T G.8272].

QL-PRS: PRS traceable ([ITU-T G.811]).

QL-STU: Synchronized – Traceability unknown.

QL-ST2: Traceable to stratum 2 ([ITU-T G.812], type II).

QL-TNC: Traceable to transit node clock ([ITU-T G.812], type V).

QL-ST3E: Traceable to stratum 3E ([ITU-T G.812], type III).

QL-ST3: Traceable to stratum 3 ([ITU-T G.812], type IV or [ITU-T G.8262], option II).

QL-SMC: Traceable to SONET clock self timed ([ITU-T G.813]).

QL-ST4: Traceable to stratum 4 free run (only applicable to 1.5 Mbit/s signals).

QL-PROV: Provisionable by the network operator.

QL-DUS: This signal should not be used for synchronization.

First-generation quality levels do not define QL-ST3E and QL-TNC as separate quality levels and QL-PROV was identified as QL-RES.

# 5.4.1.3 Option III synchronization networking

The following clock-source quality-levels are defined in the synchronization process of an option III SDH network.

QL-ePRTC: This synchronization trail transports a timing quality generated by an enhanced primary reference time clock, which is defined in [ITU-T G.8272.1].

QL-PRTC: This synchronization trail transports a timing quality generated by a primary reference time clock, which is defined in [ITU-T G.8272].

QL-UNK: This synchronization trail transports a timing quality generated by an unknown clock source. It is at least of quality SSU.

QL-eEEC: This synchronization trail transports a timing quality generated by an enhanced EEC.

QL-SEC: This synchronization trail transports a timing quality generated by a synchronous equipment clock (SEC), which is defined in [ITU-T G.813] or [ITU-T G.8262], option I.

NOTE – The use of other quality levels is for further study.

#### 5.4.1.4 Squelching

The first purpose of the "squelch" function is to prevent transmission of a timing signal with a quality that is lower than the quality of the clock in the receiving network element or SASE. It is also used for the prevention of timing loops (see clause 5.13).

# 5.4.2 Hierarchy of clock-source quality-levels (QL) or (CS\_QL)

The following tables define the QL hierarchy.

## 5.4.2.1 Option I synchronization networking

Table 1 – Hierarchy of quality levels in option I synchronization networks

| Quality level                        | Order   |

|--------------------------------------|---------|

| QL-ePRTC                             | Highest |

| QL-PRTC                              |         |

| QL-PRC                               |         |

| QL-SSU-A                             |         |

| QL-SSU-B                             |         |

| QL-eEEC                              |         |

| QL-SEC                               |         |

| QL-DNU                               |         |

| QL-INVx, QL-FAILED, QL-UNC, QL-NSUPP | Lowest  |

The quality levels QL-INVx, QL-FAILED, QL-UNC and QL-NSUPP are internal QLs inside the NE and are never generated at an output port.

QL-INVx is generated by the XX/SD\_A\_Sk function if an unallocated SSM value is received, where x represents the binary value of this SSM.

QL-NSUPP is generated by the XX/SD\_A\_Sk function when the function is not supporting the SSM (TM) processing.

QL-FAILED is generated by the SD\_TT\_Sk function when the terminated SD trail is in the signal fail state.

QL-UNC is generated by the SD\_C or NS\_C function when the output signal is not connected to an input, but instead to the internal unconnected signal generator.

# 5.4.2.2 Option II synchronization networking

Table 2 – Hierarchy of quality levels in option II synchronization networks

| Quality level                        | Order   |

|--------------------------------------|---------|

| QL-ePRTC                             | Highest |

| QL-PRTC                              |         |

| QL-PRS                               |         |

| QL-STU                               |         |

| QL-ST2                               |         |

| QL-TNC (Note)                        |         |

| QL-ST3E (Note)                       |         |

| QL-ST3                               |         |

| QL-SMC                               |         |

| QL-ST4                               |         |

| QL-PROV (default position)           |         |

| QL-DUS                               | l       |

| QL-INVx, QL-FAILED, QL-UNC, QL-NSUPP | Lowest  |

| NOTE 1 OF THE 1 OF THE 1             |         |

NOTE 1 – QL-TNC and QL-ST3E are not defined for first-generation synchronization networking (refer to clause 5.4.1.2) and QL-PROV was identified as QL-RES. NOTE 2 – The addition of QL-eEEC, for the enhanced EEC, is for further study.

The quality levels QL-INVx, QL-FAILED, QL-UNC and QL-NSUPP are internal QLs inside the NE and are never generated at an output port.

QL-INVx is generated by the XX/SD\_A\_Sk function if an unallocated SSM value is received, where x represents the binary value of this SSM.

QL-NSUPP is generated by the XX/SD\_A\_Sk function when the function is not supporting the SSM (TM) processing.

QL-FAILED is generated by the SD\_TT\_Sk function when the terminated SD trail is in the signal fail state.

QL-UNC is generated by the SD\_C or NS\_C function when the output signal is not connected to an input, but instead to the internal unconnected signal generator.

The quality level QL-PROV is provisionable by the network operator and may take different order positions. The default position for QL-PROV is as shown in Table 2.

# 5.4.2.3 Option III synchronization networking

Table 3 – Hierarchy of quality levels in option III synchronization networks

| Quality level                        | Order   |

|--------------------------------------|---------|

| QL-ePRTC                             | Highest |

| QL-PRTC                              |         |

| QL-UNK                               |         |

| QL-eEEC                              |         |

| QL-SEC                               |         |

| QL-INVx, QL-FAILED, QL-UNC, QL-NSUPP | Lowest  |

The quality levels QL-INVx, QL-FAILED, QL-UNC and QL-NSUPP are internal QLs inside the NE and are never generated at an output port.

QL-INVx is generated by the XX/SD\_A\_Sk function if an unallocated SSM value is received, where x represents the binary value of this SSM.

QL-NSUPP is generated by the XX/SD\_A\_Sk function when the function is not supporting the SSM (TM) processing.

QL-FAILED is generated by the SD\_TT\_Sk function when the terminated SD trail is in the signal fail state.

QL-UNC is generated by the SD\_C or NS\_C function when the output signal is not connected to an input, but instead to the internal unconnected signal generator.

#### 5.4.3 Forcing and defaulting of clock-source quality-levels

For synchronization source signals/interfaces not supporting SSM transport/processing, it is possible in option I networks to force the quality level to a fixed provisioned value. This allows using these signals/interfaces as synchronization sources in an automatic reference selection process operating in OL-enabled mode.

Forcing of quality levels is used for new equipment operating in QL-enabled mode in order to:

- interwork with old equipment not supporting SSM/TM generation;

- interwork with new equipment operating in QL-disabled mode;

- select interfaces not supporting SSM/TM processing;

- select signals for which SSM/TM is not defined (e.g., 2 MHz).

In option II and III networks, synchronization input ports assume a default QL-STU/QL-UNK for synchronization source signals not supporting SSM.

#### **5.4.3.1** Option I synchronization networking

The quality level of the input signal (STM-N, 2 Mbit/s, 2 MHz, 34 Mbit/s, 140 Mbit/s) can be forced to either QL-PRC, QL-SSU-A, QL-SSU-B or QL-SEC.

# 5.4.3.2 Option II synchronization networking

QL-STU is the default quality level for signals from equipment not supporting or not enabled for SSM in option II.

NOTE – 1544 kbit/s signals transport the SSM as a specific message within the data link (see [ITU-T G.704]). When a timing input port does not receive any SSM message, it defaults to QL-STU.

## 5.4.3.3 Option III synchronization networking

QL-UNK is the default quality level for 64 kHz station clock input signals.

# 5.4.4 Application of quality level "Unknown"

# 5.4.4.1 Option I synchronization networking

Option I synchronization networks do not support the unknown quality level. Instead, the network operator is required to force the quality level to one of the four quality levels: PRC, SSU-A, SSU-B or SEC. Engineering rules for this selection are for further study.

NOTE 1 – Equipment built according to the initial STM-N signal specification in which the S1 byte was still a Z1 byte with no defined value, may output any of the 16 codes within what is now bits 5 to 8 of byte S1.

NOTE 2 – Engineering rules for the forcing of quality levels in option I networks could be the following: if the reference signal is sourced by an SASE or NE with SSU-A clock, the forced QL should be QL-SSU-A; if the reference signal is sourced by an NE with SSU-B clock, the forced QL should be QL-SSU-B; if the reference signal is sourced by an NE with a SEC clock, the forced QL should be QL-SEC.

# 5.4.4.2 Option II synchronization networking

Quality level "unknown" (QL-STU) is intended to be used in option II applications where SSM functionality is not supported by all synchronization equipment. Without SSM capabilities, it is impossible for synchronization equipment to communicate its quality level. Consequently, the QL-STU message is used in applications where equipment with SSM functionality is timed from a reference without an SSM. The QL-STU message indicates that the equipment is locked to a reference (i.e., it is not in holdover) but the quality of the source is not known.

Typically, this QL-STU quality level is assumed to apply to signals at an NE's station clock input port (connected to a BITS). 1.5 Mbit/s signals into the clock input ports default to STU if SSMs are not supported by the BITS. STM-N signals into the NE contain SSM code "0000" and are interpreted as QL-STU if SSMs are not supported by the STM-N output port in the previous NE.

When the input signal with forced QL-STU is selected as the synchronization reference, the output signals supporting SSM will indicate QL-STU in their SSM bits. Network elements supporting SSM processing will accept incoming QL-STU indications as one of the normal quality-level indications.

The clock-source quality-level of a signal with QL-STU indication is assumed to be equal or less than PRS and better than or equal to ST2 (clause 5.4.2).

# 5.4.4.3 Option III synchronization networking

In the case of option III applications, an NE's clock is usually locked to an ePRTC, PRTC, or SSU clock. Consequently, the quality level of the NE's clock signal is usually better than or equal to SSU. However, if there is an eEEC or SEC, which can enter holdover or free-run mode while part of a synchronization network connection, it is necessary to ensure the clock quality.

The quality level "unknown" (QL-UNK) message indicates that the equipment is locked to a reference (i.e., it is not in holdover) but the quality of the source is not known. Typically, this QL-UNK quality level is assumed to apply to 64 kHz signals at an NE's station clock input port (connected to an SASE). The quality of the source will then be at least SSU.

When the input signal with QL-UNK is selected as synchronization reference, the output signals supporting SSM will indicate QL-UNK in their SSM bits. Network elements supporting SSM processing will accept incoming QL-UNK indications as one of the normal quality-level indications. The clock-source quality-level of a signal with QL-UNK indication is assumed to be equal or less than PRC and better than or equal to SSU.

If the clock-source quality-level is lower than QL-UNK at the clock input port of the NE in the upper synchronization layer, quality level "synchronous equipment clock" (QL-SEC) or quality level "enhanced Ethernet equipment clock" (QL-eEEC) shall be transmitted from an NE in the upper

synchronization layer to an NE in the lower synchronization layer. When the NE in the lower synchronization layer receives the QL-SEC or QL-eEEC, the NE in the lower synchronization layer squelches the output to the SSU to avoid the clock quality level degradation in other lower synchronization layers. The clock-source quality-level of a signal with QL-SEC or QL-eEEC indication means that its quality level is lower than SSU.

NOTE – Engineering rules for the forcing of quality levels in option III networks are for further study.

# 5.4.5 Application of quality level "provisioned"

The quality level QL-PROV defined for option II networks is provisionable to a QL order chosen by the operator.

# 5.5 Synchronization status messages (SSMs), extended QL-TLV, and timing marker (TM) channels

The following signals have a four-bit SSM channel defined:

- STM-N (N = 1, 4, 16): bits 5 to 8 of the byte S1 (called SSMB, synchronization status message byte) of the multiplex section overhead as defined in [ITU-T G.707].

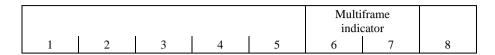

- 2 Mbit/s octet structured according to [ITU-T G.704]: bits  $S_{ax1}$  to  $S_{ax4}$  (x = 4, 5, 6, 7 or 8) of TS0.

- 1.5 Mbit/s octet structured according to clause 2.1 of [ITU-T G.704].

- 34 Mbit/s as defined in [ITU-T G.832]: bit 8 of MA byte with a 4-frame multiframe.

- 140 Mbit/s as defined in [ITU-T G.832]: bit 8 of MA byte with a 4-frame multiframe.

- 100 Mbit/s, 1 Gbit/s, 10 Gbit/s, 40 Gbit/s, and 100 Gbit/s, as defined in [IEEE 802.3]: 4-bit SSM field in the SSM PDU (i.e., the ESMC) as defined in [ITU-T G.8264].

The following signals may have a one bit TM channel:

- 34 Mbit/s with a 125 μs frame structure as defined in [ITU-T G.832]: bit 8 of byte MA.

- 140 Mbit/s with a 125 μs frame structure as defined in [ITU-T G.832]: bit 8 of byte MA.

The following signals have a packet-based SSM channel:

- 100 Mbit/s, 1 Gbit/s, 10 Gbit/s, 40 Gbit/s, and 100 Gbit/s Ethernet as defined in [ITU-T G.8262]: Ethernet Synchronization Message Channel (ESMC) [ITU-T G.8264]

- OTN OTUk, k=1,2,3,4 defined in [ITU-T G.709]: OTN Synchronization Message Channel (OSMC) [ITU-T G.709]

- OTN OSC as defined in [ITU-T G.709]: OTN Synchronization Message Channel (OSMC) [ITU-T G.709]

- FlexO as defined in [ITU-T G.709.1]: OTN Synchronization Message Channel (OSMC)

[ITU-T G.709.1]

The following signals have an optional extended QL-TLV, as defined in [ITU-T G.8264]:

- 100 Mbit/s, 1 Gbit/s, 10 Gbit/s, 40 Gbit/s, and 100 Gbit/s Ethernet as defined in [ITU-T G.8262]

- OTN OTUk, k=1,2,3,4 defined in [ITU-T G.709]

- OTN OSC as defined in [ITU-T G.709]

- FlexO as defined in [ITU-T G.709.1]

# 5.5.1 SSM and TM message sets

NOTE – The extended ESMC, and enhanced SSM codes, are specified in [ITU-T G.8264].

## 5.5.1.1 Option I synchronization networking

Five SSM codes are defined to represent clock-source QL as listed below:

- code 0010 (quality PRC) means that the source of the trail is a PRC clock ([ITU-T G.811]);

- code 0100 (quality SSU-A), means that the source of the trail is a type I or V SSU clock [ITU-T G.812];

- code 1000 (quality SSU-B), means that the source of the trail is a type VI SSU clock ([ITU-T G.812]);

- code 1011 (quality SEC), means that the source of the trail is an SEC clock ([ITU-T G.813] or [ITU-T G.8262], option I);

- code 1111 (quality DNU), means that the signal carrying this SSM shall not be used for synchronization because a timing loop situation could result if it is used.

Two TM codes are defined in [ITU-T G.832]:

- code 0 (quality PRC), means that the source of the trail is a PRC clock ([ITU-T G.811]);

- code 1 (quality less than PRC), means that the source of the trail is not a PRC clock.

#### 5.5.1.2 Option II synchronization networking

Nine SSM codes are defined to represent clock-source QL as listed below on STM-N signals:

- code 0001 (quality PRS) means that the source of the trail is a PRS clock ([ITU-T G.811]);

- code 0000 (quality STU) means that the signal does not carry the QL message of the source of the trail;

- code 0111 (quality ST2), means that the source of the trail is a stratum 2 clock ([ITU-T G.812], type II);

- code 0100 (quality TNC), means that the source of the trail is a transit node clock ([ITU-T G.812], type V);

- code 1101 (quality ST3E), means that the source of the trail is a stratum 3E clock ([ITU-T G.812], type III);

- code 1010 (quality ST3), means that the source of the trail is a stratum 3 clock ([ITU-T G.812], type IV or [ITU-T G.8262], option II);

- code 1100 (quality SMC), means that the source of the trail is a SONET self-timed clock ([ITU-T G.813]);

- code 1110 (quality PROV), is provisionable by the network operator;

- code 1111 (quality DUS), means that the signal carrying this SSM shall not be used for synchronization because a timing loop situation could result if it is used.

NOTE 1 – Code 1101 and code 0100 are not recognized by equipment supporting only first-generation SSM and are treated as invalid (see clause 5.4.1.2), code 1110 is identified as QL-RES.

Ten SSM codes are defined to represent clock-source QL as listed below on 1544 kbit/s signals:

- code 04FF<sub>H</sub> (quality PRS) means that the source of the trail is a PRS clock ([ITU-T G.811]);

- code 08FF<sub>H</sub> (quality unknown) means that the source of the trail is unknown;

- code 0CFF<sub>H</sub> (quality ST2) means that the source of the trail is a stratum 2 clock ([ITU-T G.812], type II);

- code  $78FF_H$  (quality TNC) means that the source of the trail is a transit node clock ([ITU-T G.812], type V);

- code 7CFF $_{\rm H}$  (quality ST3E) means that the source of the trail is a stratum 3E clock ([ITU-T G.812, type III);

- code  $10FF_H$  (quality ST3) means that the source of the trail is a stratum 3 clock ([ITU-T G.812, type IV);

- code 22FF<sub>H</sub> (quality SMC) means that the source of the trail is a SONET/Ethernet self-timed clock ([ITU-T G.813] or [ITU-T G.8262], option II);

- code 28FF<sub>H</sub> (quality ST4) means that the source of the trail is a stratum 4 clock;

- code 40FF<sub>H</sub> (quality PROV) is provisionable by the network operator;

- code 30FF<sub>H</sub> (quality DUS) means that the signal carrying this SSM shall not be used for synchronization because a timing loop situation could result if it is used.

NOTE 2 – Code 78FF<sub>H</sub> and code 7CFF<sub>H</sub> are not recognized by equipment supporting only second-generation SSM and are treated as invalid (refer to clause 5.4.1.2), code 40FF<sub>H</sub> is identified as QL-RES.

# 5.5.1.3 Option III synchronization networking

Two SSM codes are defined to represent clock-source QL as listed below:

- code 0000 (quality unknown) means that the source of the trail is unknown;

- code 1011 (quality SEC) means that the source of the trail is an SEC clock ([ITU-T G.813] or [ITU-T G.8262], option I).

# 5.5.2 SSM and TM code word generation

The SSM can be viewed as an application-specific data communication channel with a limited message set. The message that shall be generated and inserted depends on the applied quality-level indication that is input to the adaptation source function. The following tables present the relation between the existing set of QLs and SSM codes for the three options.

It is possible to disable the SSM generation and insert "1111". An application for this could be, e.g., at network boundaries where timing information should not be forwarded to the other network.

# 5.5.2.1 Option I synchronization networking

Table 4 – Quality level set and coding in synchronization status message in option I synchronization networks

| Quality level (QL) | SSM usage | SSM coding [MSBLSB] |

|--------------------|-----------|---------------------|

| QL-PRC             | Enabled   | 0010                |

| QL-SSU-A           | Enabled   | 0100                |

| QL-SSU-B           | Enabled   | 1000                |

| QL-SEC             | Enabled   | 1011                |

| QL-DNU             | Enabled   | 1111                |

| _                  | Disabled  | 1111                |

The TM can be viewed as an application-specific data communication channel with a limited message set. The message that shall be generated and inserted depends on the applied quality level indication that is input to the adaptation source function. The following table presents the relation between the existing set of QLs and TM codes.

Table 5 – Quality level set and coding in timing marker in option I synchronization networks

| Quality Level (QL) | TM usage | TM coding |

|--------------------|----------|-----------|

| QL-PRC             | Enabled  | 0         |

| QL-SSU-A           | Enabled  | 1         |

| QL-SSU-B           | Enabled  | 1         |

| QL-SEC             | Enabled  | 1         |

| QL-DNU             | Enabled  | 1         |

| _                  | Disabled | 1         |

At network boundaries, it should be possible to prevent synchronization information passing the interface. This can be achieved by disabling the SSM (TM) usage.

# 5.5.2.2 Option II synchronization networking

In order to provide stable interoperability between equipment supporting first generation and equipment supporting second-generation quality levels, Table 6 defines the SSM coding for both "second-generation output connected to a second-generation input", and for "second-generation output connected to first-generation input".

This translation table is for newer equipment supporting second-generation quality-level definitions only. Message translation is provided on a per port basis as a provisionable option. This allows for equipment supporting second-generation messaging to simultaneously pass valid SSMs to both second-generation and first-generation equipment.

The shaded fields in Table 6 identify the quality levels that require translation in order to be understood by first-generation equipment: QL-TNC and QL-ST3E are translated into QL-ST3 messages, QL-PROV SSM code is interpreted as QL-RES by first-generation equipment.

Table 6 – Quality level set and coding in synchronization status message in option II synchronization networks

| Quality<br>level (QL) | SSM<br>usage | Second-generation SSM                                 |                                                                      | First-genei                                           | ration SSM                                                           |

|-----------------------|--------------|-------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------|

|                       |              | SSM coding<br>[MSBLSB]<br>in STM-N signal<br>(BINARY) | SSM coding<br>[MSBLSB]<br>in 1544 kbit/s<br>signal with ESF<br>(HEX) | SSM coding<br>[MSBLSB]<br>in STM-N signal<br>(BINARY) | SSM coding<br>[MSBLSB]<br>in 1544 kbit/s<br>signal with ESF<br>(HEX) |

| QL-PRS                | Enabled      | 0001                                                  | 04FF                                                                 | 0001                                                  | 04FF                                                                 |

| QL-STU                | Enabled      | 0000                                                  | 08FF                                                                 | 0000                                                  | 08FF                                                                 |

| QL-ST2                | Enabled      | 0111                                                  | 0CFF                                                                 | 0111                                                  | 0CFF                                                                 |

| QL-TNC                | Enabled      | 0100                                                  | 78FF                                                                 | 1010 <sup>c)</sup>                                    | 10FF <sup>c)</sup>                                                   |

| QL-ST3E               | Enabled      | 1101                                                  | 7CFF                                                                 | 1010 <sup>c)</sup>                                    | 10FF <sup>c)</sup>                                                   |

| QL-ST3                | Enabled      | 1010                                                  | 10FF                                                                 | 1010                                                  | 10FF                                                                 |

| QL-SMC                | Enabled      | 1100                                                  | 22FF                                                                 | 1100                                                  | 22FF                                                                 |

| QL-ST4                | Enabled      | _                                                     | 28FF                                                                 | _                                                     | 28FF                                                                 |

| QL-PROV               | Enabled      | 1110                                                  | 40FF                                                                 | 1110 <sup>a), b), c)</sup>                            | 40FF <sup>a), b), c)</sup>                                           |

| QL-DUS                | Enabled      | 1111                                                  | 30FF                                                                 | 1111                                                  | 30FF                                                                 |

Table 6 – Quality level set and coding in synchronization status message in option II synchronization networks

| Quality<br>level (QL) | SSM<br>usage | Second-generation SSM                                 |                                                                      | First-generation SSM                                  |                                                                      |

|-----------------------|--------------|-------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------|

|                       |              | SSM coding<br>[MSBLSB]<br>in STM-N signal<br>(BINARY) | SSM coding<br>[MSBLSB]<br>in 1544 kbit/s<br>signal with ESF<br>(HEX) | SSM coding<br>[MSBLSB]<br>in STM-N signal<br>(BINARY) | SSM coding<br>[MSBLSB]<br>in 1544 kbit/s<br>signal with ESF<br>(HEX) |

| _                     | Disabled     | 1111                                                  | 08FF                                                                 | 1111                                                  | 08FF                                                                 |

a) The assignment of the GEN1 message "reserved for network synchronization use (QL-RES)" needs to be done on a network-wide basis.

At network boundaries, it shall be possible to prevent synchronization information passing the interface. This can be achieved by disabling the SSM usage, or by provisioning output signals to have QL-STU or QL-DUS.

The application of the QL-PROV message is at the discretion of the network operator.

## 5.5.2.3 Option III synchronization networking

Table 7 – Quality level set and coding in synchronization status message in option III synchronization networks

| Quality level (QL) | SSM coding [MSBLSB] |

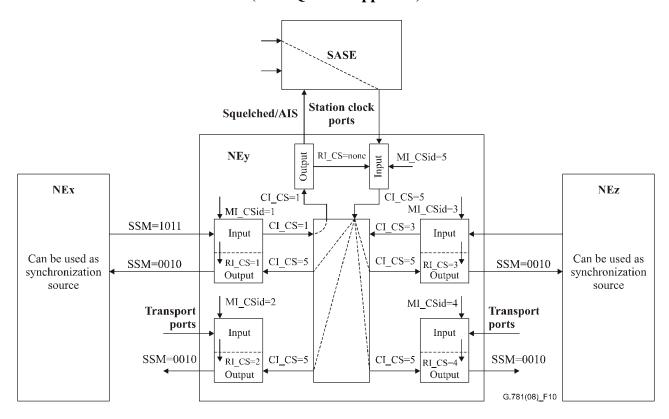

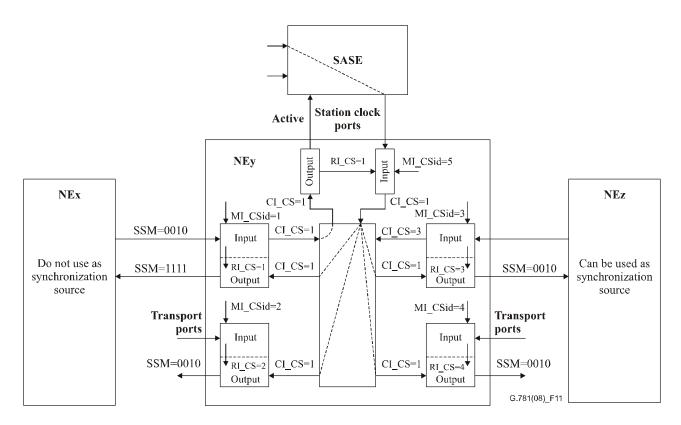

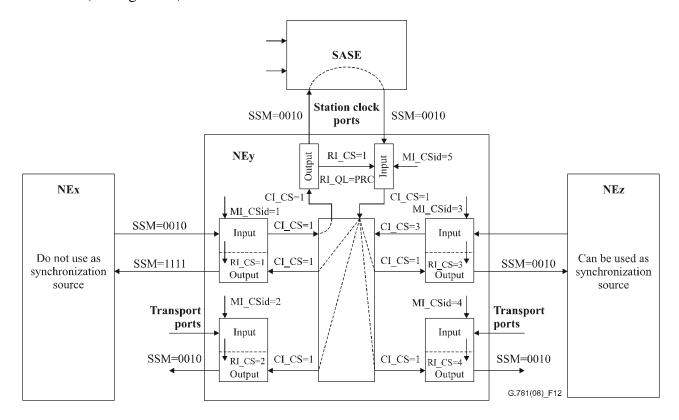

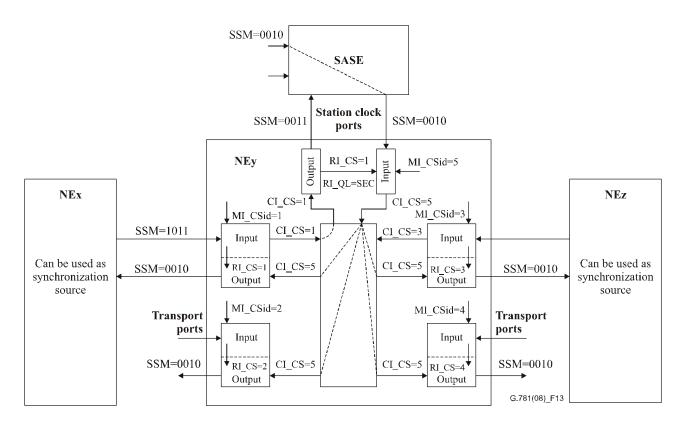

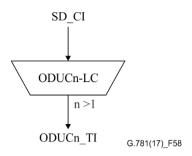

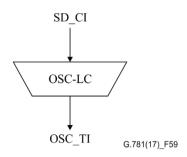

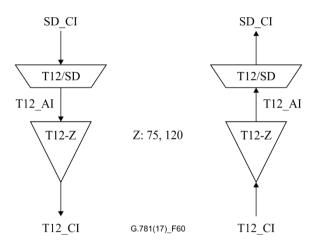

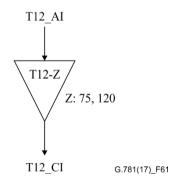

|--------------------|---------------------|