ITU-T

G.707/Y.1322

(10/2000)

TELECOMMUNICATION STANDARDIZATION SECTOR OF ITU

SERIES G: TRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKS

Digital terminal equipments – General

SERIES Y: GLOBAL INFORMATION INFRASTRUCTURE AND INTERNET PROTOCOL ASPECTS

Internet protocol aspects - Transport

Network node interface for the synchronous digital hierarchy (SDH)

ITU-T Recommendation G.707/Y.1322

(Formerly CCITT Recommendation)

### ITU-T G-SERIES RECOMMENDATIONS

# TRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKS

| INTERNATIONAL TELEPHONE CONNECTIONS AND CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | G.100–G.199                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| GENERAL CHARACTERISTICS COMMON TO ALL ANALOGUE CARRIER-<br>TRANSMISSION SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                         | G.200–G.299                                                                                                          |

| INDIVIDUAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONE SYSTEMS ON METALLIC LINES                                                                                                                                                                                                                                                                                                                                                                                                                                 | G.300-G.399                                                                                                          |

| GENERAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONE<br>SYSTEMS ON RADIO-RELAY OR SATELLITE LINKS AND INTERCONNECTION WITH<br>METALLIC LINES                                                                                                                                                                                                                                                                                                                                                                      | G.400–G.449                                                                                                          |

| COORDINATION OF RADIOTELEPHONY AND LINE TELEPHONY                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | G.450-G.499                                                                                                          |

| TESTING EQUIPMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | G.500-G.599                                                                                                          |

| TRANSMISSION MEDIA CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | G.600-G.699                                                                                                          |

| Characteristics of optical components and subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | G.660-G.699                                                                                                          |

| DIGITAL TERMINAL EQUIPMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | G.700-G.799                                                                                                          |

| General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | G.700-G.709                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| Coding of analogue signals by pulse code modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | G.710-G.719                                                                                                          |

| Coding of analogue signals by pulse code modulation Coding of analogue signals by methods other than PCM                                                                                                                                                                                                                                                                                                                                                                                                                | G.710–G.719<br>G.720–G.729                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| Coding of analogue signals by methods other than PCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | G.720–G.729                                                                                                          |

| Coding of analogue signals by methods other than PCM Principal characteristics of primary multiplex equipment                                                                                                                                                                                                                                                                                                                                                                                                           | G.720–G.729<br>G.730–G.739                                                                                           |

| Coding of analogue signals by methods other than PCM Principal characteristics of primary multiplex equipment Principal characteristics of second order multiplex equipment                                                                                                                                                                                                                                                                                                                                             | G.720–G.729<br>G.730–G.739<br>G.740–G.749                                                                            |

| Coding of analogue signals by methods other than PCM Principal characteristics of primary multiplex equipment Principal characteristics of second order multiplex equipment Principal characteristics of higher order multiplex equipment                                                                                                                                                                                                                                                                               | G.720–G.729<br>G.730–G.739<br>G.740–G.749<br>G.750–G.759                                                             |

| Coding of analogue signals by methods other than PCM Principal characteristics of primary multiplex equipment Principal characteristics of second order multiplex equipment Principal characteristics of higher order multiplex equipment Principal characteristics of transcoder and digital multiplication equipment                                                                                                                                                                                                  | G.720–G.729<br>G.730–G.739<br>G.740–G.749<br>G.750–G.759<br>G.760–G.769                                              |

| Coding of analogue signals by methods other than PCM Principal characteristics of primary multiplex equipment Principal characteristics of second order multiplex equipment Principal characteristics of higher order multiplex equipment Principal characteristics of transcoder and digital multiplication equipment Operations, administration and maintenance features of transmission equipment                                                                                                                    | G.720–G.729<br>G.730–G.739<br>G.740–G.749<br>G.750–G.759<br>G.760–G.769<br>G.770–G.779                               |

| Coding of analogue signals by methods other than PCM Principal characteristics of primary multiplex equipment Principal characteristics of second order multiplex equipment Principal characteristics of higher order multiplex equipment Principal characteristics of transcoder and digital multiplication equipment Operations, administration and maintenance features of transmission equipment Principal characteristics of multiplexing equipment for the synchronous digital hierarchy                          | G.720–G.729<br>G.730–G.739<br>G.740–G.749<br>G.750–G.759<br>G.760–G.769<br>G.770–G.779<br>G.780–G.789                |

| Coding of analogue signals by methods other than PCM Principal characteristics of primary multiplex equipment Principal characteristics of second order multiplex equipment Principal characteristics of higher order multiplex equipment Principal characteristics of transcoder and digital multiplication equipment Operations, administration and maintenance features of transmission equipment Principal characteristics of multiplexing equipment for the synchronous digital hierarchy Other terminal equipment | G.720–G.729<br>G.730–G.739<br>G.740–G.749<br>G.750–G.759<br>G.760–G.769<br>G.770–G.779<br>G.780–G.789<br>G.790–G.799 |

$For {\it further details, please refer to the list of ITU-T Recommendations}.$

### ITU-T Recommendation G.707/Y.1322

| N    | etwork | node | interface | for | the sv | nchronous | digital | hierarchy | (SDH)  |

|------|--------|------|-----------|-----|--------|-----------|---------|-----------|--------|

| T.44 | CLWOID | nouc | mucriace  | 101 | uic sy | ncm onous | uigitai | merareny  | (DDII) |

### **Summary**

This Recommendation provides the requirements for the STM-N signals at the Network Node Interface of a synchronous digital network, including B-ISDN in terms of:

- bit rates;

- frames structures;

- formats for mapping and multiplexing of client signals (e.g. PDH, ATM and IP) elements;

- functionalities of the overheads.

#### **Source**

ITU-T Recommendation G.707/Y.1322 was revised by ITU-T Study Group 15 (1997-2000) and approved by the World Telecommunication Standardization Assembly (Montreal, September 27-October 6, 2000).

It already includes the editorial and technical corrections approved by ITU-T Study Group 15 on 15 March 2001 as Corrigendum 1 to ITU-T Recommendation G.707/Y.1322.

#### **FOREWORD**

The International Telecommunication Union (ITU) is the United Nations specialized agency in the field of telecommunications. The ITU Telecommunication Standardization Sector (ITU-T) is a permanent organ of ITU. ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.

The World Telecommunication Standardization Assembly (WTSA), which meets every four years, establishes the topics for study by the ITU-T study groups which, in turn, produce Recommendations on these topics.

The approval of ITU-T Recommendations is covered by the procedure laid down in WTSA Resolution 1.

In some areas of information technology which fall within ITU-T's purview, the necessary standards are prepared on a collaborative basis with ISO and IEC.

#### NOTE

In this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.

#### INTELLECTUAL PROPERTY RIGHTS

ITU draws attention to the possibility that the practice or implementation of this Recommendation may involve the use of a claimed Intellectual Property Right. ITU takes no position concerning the evidence, validity or applicability of claimed Intellectual Property Rights, whether asserted by ITU members or others outside of the Recommendation development process.

As of the date of approval of this Recommendation, ITU had received notice of intellectual property, protected by patents, which may be required to implement this Recommendation. However, implementors are cautioned that this may not represent the latest information and are therefore strongly urged to consult the TSB patent database.

#### © ITU 2001

All rights reserved. No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from ITU.

# **CONTENTS**

| 1   | Scope   |                                                              |  |  |  |  |  |

|-----|---------|--------------------------------------------------------------|--|--|--|--|--|

| 2   | Refere  | References                                                   |  |  |  |  |  |

| 3   | Terms   | Terms and definitions                                        |  |  |  |  |  |

| 4   | Acron   | Acronyms and abbreviations                                   |  |  |  |  |  |

| 5   | Conve   | ntions                                                       |  |  |  |  |  |

| 6   | Basic 1 | Multiplexing principles                                      |  |  |  |  |  |

| 6.1 | Multip  | olexing structure                                            |  |  |  |  |  |

| 6.2 | Basic   | frame structure                                              |  |  |  |  |  |

|     | 6.2.1   | Section overhead                                             |  |  |  |  |  |

|     | 6.2.2   | Administrative Unit pointers                                 |  |  |  |  |  |

|     | 6.2.3   | Administrative Units in the STM-N                            |  |  |  |  |  |

|     | 6.2.4   | Maintenance signals                                          |  |  |  |  |  |

| 6.3 | Hierar  | chical bit rates                                             |  |  |  |  |  |

| 6.4 | Interco | onnection of STM-Ns                                          |  |  |  |  |  |

| 6.5 | Scram   | bling                                                        |  |  |  |  |  |

| 6.6 | Physic  | al specification of the NNI                                  |  |  |  |  |  |

| 7   | Multip  | Multiplexing method                                          |  |  |  |  |  |

| 7.1 | Multip  | plexing of Administrative Units into STM-N                   |  |  |  |  |  |

|     | 7.1.1   | Multiplexing of Administrative Unit Groups (AUGs) into STM-N |  |  |  |  |  |

|     | 7.1.2   | Multiplexing of an AU-4 via AUG-1                            |  |  |  |  |  |

|     | 7.1.3   | Multiplexing of AU-3s via AUG-1                              |  |  |  |  |  |

|     | 7.1.4   | Multiplexing of AU-3 into STM-0                              |  |  |  |  |  |

| 7.2 | Multip  | plexing of Tributary Units into VC-4 and VC-3                |  |  |  |  |  |

|     | 7.2.1   | Multiplexing of Tributary Unit Group-3s (TUG-3s) into a VC-4 |  |  |  |  |  |

|     | 7.2.2   | Multiplexing of a TU-3 via TUG-3                             |  |  |  |  |  |

|     | 7.2.3   | Multiplexing of TUG-2s via a TUG-3                           |  |  |  |  |  |

|     | 7.2.4   | Multiplexing of TUG-2s into a VC-3                           |  |  |  |  |  |

|     | 7.2.5   | Multiplexing of a TU-2 via TUG-2s                            |  |  |  |  |  |

|     | 7.2.6   | Multiplexing of TU-1s via TUG-2s                             |  |  |  |  |  |

| 7.3 | AU-n/   | TU-n numbering scheme                                        |  |  |  |  |  |

|     | 7.3.1   | Numbering of AU-ns (VC-ns) in a STM-256                      |  |  |  |  |  |

|     | 7.3.2   | Numbering of AU-ns (VC-ns) in a STM-64                       |  |  |  |  |  |

|     | 7.3.3   | Numbering of AU-ns (VC-ns) in an STM-16                      |  |  |  |  |  |

|     | 7.3.4   | Numbering of AU-ns (VC-ns) in an STM-4                       |  |  |  |  |  |

|     | 7.3.5   | Numbering of AU-4 (VC-4) in an STM-1 signal                  |  |  |  |  |  |

|     | 7.3.6   | Numbering of AU-3 (VC-3) in an STM-0 signal     |

|-----|---------|-------------------------------------------------|

|     | 7.3.7   | Numbering of TU-3s in a VC-4                    |

|     | 7.3.8   | Numbering of TU-2s in a VC-4                    |

|     | 7.3.9   | Numbering of TU-12s in a VC-4.                  |

|     | 7.3.10  | Numbering of TU-11s in a VC-4.                  |

|     | 7.3.11  | Numbering of TU-2s in a VC-3                    |

|     | 7.3.12  | Numbering of TU-12s in a VC-3                   |

|     | 7.3.13  | Numbering of TU-11s in a VC-3                   |

| 3   | Pointer | 'S                                              |

| 3.1 | AU-n p  | oointer                                         |

|     | 8.1.1   | AU-n pointer location                           |

|     | 8.1.2   | AU-n pointer value                              |

|     | 8.1.3   | Frequency justification                         |

|     | 8.1.4   | New Data Flag (NDF)                             |

|     | 8.1.5   | Pointer generation                              |

|     | 8.1.6   | Pointer interpretation                          |

|     | 8.1.7   | AU-4 concatenation                              |

| .2  | TU-3 p  | ointer                                          |

|     | 8.2.1   | TU-3 pointer location                           |

|     | 8.2.2   | TU-3 pointer value                              |

|     | 8.2.3   | Frequency justification                         |

|     | 8.2.4   | New Data Flag (NDF)                             |

|     | 8.2.5   | Pointer generation                              |

|     | 8.2.6   | Pointer interpretation                          |

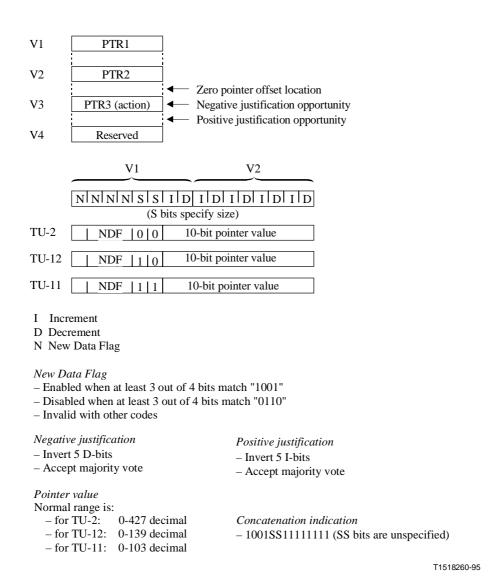

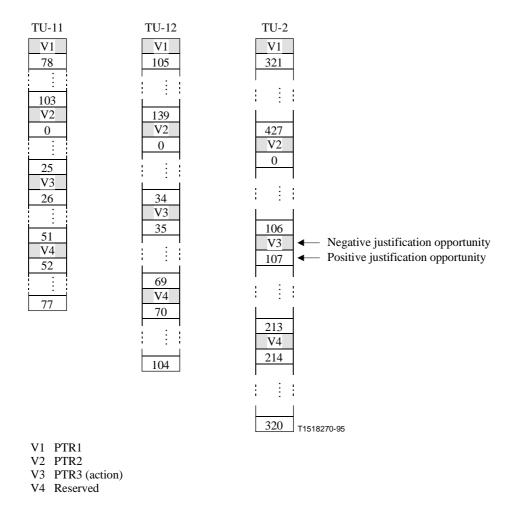

| .3  | TU-2/7  | TU-1 pointer                                    |

|     | 8.3.1   | TU-2/TU-1 pointer location                      |

|     | 8.3.2   | TU-2/TU-1 pointer value                         |

|     | 8.3.3   | TU-2/TU-1 frequency justification               |

|     | 8.3.4   | New Data Flag (NDF)                             |

|     | 8.3.5   | TU-2/TU-1 pointer generation and interpretation |

|     | 8.3.6   | TU-2 concatenation                              |

|     | 8.3.7   | TU-2/TU-1 sizes                                 |

|     | 8.3.8   | TU-2/TU-1 multiframe indication byte            |

| )   | Overhe  | ead bytes description                           |

| 9.1 | Types   | of overhead                                     |

|     | 9.1.1   | SOH                                             |

|     | 9.1.2   | Virtual Container POH                           |

| 9.2 | SOH d   | escription                                      |

|     |         | SOH bytes location                              |

|       |                                                                               | Pag   |  |  |  |  |

|-------|-------------------------------------------------------------------------------|-------|--|--|--|--|

|       | 9.2.2 SOH bytes description                                                   | . 78  |  |  |  |  |

|       | 9.2.3 Reduced SOH functionalities interface                                   | . 85  |  |  |  |  |

|       | 9.2.4 Forward Error Correction: P1, Q1                                        | . 86  |  |  |  |  |

| 9.3   | POH descriptions                                                              | . 86  |  |  |  |  |

|       | 9.3.1 VC-4-Xc/VC-4/VC-3 POH                                                   | . 86  |  |  |  |  |

|       | 9.3.2 VC-2/VC-1 POH                                                           | . 89  |  |  |  |  |

| 10    | Mapping of tributaries into VC-n                                              | . 93  |  |  |  |  |

| 10.1  | Mapping of G.702 type signals                                                 | . 93  |  |  |  |  |

|       | 10.1.1 Mapping into VC-4                                                      | . 94  |  |  |  |  |

|       | 10.1.2 Mapping into VC-3                                                      | . 96  |  |  |  |  |

|       | 10.1.3 Mapping into VC-2                                                      | . 99  |  |  |  |  |

|       | 10.1.4 Mapping into VC-12                                                     | . 101 |  |  |  |  |

|       | 10.1.5 Mapping into VC-11                                                     | . 104 |  |  |  |  |

|       | 10.1.6 VC-11 to VC-12 conversion for transport by a TU-12                     | . 110 |  |  |  |  |

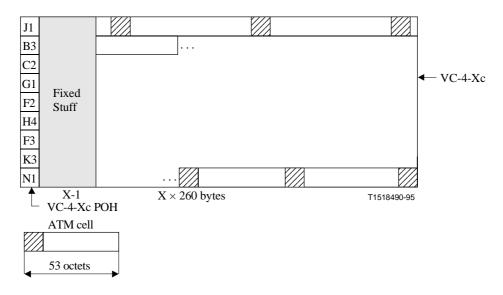

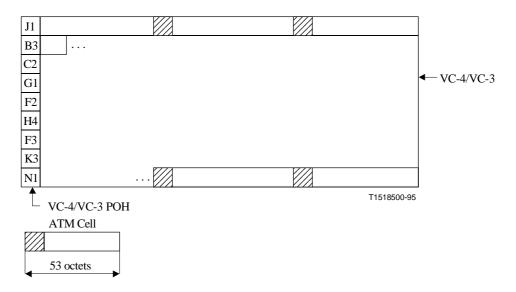

| 10.2  | Mapping of ATM cells                                                          | . 110 |  |  |  |  |

|       | 10.2.1 Mapping into VC-4-Xc/VC-4-Xv                                           | . 111 |  |  |  |  |

|       | 10.2.2 Mapping into VC-4/VC-3                                                 | . 112 |  |  |  |  |

|       | 10.2.3 Mapping into VC-2-Xc/VC-2-Xv                                           | . 112 |  |  |  |  |

|       | 10.2.4 Mapping into VC-2                                                      | . 114 |  |  |  |  |

|       | 10.2.5 Mapping into VC-12/VC-11                                               | . 115 |  |  |  |  |

| 10.3  | Mapping of HDLC framed signals                                                | . 116 |  |  |  |  |

| 10.4  | Mapping of DQDB into VC-4                                                     |       |  |  |  |  |

| 10.5  | Asynchronous mapping for FDDI at 125 000 kbit/s into VC-4                     | . 117 |  |  |  |  |

| 11    | VC concatenation                                                              | . 118 |  |  |  |  |

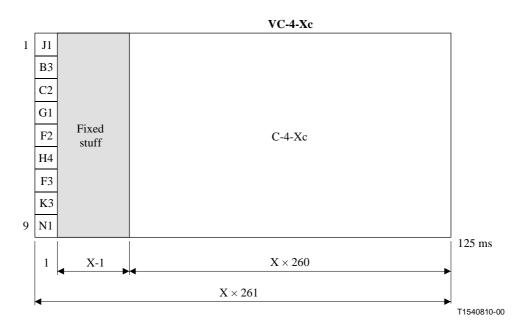

| 11.1  | Contiguous concatenation of X VC-4s (VC-4-Xc, X = 4, 16, 64, 256)             | . 119 |  |  |  |  |

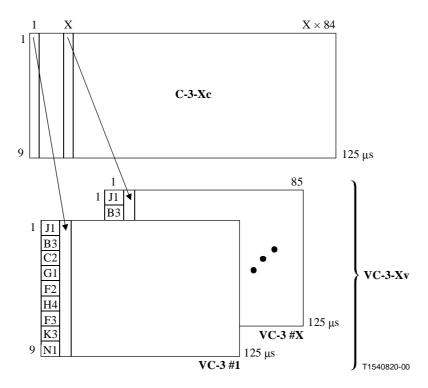

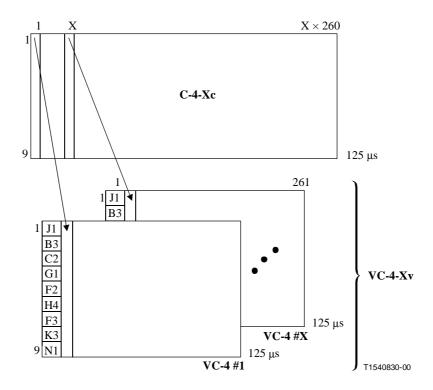

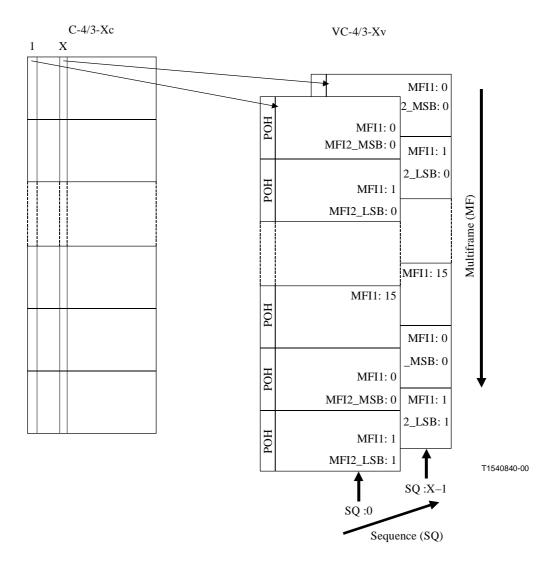

| 11.2  | Virtual concatenation of X VC-3/4s (VC-3/4-Xv, X = 1 256)                     | . 120 |  |  |  |  |

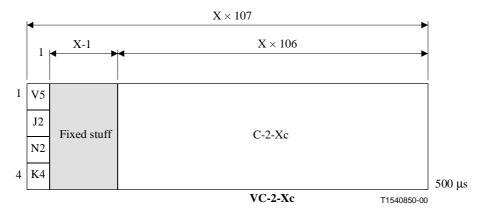

| 11.3  | Contiguous concatenation of X VC-2s in a higher order VC-3 (VC-2-Xc, X = 1 7) |       |  |  |  |  |

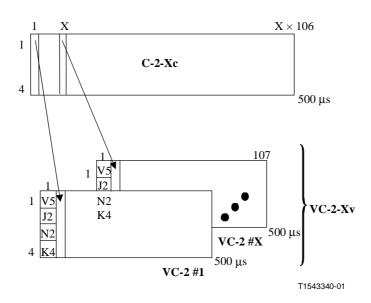

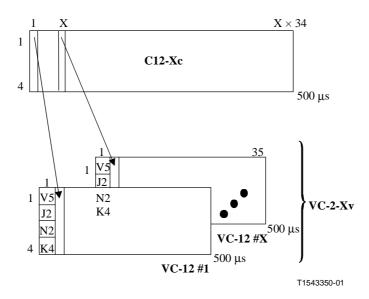

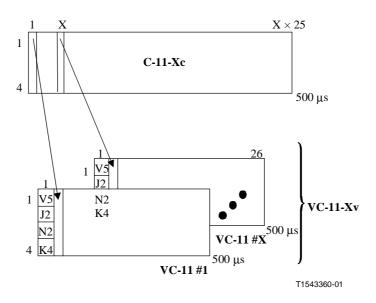

| 11.4  | Virtual concatenation of X VC-2/1s                                            | . 124 |  |  |  |  |

| Annex | A – Forward Error Correction for STM-64, and STM-256                          | . 127 |  |  |  |  |

| A.1   | Network reference model                                                       | . 127 |  |  |  |  |

| A.2   | The FEC function                                                              | . 127 |  |  |  |  |

|       | A.2.1 Code type and parameters                                                | . 127 |  |  |  |  |

|       | A.2.2 FEC encoder description and algorithm                                   | . 127 |  |  |  |  |

|       | A.2.3 Encoder and decoder locations                                           | . 128 |  |  |  |  |

|       | A.2.4 FEC delay characteristic                                                | . 128 |  |  |  |  |

|       | A.2.5 SDH and FEC check bits not included in FEC coding                       | . 128 |  |  |  |  |

|             |         |                                                                               | Page |

|-------------|---------|-------------------------------------------------------------------------------|------|

| A.3         | Mappi   | ng into the SDH frame                                                         | 128  |

|             | A.3.1   | Location of the information bits                                              | 128  |

|             | A.3.2   | Location of in-band FEC parity                                                | 129  |

|             | A.3.3   | Location of status/control bits                                               | 129  |

|             | A.3.4   | FEC Status Indication (FSI)                                                   | 130  |

|             | A.3.5   | B1 calculation at encoder and decoder                                         | 130  |

|             | A.3.6   | B2 calculation at encoder and Decoder                                         | 130  |

| A.4         | In-band | d FEC regenerator functions                                                   | 130  |

|             | A.4.1   | Regenerators not supporting in-band FEC                                       | 130  |

|             | A.4.2   | Regenerators passing in-band FEC transparently without error correction       | 130  |

|             | A.4.3   | Regenerators with error correction                                            | 130  |

| A.5         | Perform | mance monitoring                                                              | 131  |

|             | A.5.1   | FEC correctable error count                                                   | 131  |

|             | A.5.2   | FEC uncorrectable error count                                                 | 131  |

|             | A.5.3   | Error count after FEC decoding                                                | 131  |

| A.6         | FEC ac  | ctivation and deactivation                                                    | 131  |

|             | A.6.1   | FEC Operational States                                                        | 131  |

|             | A.6.2   | FEC Status Indication (FSI)                                                   | 131  |

|             | A.6.3   | MS-AIS interaction with FEC                                                   | 132  |

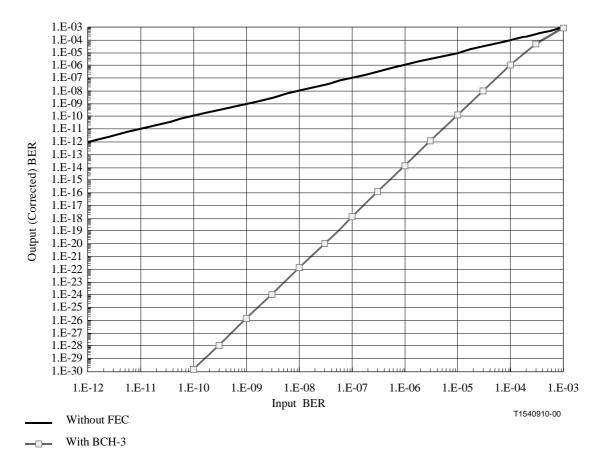

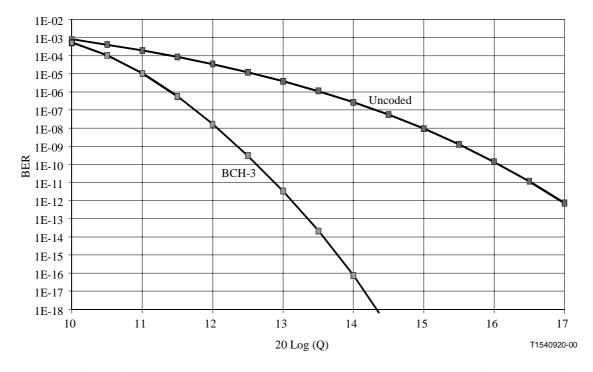

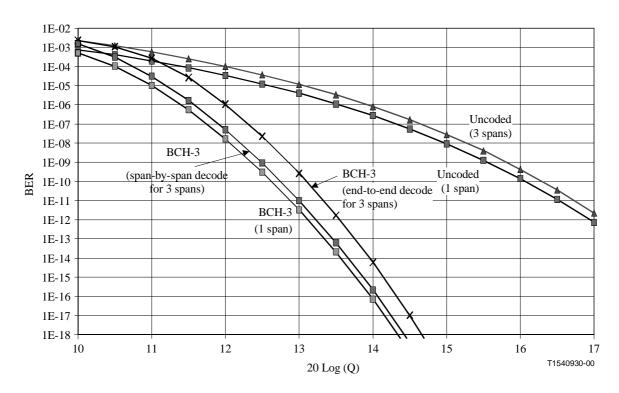

| A.7         | Perform | nance of in-band FEC                                                          | 132  |

| Annex       | B - CR  | C-7 polynomial algorithm                                                      | 132  |

| B.1         | Multip  | lication/division process                                                     | 132  |

| B.2         | Encodi  | ng procedure                                                                  | 132  |

| B.3         | Decodi  | ing procedure                                                                 | 133  |

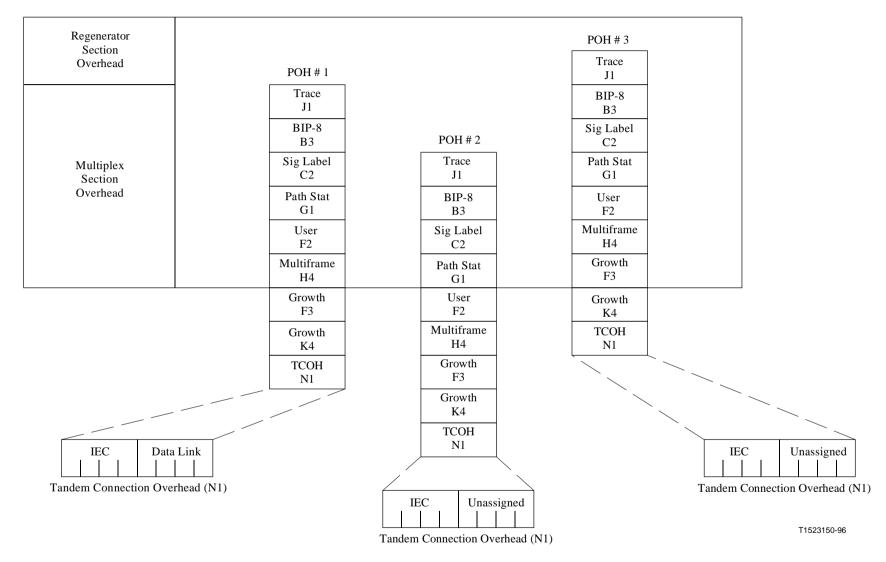

| Annex       |         | C-4-Xc/VC-4/VC-3 Tandem Connection Monitoring protocol: Option 1              | 133  |

| C.1         |         | n Connection Overhead – Byte location                                         | 133  |

| C.2         |         | ions                                                                          | 135  |

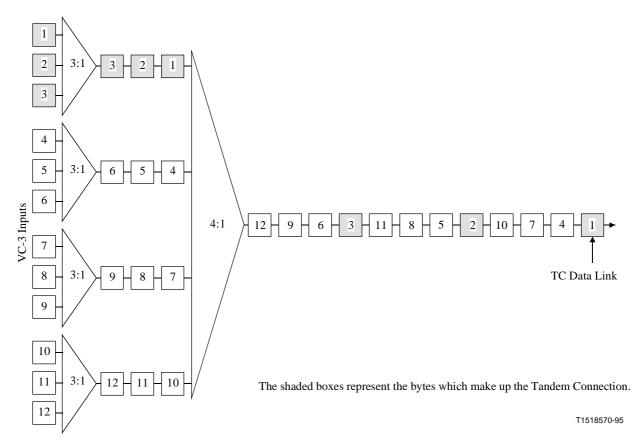

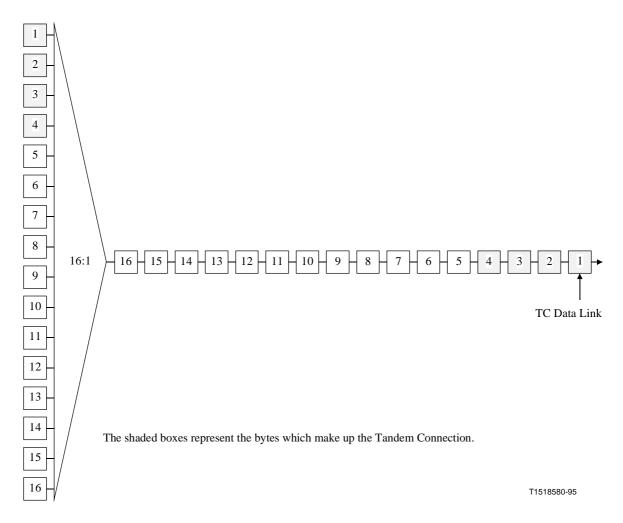

| C.3         |         | n Connection bundling                                                         | 135  |

| <b>C.</b> 3 | C.3.1   | Bundling of VC-3s within an STM-1                                             | 135  |

|             | C.3.1   | Bundling of VC-3s within an STM-N (N>1)                                       | 136  |

|             | C.3.2   | Tandem Connection Bundle Contents                                             | 136  |

|             | C.3.4   | Tandem Connection bundles in higher rate signals                              | 137  |

| C.4         |         | ng Error Count (IEC)                                                          | 137  |

|             |         |                                                                               |      |

| C.5         |         | mpensation                                                                    | 139  |

| C.6         |         | nk                                                                            | 139  |

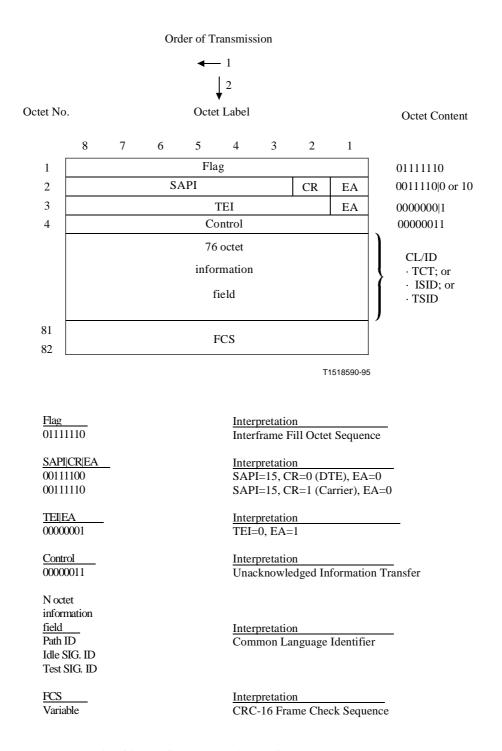

|             | C.6.1   | Format of the LAPD messages                                                   | 140  |

|             | C.6.2   | Tandem Connection Trace, Idle Signal, and Test Signal Identification Messages | 141  |

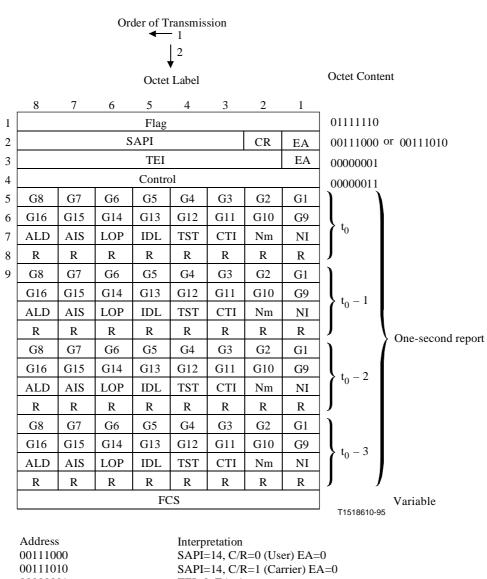

|        | C.6.3 The far-     | end performance report message                                 |

|--------|--------------------|----------------------------------------------------------------|

|        | C.6.4 Special      | carrier applications                                           |

| C.7    | Treatment of Inc   | coming Signal Failures                                         |

|        | C.7.1 Signal f     | ailures before the Tandem Connection                           |

|        | C.7.2 Signal f     | ailures within the Tandem Connection                           |

| C.8    | Tandem Connec      | tion Idle Signal                                               |

| C.9    | Tandem Connec      | tion Test Signal                                               |

| Annex  | D-VC-4-Xc/V        | C-4/VC-3 Tandem Connection Monitoring protocol: Option 2       |

| D.1    | N1 byte structur   | e                                                              |

| D.2    | TCM functional     | ity at the Tandem Connection source                            |

| D.3    | TCM functional     | ity at the Tandem Connection sink                              |

| D.4    | BIP-8 compensa     | tion                                                           |

| Annex  | E – VC-2/VC-1      | Tandem Connection Monitoring protocol                          |

| E.1    | N2 byte structur   | e                                                              |

| E.2    | TCM functional     | ity at the Tandem Connection source                            |

| E.3    | TCM functional     | ity at the Tandem Connection sink                              |

| E.4    | BIP-2 compensa     | tion                                                           |

| Append | lix I – Relationsl | nip between TU-2 address and location of columns within a VC-4 |

| Append |                    | hip between TU-12 address and location of columns within a     |

| Append |                    | ship between TU-11 address and location of columns within a    |

| Append |                    | ship between TU-2 address and location of columns within a     |

| Append |                    | ship between TU-12 address and location of columns within a    |

| Append |                    | ship between TU-11 address and location of columns within a    |

| Append | lix VII – Enhanc   | ed Remote Defect Indication (RDI)                              |

| Append |                    | ected behaviour, dependence of TC Monitoring on the incoming   |

| Append | lix IX – Forward   | Error Correction for STM-16                                    |

| Append | lix X – Performa   | nce of in-band FEC                                             |

| Append | lix XI – Bibliogr  | aphy                                                           |

#### ITU-T Recommendation G.707/Y.1322

### Network node interface for the synchronous digital hierarchy (SDH)

### 1 Scope

This Recommendation covers the Network Node Interface (NNI) specifications which are necessary to enable interconnection of network elements at their Synchronous Digital Hierarchy (SDH) interfaces for the transport of different types of payloads.

Therefore, this Recommendations specifies:

- the bit rates for STM-N signals;

- the frames structures for STM-N signals;

- the formats for mapping and multiplexing of client signals (e.g. PDH, ATM and IP) elements into an STM-N frame;

- the functionalities to be implemented in the different overheads of an STM-N frame, at the NNI of a synchronous digital network, including B-ISDN.

#### 2 References

The following Recommendations and other references contain provisions which, through reference in this text, constitute provisions of this Recommendation. At the time of publication, the editions indicated were valid. All Recommendations and other references are subject to revision; all users of this Recommendation are therefore encouraged to investigate the possibility of applying the most recent edition of the Recommendations and other references listed below. A list of the currently valid ITU-T Recommendations is regularly published.

- ITU-T G.691 (2000), Optical interfaces for single-channel STM-64, STM-256 and other SDH systems with optical amplifiers.

- ITU-T G.702 (1988), Digital hierarchy bit rates.

- ITU-T G.703 (1998), Physical/electrical characteristics of hierarchical digital interfaces.

- ITU-T G.704 (1998), Synchronous frame structures used at 1544, 6312, 2048, 8448 and 44 736 kbit/s hierarchical levels.

- ITU-T G.783 (2000), Characteristics of synchronous digital hierarchy (SDH) equipment functional blocks.

- ITU-T G.802 (1988), Interworking between networks based on different digital hierarchies and speech encoding laws.

- ITU-T G.803 (2000), Architecture of transport networks based on the synchronous digital hierarchy (SDH).

- ITU-T G.831 (2000), Management capabilities of transport networks based on the synchronous digital hierarchy (SDH).

- ITU-T G.841 (1998), Types and characteristics of SDH network protection architectures.

- ITU-T G.957 (1999), Optical interfaces for equipments and systems relating to the synchronous digital hierarchy.

- ITU-T I.432.1 (1999), *B-ISDN User-Network Interface Physical layer specification:* General characteristics.

- ITU-T I.432.2 (1999), B-ISDN User-Network Interface Physical layer specification: 155 520 kbit/s and 622 080 kbit/s operation.

- ITU-T O.181 (1996), Equipment to assess error performance on STM-N interfaces.

- ITU-R F.750-4 (2000), Architectures and functional aspects of radio-relay systems for synchronous digital hierarchy SDH-based networks.

- ITU-R S.1149-1 (1997), Network architecture and equipment functional aspects of digital satellite systems in the fixed satellite service forming part of synchronous digital hierarchy transport networks.

- ETSI ETS 300 216 (December 1992), Network Aspects (NA); Metropolitan Area Network (MAN); Physical layer convergence procedure for 155,520 Mbit/s.

#### 3 Terms and definitions

This Recommendation defines the following terms:

- **3.1 synchronous digital hierarchy (SDH)**: The SDH is a hierarchical set of digital transport structures, standardized for the transport of suitably adapted payloads over physical transmission networks.

- 3.2 synchronous transport module (STM): An STM is the information structure used to support section layer connections in the SDH. It consists of information payload and Section Overhead (SOH) information fields organized in a block frame structure which repeats every 125  $\mu$ s. The information is suitably conditioned for serial transmission on the selected media at a rate which is synchronized to the network. A basic STM is defined at 155 520 kbit/s. This is termed STM-1. Higher capacity STMs are formed at rates equivalent to N times this basic rate. STM capacities for N=4, N=16, N=64 and N=256 are defined; higher values are under consideration.

The STM-0 comprises a single Administrative Unit of level 3. The STM-N,  $N \ge 1$ , comprises a single Administrative Unit Group of level N (AUG-N) together with the SOH. The STM-N hierarchical bit rates are given in 6.3.

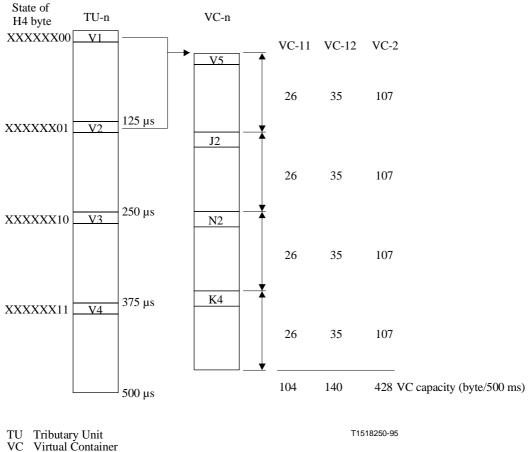

3.3 virtual container-n (VC-n): A Virtual Container is the information structure used to support path layer connections in the SDH. It consists of information payload and Path Overhead (POH) information fields organized in a block frame structure which repeats every 125 or 500  $\mu$ s. Alignment information to identify VC-n frame start is provided by the server network layer.

Two types of Virtual Containers have been identified.

- Lower order Virtual Container-n: VC-n (n=1, 2, 3)

This element comprises a single Container-n (n=1, 2, 3) plus the lower order Virtual Container POH appropriate to that level.

- Higher order Virtual Container-n: VC-n (n=3, 4)

This element comprises either a single Container-n (n=3, 4) or an assembly of Tributary Unit Groups (TUG-2s or TUG-3s), together with Virtual Container POH appropriate to that level.

- **3.4 administrative unit-n** (**AU-n**): An Administrative Unit is the information structure which provides adaptation between the higher order path layer and the multiplex section layer. It consists of an information payload (the higher order Virtual Container) and an Administrative Unit pointer which indicates the offset of the payload frame start relative to the multiplex section frame start.

Two Administrative Units are defined. The AU-4 consists of a VC-4 plus an Administrative Unit pointer which indicates the phase alignment of the VC-4 with respect to the STM-N frame. The AU-3 consists of a VC-3 plus an Administrative Unit pointer which indicates the phase alignment of

the VC-3 with respect to the STM-N frame. In each case the Administrative Unit pointer location is fixed with respect to the STM-N frame.

One or more Administrative Units occupying fixed, defined positions in an STM payload are termed an Administrative Unit Group (AUG).

An AUG-1 consists of a homogeneous assembly of AU-3s or an AU-4.

**3.5 tributary unit-n (TU-n)**: A Tributary Unit is an information structure which provides adaptation between the lower order path layer and the higher order path layer. It consists of an information payload (the lower order Virtual Container) and a Tributary Unit pointer which indicates the offset of the payload frame start relative to the higher order Virtual Container frame start.

The TU-n (n=1, 2, 3) consists of a VC-n together with a Tributary Unit pointer.

One or more Tributary Units, occupying fixed, defined positions in a higher order VC-n payload is termed a Tributary Unit Group (TUG). TUGs are defined in such a way that mixed capacity payloads made up of different size Tributary Units can be constructed to increase flexibility of the transport network.

A TUG-2 consists of a homogeneous assembly of identical TU-1s or a TU-2.

A TUG-3 consists of a homogeneous assembly of TUG-2s or a TU-3.

- **3.6 container-n** (n=1-4): A container is the information structure which forms the network synchronous information payload for a Virtual Container. For each of the defined Virtual Containers there is a corresponding container. Adaptation functions have been defined for many common network rates into a limited number of standard containers. These include those rates already defined in ITU-T G.702. Further adaptation functions will be defined in the future for new broadband rates.

- **3.7 network node interface (NNI)**: The interface at a network node which is used to interconnect with another network node.

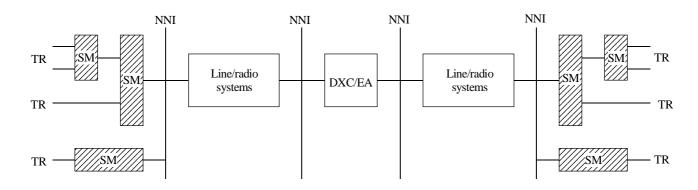

Figure 3-1 gives a possible network configuration to illustrate the location of NNI specified in this Recommendation.

DXC Digital cross-connect equipment

EA External Access equipment

SM Synchronous Multiplexer

TR Tributary

### Figure 3-1/G.707/Y.1322 – Location of the NNI

- **3.8 pointer**: An indicator whose value defines the frame offset of a Virtual Container with respect to the frame reference of the transport entity on which it is supported.

- **3.9 concatenation**: A procedure whereby a multiplicity of Virtual Containers is associated one

T1517940-95

with another with the result that their combined capacity can be used as a single container across which bit sequence integrity is maintained.

- **3.10 SDH mapping**: A procedure by which tributaries are adapted into Virtual Containers at the boundary of an SDH network.

- **3.11 SDH multiplexing**: A procedure by which multiple lower order path layer signals are adapted into a higher order path or the multiple higher order path layer signals are adapted into a multiplex section.

- **3.12 SDH aligning**: A procedure by which the frame offset information is incorporated into the Tributary Unit or the Administrative Unit when adapting to the frame reference of the supporting layer.

- **3.13 Bit Interleaved Parity-X** (**BIP-X**): BIP-X code is defined as a method of error monitoring. With even parity an X-bit code is generated by the transmitting equipment over a specified portion of the signal in such a manner that the first bit of the code provides even parity over the first bit of all X-bit sequences in the covered portion of the signal, the second bit provides even parity over the second bit of all X-bit sequences within the specified portion, etc. Even parity is generated by setting the BIP-X bits so that there is an even number of 1s in each monitored partition of the signal. A monitored partition comprises all bits which are in the same bit position within the X-bit sequences in the covered portion of the signal. The covered portion includes the BIP-X.

- **3.14 concatenation**: The process of summing the bandwidth of a number of smaller containers into a larger bandwidth container. Two versions exist:

- Contiguous concatenation;

- Virtual concatenation.

- **3.15 shortened binary-BCH**: A shortened version of the class of the block linear cyclic codes. These shortened binary BCH codes have the following common properties, i.e.:

$$n = 2^m - 1 - s$$

$$k = n - t \times m$$

$$d = 2 \times t + 1$$

where:

n the size of the whole code word;

k the number of the information bits;

m the parameter of the BCH code;

t the number of the corrected errors within the block of the BCH code;

d minimum code distance:

s the amount of information eliminated as part of the code shorting.

- **3.16 generator polynomial**: The polynomial that is used for encoding of any cyclic codes. The remainder after division of the information polynomial by generating polynomial is the redundancy part of the encoded code word.

- **3.17 systematic code**: The original data bits for binary codes are unchanged by the encoding procedure. Redundant bits or symbols (parity) are added separately to each code block.

#### 4 Acronyms and abbreviations

This Recommendation uses the following abbreviations:

AIS Alarm Indication Signal

API Access Point Identifier

APS Automatic Protection Switching

ATM Asynchronous Transfer Mode

AU-n Administrative Unit-n

AUG-N Administrative Unit Group-N

BCH Bose-Chaudhuri-Hocquenghem

BCH-3 Triple error correcting BCH code

BER Bit Error Ratio

BIP-X Bit Interleaved Parity-X

C-n Container-n

CAS Channel Associated Signalling

CRC-N Cyclic Redundancy Check-N

DCC Data Communication Channel

DQDB Distributed Queue Dual Bus

FDDI Fibre Distributed Data Interface

FEBE Far End Block Error (renamed as REI)

FEC Forward Error Correction

FERF Far End Receive Failure (renamed as RDI)

FSI FEC Status Indication

HDLC High-level Data Link Control

HEC Header Error Control

HOVC Higher Order Virtual Container

IEC Incoming Error Count

IP Internet Protocol

ISF Incoming Signal Failure

ISDN Integrated Services Digital Network

ISID Idle Signal Identification

LAPD Link Access Protocol for D-channel

LAPS Link Access Procedure – SDH

LCD Loss of Cell Delineation

LOP Loss of Pointer

LOVC Low Order Virtual Container

LSB Least Significant Bit

MAN Metropolitan Area Network

MSB Most Significant Bit

MS-AIS Multiplex Section Alarm Indication Signal

MSF-AIS Multiplex Section FEC Alarm Indication Signal

MSOH Multiplex Section Overhead

MS-RDI Multiplex Section Remote Defect Indication

MS-REI Multiplex Section Remote Error Indication

MSTE Multiplex Section Terminating Element

NDF New Data Flag

NNI Network Node Interface

ODI Outgoing Defect Indication

OEI Outgoing Error Indication

OH Overhead

PDH Plesiochronous Digital Hierarchy

PLM Payload Mismatch POH Path Overhead

PPP Point-to-Point Protocol

PTE Path Terminating Element

PTR Pointer

RDI Remote Defect Indication (former FERF)

REI Remote Error Indication (former FEBE)

RFI Remote Failure Indication

RSOH Regenerator Section Overhead SDH Synchronous Digital Hierarchy

SLM Signal Label Mismatch

SOH Section Overhead

SSU Synchronization Supply Unit

$STM(\text{-}N) \quad Synchronous \ Transport \ Module \ (\text{-}N)$

TCM Tandem Connection Monitoring

TC-RDI Tandem Connection Remote Defect IndicationTC-REI Tandem Connection Remote Error Indication

TCOH Tandem Connection Overhead TCT Tandem Connection Trace

TCTE Tandem Connection Terminating Element

TIM Trace Identifier Mismatch

TSID Test Signal Identification

TTI Trace Identifier

TU-n Tributary Unit-n

TUG(-n) Tributary Unit Group (-n)

UNEQ Unequipped

VC-n Virtual Container-n

VC-n-X X concatenated Virtual Container-ns

VC-n-Xc X Contiguously concatenated VC-ns

VC-n-Xv X Virtually concatenated VC-ns

#### **5** Conventions

The order of transmission of information in all the diagrams in this Recommendation is first from left to right and then from top to bottom. Within each byte the most significant bit is transmitted first. The most significant bit (bit 1) is illustrated at the left in all the diagrams.

### **6** Basic Multiplexing principles

### 6.1 Multiplexing structure

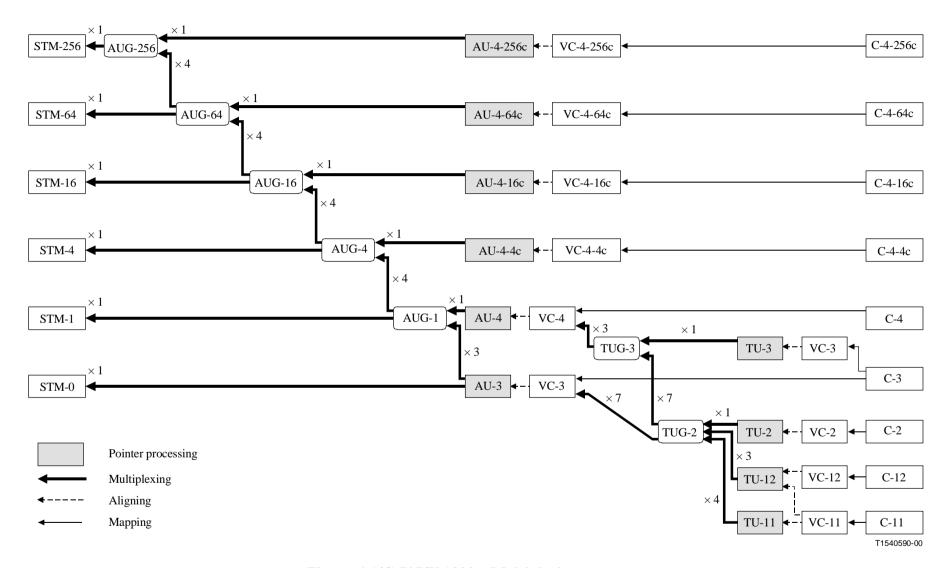

Figure 6-1 shows the relationship between various multiplexing elements that are defined in Table 6-1, and illustrates possible multiplexing structures.

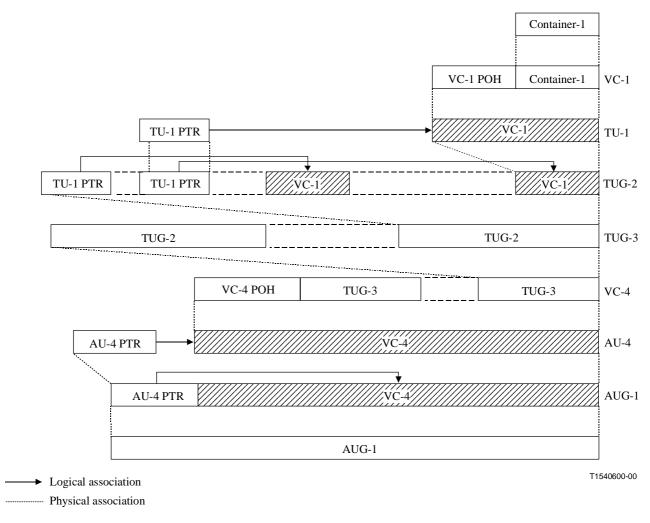

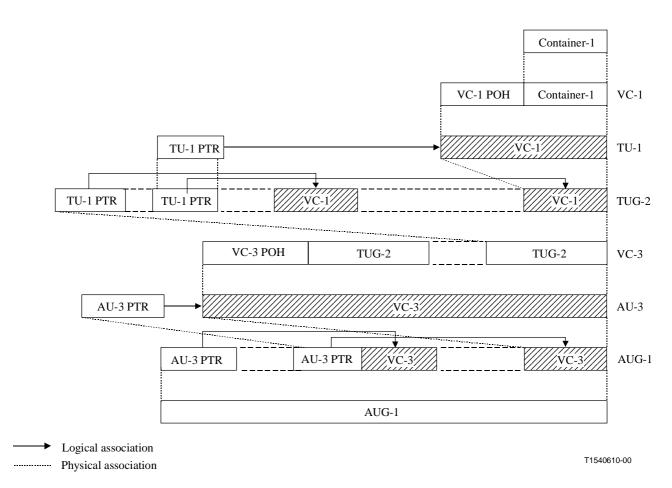

Figures 6-2, 6-3, 6-4 and 6-5 show how various signals are multiplexed using these multiplexing elements.

Details of the multiplexing method and mappings are given in clauses 7 and 10.

Descriptions of the various multiplexing elements are given in clauses 8 to 10.

Descriptions of the various concatenations are given in clause 11.

NOTE – High rate VC-4-Xc could be used without any constraints in point-to-point connections. SDH networks may be limited to a certain bit rate of VC-4-Xc (e.g.  $X \le 64$ ), e.g. due to rings with MSSPRING that has to reserve 50% of the STM-N bandwidth for protection.

Table 6-1/G.707/Y.1322 – VC types and capacity

| VC type   | VC bandwidth      | VC payload        |

|-----------|-------------------|-------------------|

| VC-11     | 1 664 kbit/s      | 1 600 kbit/s      |

| VC-12     | 2 240 kbit/s      | 2 176 kbit/s      |

| VC-2      | 6 848 kbit/s      | 6 784 kbit/s      |

| VC-3      | 48 960 kbit/s     | 48 384 kbit/s     |

| VC-4      | 150 336 kbit/s    | 149 760 kbit/s    |

| VC-4-4c   | 601 344 kbit/s    | 599 040 kbit/s    |

| VC-4-16c  | 2 405 376 kbit/s  | 2 396 160 kbit/s  |

| VC-4-64c  | 9 621 504 kbit/s  | 9 584 640 kbit/s  |

| VC-4-256c | 38 486 016 kbit/s | 38 338 560 kbit/s |

Figure 6-1/G.707/Y.1322 – Multiplexing structure

NOTE – Unshaded areas are phase aligned. Phase alignment between the unshaded and shaded areas is defined by the pointer (PTR) and is indicated by the arrow.

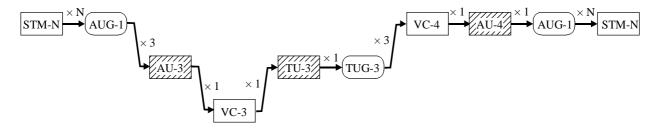

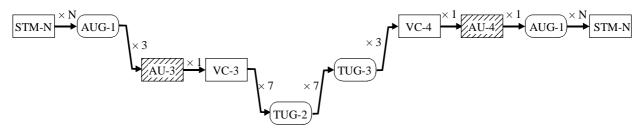

Figure 6-2/G.707/Y.1322 – Multiplexing method directly from Container-1 using AU-4

NOTE – Unshaded areas are phase aligned. Phase alignment between the unshaded and shaded areas is defined by the pointer (PTR) and is indicated by the arrow.

Figure 6-3/G.707/Y.1322 – Multiplexing method directly from Container-1 using AU-3

NOTE – Unshaded areas are phase aligned. Phase alignment between the unshaded and shaded areas is defined by the pointer (PTR) and is indicated by the arrow.

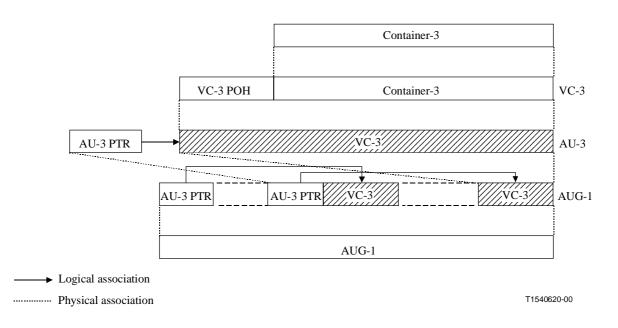

Figure 6-4/G.707/Y.1322 – Multiplexing method directly from Container-3 using AU-3

NOTE – Unshaded areas are phase aligned. Phase alignment between the unshaded and shaded areas is defined by the pointer (PTR) and is indicated by the arrow.

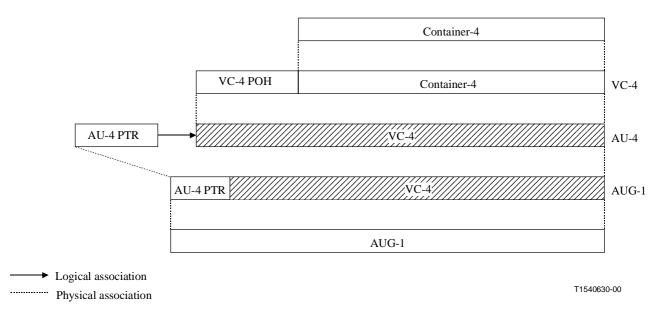

Figure 6-5/G.707/Y.1322 – Multiplexing method directly from Container-4 using AU-4

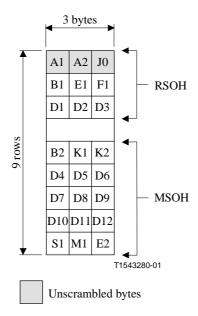

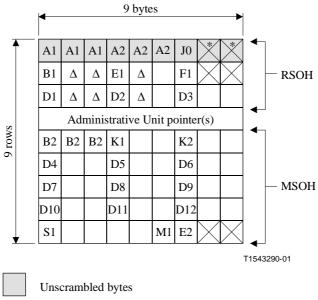

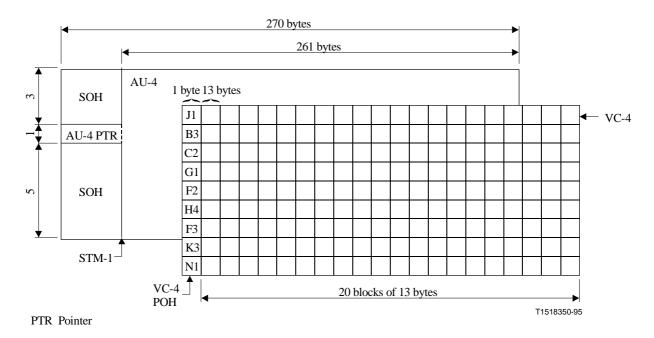

#### **6.2** Basic frame structure

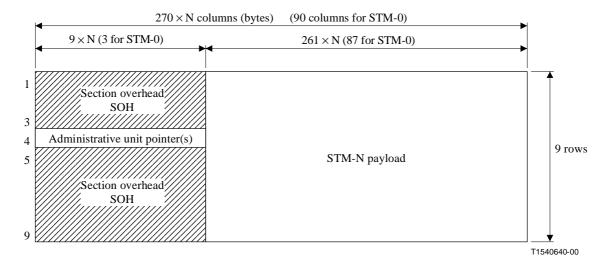

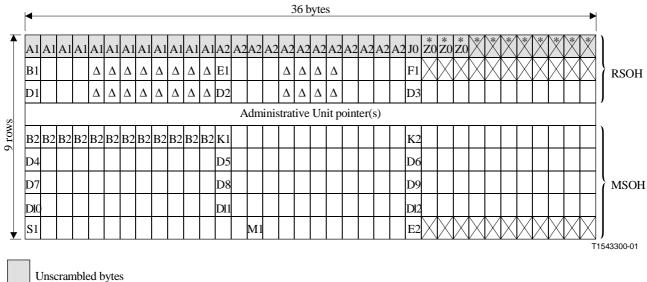

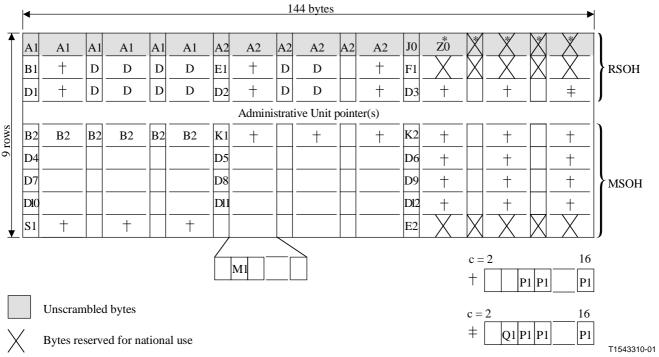

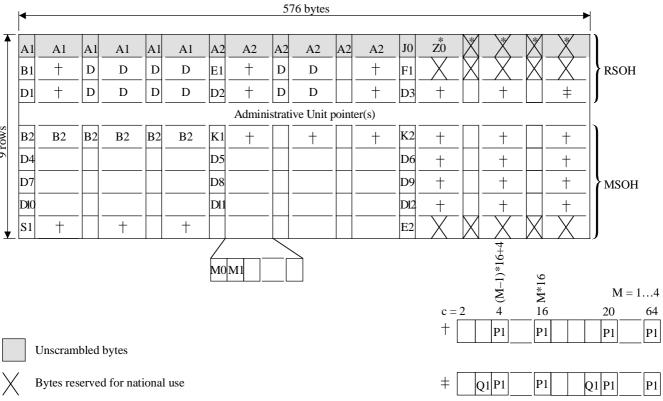

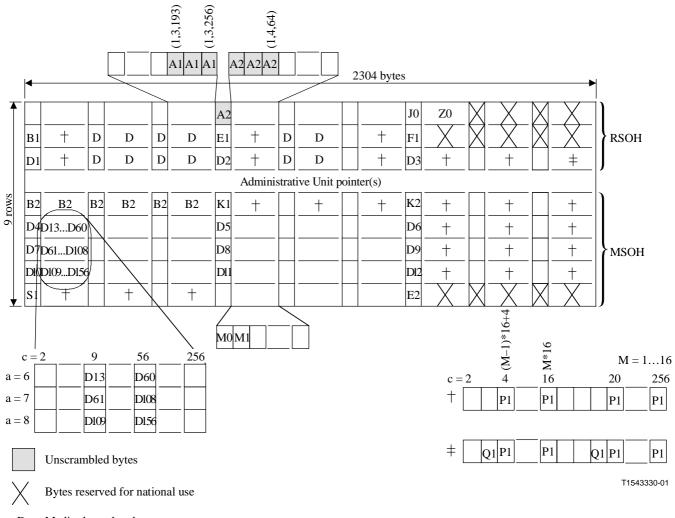

STM-N frame structure is shown in Figure 6-6. The three main areas of the STM-N frame are indicated:

- SOH;

- Administrative Unit pointer(s);

- Information payload.

Figure 6-6/G.707/Y.1322 – STM-N frame structure

#### **6.2.1** Section overhead

Rows 1-3 and 5-9 of columns 1 to  $9 \times N$  of the STM-N in Figure 6-6 are dedicated to the SOH.

The allocation of SOH capacity and an explanation of the overhead functions are given in clause 9.

### **6.2.2** Administrative Unit pointers

Row 4 of columns 1 to  $9 \times N$  in Figure 6-6 is available for Administrative Unit pointers. The application of pointers and their detailed specifications are given in clause 8.

### 6.2.3 Administrative Units in the STM-N

The STM-N payload support one AUG-N where the:

- a) AUG-256 may consist of:

- 1) four AUG-64;

- 2) one AU-4-256c.

- b) AUG-64 may consist of:

- 1) four AUG-16;

- 2) one AU-4-64c.

- c) AUG-16 may consist of:

- 1) four AUG-4;

- 2) one AU-4-16c.

- d) AUG-4 may consist of:

- 1) four AUG-1;

- 2) one AU-4-4c.

- e) AUG-1 may consist of:

- 1) one AU-4;

- 2) three AU-3s.

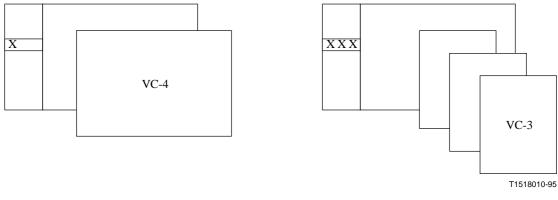

The VC-n associated with each AU-n does not have a fixed phase with respect to the STM-N frame. The location of the first byte of the VC-n is indicated by the AU-n pointer. The AU-n pointer is in a fixed location in the STM-N frame. Examples are illustrated in Figures 6-2, 6-3, 6-4, 6-5, 6-6, 6-7 and 6-8.

The AU-4 may be used to carry, via the VC-4, a number of TU-ns (n=1, 2, 3) forming a two-stage multiplex. An example of this arrangement is illustrated in Figures 6-7 a) and 6-8 a). The VC-n associated with each TU-n does not have a fixed phase relationship with respect to the start of the VC-4. The TU-n pointer is in a fixed location in the VC-4 and the location of the first byte of the VC-n is indicated by the TU-n pointer.

The AU-3 may be used to carry, via the VC-3, a number of TU-ns (n=1, 2) forming a two-stage multiplex. An example of this arrangement is illustrated in Figures 6-7 b) and 6-8 b). The VC-n associated with each TU-n does not have a fixed phase relationship with respect to the start of the VC-3. The TU-n pointer is in a fixed location in the VC-3 and the location of the first byte of the VC-n is indicated by the TU-n pointer.

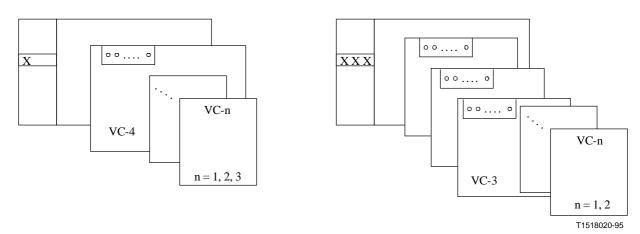

a) STM-1 with one AU-4

b) STM-1 with three AU-3s

X AU-n pointer AU-n AU-n pointer + VC-n (see clause 8)

$Figure\ 6\text{-}7/G.707/Y.1322-Administrative\ Units\ in\ STM\text{-}1\ frame$

- a) STM-1 with one AU-4 containing TUs

- b) STM-1 with three AU-3s containing TUs

- X AU-n pointer

- o TU-n pointer

- AU-n AU-n pointer + VC-n (see clause 8)

- TU-n TU-n pointer + VC-n (see clause 8)

Figure 6-8/G.707/Y.1322 – Two-stage multiplex

### 6.2.4 Maintenance signals

### **6.2.4.1** Alarm Indication Signals

An Alarm Indication Signal (AIS) is a signal sent downstream as an indication that an upstream defect has been detected.

#### 6.2.4.1.1 MS-AIS

The Multiplex Section AIS (MS-AIS) is specified as all "1"s in the entire STM-N, excluding the STM-N RSOH.

### 6.2.4.1.2 MSF-AIS

The Multiplex Section FEC AIS (MSF-AIS) is specified as all "1"s in the entire STM-N, excluding the STM-N RSOH except P1 and Q1 bytes.

#### 6.2.4.1.3 **AU/TU-AIS**

The Administrative Unit AIS (AU-AIS) is specified as all "1"s in the entire AU-n (n=3, 4, 4-Xc), including the AU-n pointer.

The Tributary Unit AIS (TU-AIS) is specified as all "1"s in the entire TU-n (n=1, 2, 3), including the TU-n pointer.

#### 6.2.4.1.4 VC-AIS

An AU/TU-AIS incoming to a Tandem Connection (TC) is translated into a Virtual Container AIS (VC-AIS) within the Tandem Connection because a valid AU-n/TU-n pointer is needed for Tandem Connection Monitoring (TCM).

VC-n (n=3, 4, 4-Xc) AIS is specified as all "1"s in the entire VC-n with a valid network operator byte N1 – supporting TCM functionality – and a valid Error Detection Code in the B3 byte.

VC-n (n=1, 2) AIS is specified as all "1"s in the entire VC-n with a valid network operator byte N2 – supporting TCM functionality – and a valid Error Detection Code in bits 1 and 2 of V5 byte.

### 6.2.4.2 Unequipped VC-n signal

### 6.2.4.2.1 Case of network supporting the transport of Tandem Connection signals

For the case of networks supporting the transport of Tandem Connection signals, the VC-n (n=3, 4) or VC-4-Xc unequipped signal is a signal having an all "0"s in the higher order virtual container path signal label byte (C2), the Tandem Connection Monitoring byte (N1) and the path trace byte (J1), and a valid BIP-8 byte (B3). The virtual container payload and the remaining path overhead bytes are unspecified.

For the case of networks supporting the transport of Tandem Connection signals, the VC-n (n=1, 2) unequipped signal is a signal having an all "0"s in the lower order virtual container path signal label (bits 5, 6, 7 of byte V5), the Tandem Connection Monitoring byte (N2) and the path trace byte (J2), and a valid BIP-2 (bits 1, 2 of byte V5). The virtual container payload and the remaining path overhead bytes are unspecified.

These signals indicate to downstream transport processing functions (refer to ITU-T G.803) that the virtual container is unoccupied, not connected to a path termination source function. Additional information on the quality is only available by means of the BIP monitoring.

Within a Tandem Connection, an unequipped VC-n signal generated before the Tandem Connection will have a valid (non all "0"s) Tandem Connection Monitoring byte (N1, N2).

### 6.2.4.2.2 Case of network not supporting the transport of Tandem Connection signals

For the case of networks not supporting the transport of Tandem Connection signals, the VC-n (n=3, 4) or VC-4-Xc unequipped signal is a signal having an all "0"s in the higher order virtual container path signal label byte (C2) and the path trace byte (J1), and a valid BIP-8 byte (B3). The virtual container payload and the remaining path overhead bytes are unspecified.

For the case of networks not supporting the transport of Tandem Connection signals, the VC-n (n=1, 2) unequipped signal is a signal having an all "0"s in the lower order virtual container path signal label (bits 5, 6, 7 of byte V5) and the path trace byte (J2), and a valid BIP-2 (bits 1, 2 of byte V5). The virtual container payload and the remaining path overhead bytes are unspecified.

### 6.2.4.3 Supervisory-unequipped VC-n signal

### 6.2.4.3.1 Case of network supporting the transport of Tandem Connection signals

For the case of networks supporting the transport of Tandem Connection signals, the VC-n (n=3, 4) or VC-4-Xc supervisory-unequipped signal is a signal having an all "0"s in the higher order virtual

container path signal label byte (C2) and the Tandem Connection Monitoring byte (N1), a valid BIP-8 byte (B3), a valid path trace identifier byte (J1), and a valid path status byte (G1). The virtual container payload is unspecified. The content of the remaining path overhead bytes F2, H4, F3 and K3 is for further study.

The VC-n (n=3, 4) supervisory-unequipped signal is an enhanced unequipped VC-n signal.

For the case of networks supporting the transport of Tandem Connection signals, the VC-n (n=1, 2) supervisory-unequipped signal is a signal having an all "0"s in the lower order virtual container path signal label (bits 5, 6, 7 of byte V5) and the Tandem Connection Monitoring byte (N2), a valid BIP-2 (bits 1, 2 of byte V5), a valid path trace byte (J2), and valid path status (bits 3 and 8 of byte V5). The virtual container payload is unspecified. The content of the remaining path overhead bytes/bits V5 bit 4 and K4 is for further study.

The VC-n (n=1, 2) supervisory-unequipped signal is an enhanced unequipped VC-n signal.

These signals indicate to downstream transport processing functions (refer to UIT-T G.803) that the virtual container is unoccupied, and sourced by a supervisory generator. Additional information on quality, source and status of the connection is available by means of the bit error, path trace and path status indications.

Within a Tandem Connection, a supervisory-unequipped VC-n signal generated before the Tandem Connection will have a valid (non all "0"s) Tandem Connection Monitoring byte (N1, N2).

### 6.2.4.3.2 Case of network not supporting the transport of Tandem Connection signals

For the case of networks not supporting the transport of Tandem Connection signals, the VC-n (n=3, 4) or VC-4-Xc supervisory-unequipped signal is a signal having an all "0"s in the higher order virtual container path signal label byte (C2), a valid BIP-8 byte (B3), a valid path trace identifier byte (J1), and a valid path status byte (G1). The virtual container payload is unspecified. The content of the remaining path overhead bytes F2, H4, F3, K3 and N1 is for further study.

For the case of networks not supporting the transport of Tandem Connection signals, the VC-n (n=1, 2) supervisory-unequipped signal is a signal having an all "0"s in the lower order virtual container path signal label (bits 5, 6, 7 of byte V5), a valid BIP-2 (bits 1, 2 of byte V5), a valid path trace byte (J2), and valid path status (bits 3 and 8 of byte V5). The virtual container payload is unspecified. The content of the remaining path overhead bytes/bits V5 bit 4, N2 and K4 is for further study.

#### **6.3** Hierarchical bit rates

The zero level of the synchronous digital hierarchy shall be 51 840 kbit/s.

The first level of the synchronous digital hierarchy shall be 155 520 kbit/s.

Higher synchronous digital hierarchy bit rates shall be obtained as integer multiples of the first level bit rate and shall be denoted by the corresponding multiplication factor of the first level rate.

The bit rates listed in Table 6-2 constitute the synchronous digital hierarchy:

Table 6-2/G.707/Y.1322 – SDH hierarchical bit rates

| Synchronous digital<br>hierarchy level                                     | Hierarchical bit rate (kbit/s) |  |  |

|----------------------------------------------------------------------------|--------------------------------|--|--|

| 0                                                                          | 51 840                         |  |  |

| 1                                                                          | 155 520                        |  |  |

| 4                                                                          | 622 080                        |  |  |

| 16                                                                         | 2 488 320                      |  |  |

| 64                                                                         | 9 953 280                      |  |  |

| 256                                                                        | 39 813 120                     |  |  |

| NOTE – The specification of levels higher than 256 requires further study. |                                |  |  |

#### 6.4 Interconnection of STM-Ns

The SDH is designed to be universal, allowing transport of a large variety of signals including all those specified in ITU-T G.702. However, different structures can be used for the transport of Virtual Containers. The following interconnection rules will be used:

- a) The rule for interconnecting two AUG-1 based upon two different types of Administrative Unit, namely AU-4 and AU-3, will be to use the AU-4 structure. Therefore, the AUG-1 based upon AU-3 will be demultiplexed to the VC-3 or TUG-2 level according to the type of the payload, and remultiplexed within an AUG-1 via the TUG-3/VC-4/AU-4 route. This is illustrated in Figures 6-9 a) and 6-9 b).

- b) The rule for interconnecting VC-11s transported via different types of Tributary Unit, namely TU-11 and TU-12, will be to use the TU-11 structure. This is illustrated in Figure 6-9 c). VC-11, TU-11 and TU-12 are described in the following clauses.

- c) The rule for interconnecting concatenated VC-3/4s transported via different types of concatenation, namely contiguous and virtual, will be to use the contiguous concatenation unless otherwise mutually agreed by the operators providing the transport.

a) Interconnection of VC-3 with C-3 payload

b) Interconnection of TUG-2

c) Interconnection of VC-11

Figure 6-9/G.707/Y.1322 – Interconnection of STM-Ns

This SDH interconnection rule does not modify the interworking rules defined in ITU-T G.802 for networks based upon different Plesiochronous Digital Hierarchies and speech encoding laws.

### 6.5 Scrambling

The STM-N (N=0, 1, 4, 16, 64, 256) signal must have sufficient bit timing content at the NNI. A suitable bit pattern, which prevents a long sequence of "1"s or "0"s is provided by using a scrambler.

The STM-N (N=0, 1, 4, 16, 64, 256) signal shall be scrambled with a frame synchronous scrambler of sequence length 127 operating at the line rate.

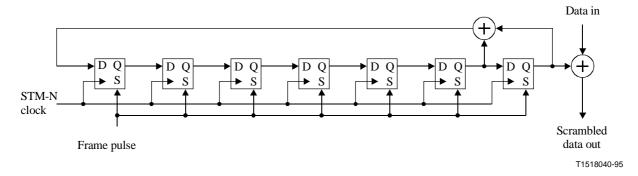

The generating polynomial shall be  $1 + X^6 + X^7$ . Figure 6-10 gives a functional diagram of the frame synchronous scrambler.

Figure 6-10/G.707/Y.1322 – Frame synchronous scrambler (functional diagram)

The scrambler shall be reset to "1111111" on the most significant bit of the byte following the last byte of the first row of the STM-N SOH S (1,9,N). This bit, and all subsequent bits to be scrambled shall be added modulo 2 to the output from the X<sup>7</sup> position of the scrambler. The scrambler shall run continuously throughout the complete STM-N frame.

The first row of the STM-N (N  $\leq$  64) SOH (9  $\times$  N bytes, 3 bytes for STM-0, including the A1 and A2 framing bytes) shall not be scrambled.

NOTE 1 – Care should be taken in selecting the binary content of the Z0 bytes and of the bytes reserved for national use which are excluded from the scrambling process of the STM-N signal to ensure that long sequences of "1"s or "0"s do not occur.

For the first row of the STM-256 SOH bytes only S (1,3,193) [1,705] to S (1,4,64) [1,832] shall not be scrambled.

NOTE 2 – The scrambler shall continue to run during the above-mentioned frame positions.

NOTE 3 – Thus STM-256, SOH bytes S (1,1,1) [1,1] to S (1,3,192) [1,704] and S (1,4,65) [1,833] to S (1,9,256) [1,2304] shall be scrambled with the scrambler running from the reset in the previous STM-256 frame.

NOTE 4 – For the unused bytes in row 1 of the STM-256 frame, a pattern should be used that provides sufficient transitions and no significant DC unbalance after scrambling.

### 6.6 Physical specification of the NNI

Specifications for physical electrical characteristics of the NNI are contained in ITU-T G.703.

Specifications for physical optical characteristics of the NNI are contained in ITU-T G.957 and G.691.

### 7 Multiplexing method

### 7.1 Multiplexing of Administrative Units into STM-N

### 7.1.1 Multiplexing of Administrative Unit Groups (AUGs) into STM-N

#### 7.1.1.1 Multiplexing of AUG-N into STM-N, N=(1, 4, 16, 64, 256)

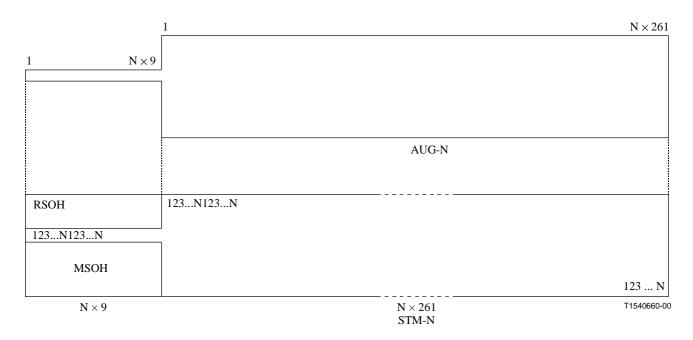

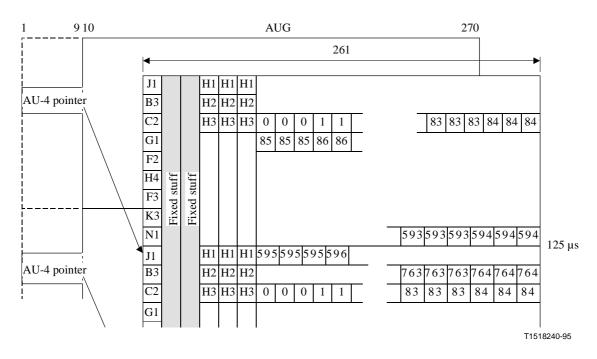

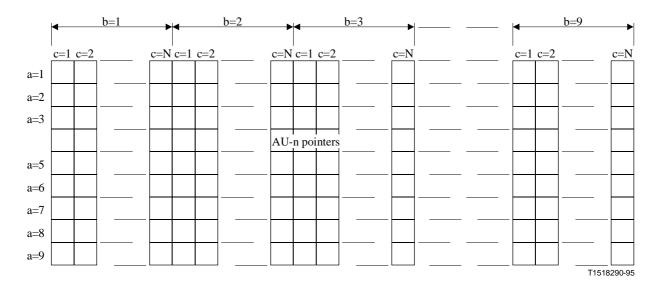

The AUG-N is a structure of 9 rows by  $N \times 261$  columns plus  $N \times 9$  bytes in row 4 (for the AU-n pointers). The STM-N consists of an SOH as described in 9.2 and a structure of 9 rows by  $N \times 261$  columns with  $N \times 9$  bytes in row 4 (for the AU-n pointers). The AUG-N is multiplexed into this structure and has a fixed phase relationship with respect to the STM-N as shown in Figure 7-1.

Figure 7-1/G.707/Y.1322 – Multiplexing of AUG-N into STM-N

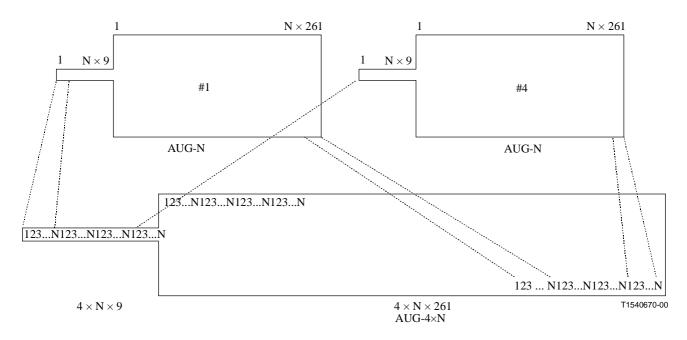

### 7.1.1.2 Multiplexing of AUG-Ns into AUG-4×N

The arrangement of 4 AUG-Ns multiplexed into the AUG-4×N is shown in Figure 7-2. The AUG-N is a structure of 9 rows by  $N \times 261$  columns plus  $N \times 9$  bytes in row 4 (for the AU-n pointers). The 4 AUG-Ns are block interleaved into the AUG-4×N structure with a block length of N bytes. The AUG-Ns have a fixed phase relationship with respect to the AUG-4×N.

Figure 7-2/G.707/Y.1322 – Multiplexing of 4 AUG-Ns into AUG-4×N

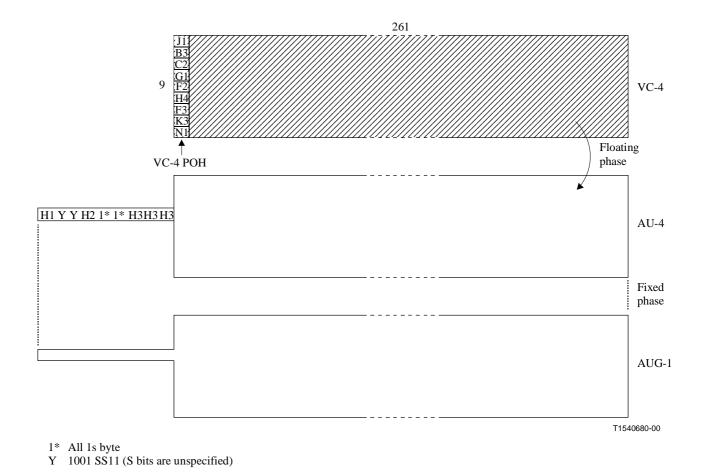

### 7.1.2 Multiplexing of an AU-4 via AUG-1

The multiplexing arrangement of a single AU-4 via the AUG-1 is depicted in Figure 7-3. The 9 bytes at the beginning of row 4 are allocated to the AU-4 pointer. The remaining 9 rows by 261 columns is

allocated to the Virtual Container-4 (VC-4). The phase of the VC-4 is not fixed with respect to the AU-4. The location of the first byte of the VC-4 with respect to the AU-4 pointer is given by the pointer value. The AU-4 is placed directly in the AUG-1.

Figure 7-3/G.707/Y.1322 – Multiplexing of AU-4 via AUG-1

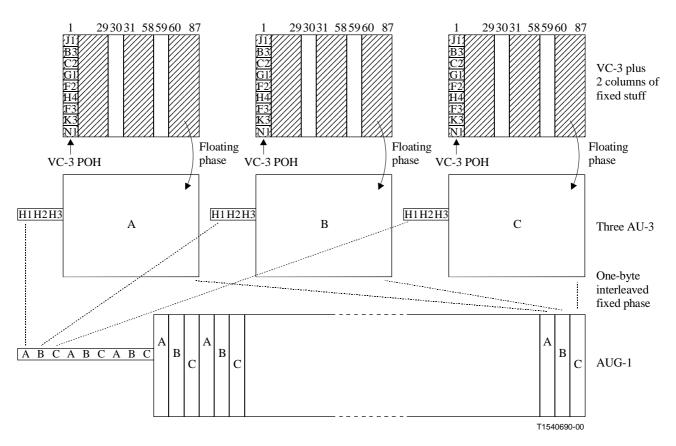

### 7.1.3 Multiplexing of AU-3s via AUG-1

The multiplexing arrangement of three AU-3s via the AUG-1 is depicted in Figure 7-4. The 3 bytes at the beginning of row 4 are allocated to the AU-3 pointer. The remaining 9 rows by 87 columns is allocated to the VC-3 and two columns of fixed stuff. The byte in each row of the two columns of fixed stuff of each AU-3 shall be the same. The phase of the VC-3 and the two columns of fixed stuff is not fixed with respect to the AU-3. The location of the first byte of the VC-3 with respect to the AU-3 pointer is given by the pointer value. The three AU-3s are one-byte interleaved in the AUG-1.

NOTE – The byte in each row of the two columns of fixed stuff of each AU-3 shall be the same.

Figure 7-4/G.707/Y.1322 – Multiplexing of AU-3s via AUG-1

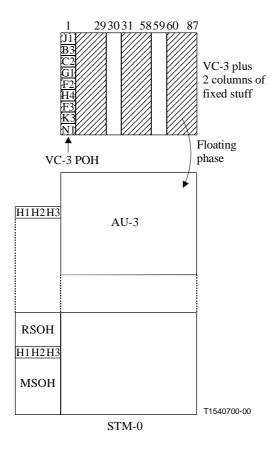

### 7.1.4 Multiplexing of AU-3 into STM-0

The AU-3 is a structure of 9 rows by 87 columns plus 3 bytes in row 4 (for the AU-3 pointers). The STM-0 consists of an SOH as described in 9.2 and a structure of 9 rows by 87 columns with 3 bytes in row 4 (for the AU-3 pointers). The AU-3 is multiplexed into this structure and have a fixed phase relationship with respect to the STM-0 as shown in Figure 7-5.

NOTE – The byte in each row of the two columns of fixed stuff of each AU-3 shall be the same.

Figure 7-5/G.707/Y.1322 – Multiplexing of AU-3 into STM-0

### 7.2 Multiplexing of Tributary Units into VC-4 and VC-3

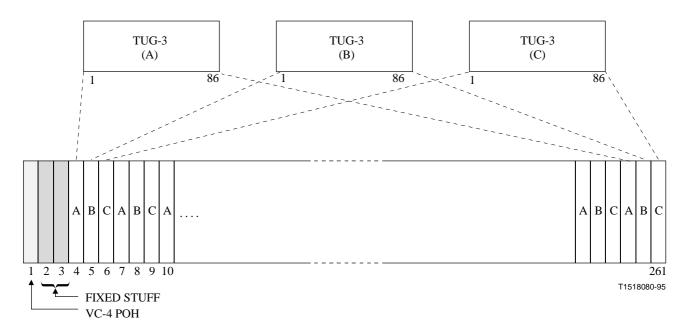

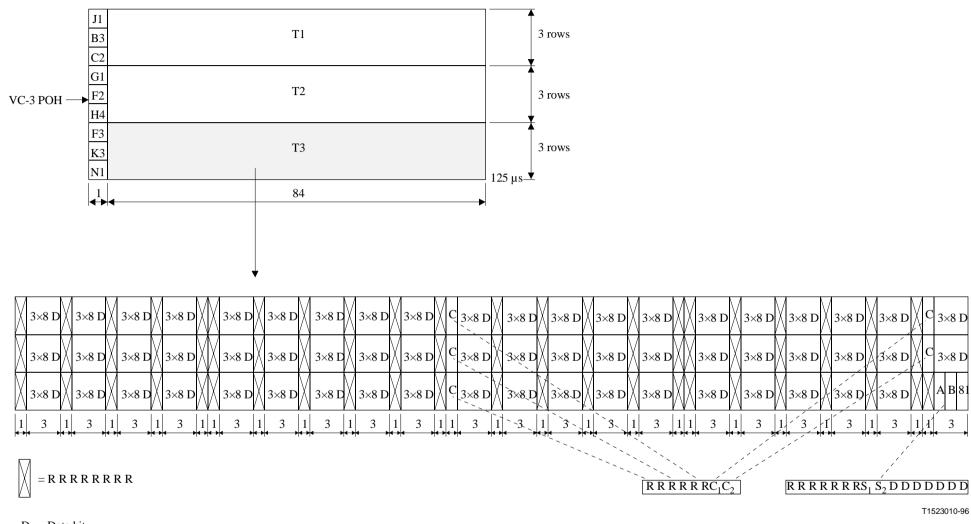

# 7.2.1 Multiplexing of Tributary Unit Group-3s (TUG-3s) into a VC-4

The arrangement of three TUG-3s multiplexed in the VC-4 is shown in Figure 7-6. The TUG-3 is a 9-row by 86-column structure. The VC-4 consists of one column of VC-4 POH, two columns of fixed stuff and a 258-column payload structure. The three TUG-3s are single byte interleaved into the 9-row by 258-column VC-4 payload structure and have a fixed phase with respect to the VC-4.

As described in 7.1, the phase of the VC-4 with respect to the AU-4 is given by the AU-4 pointer.

Figure 7-6/G.707/Y.1322 – Multiplexing of three TUG-3s into a VC-4

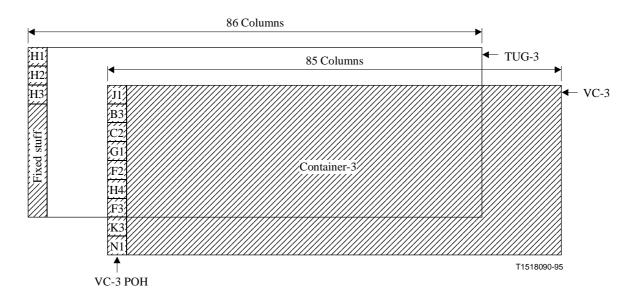

### 7.2.2 Multiplexing of a TU-3 via TUG-3

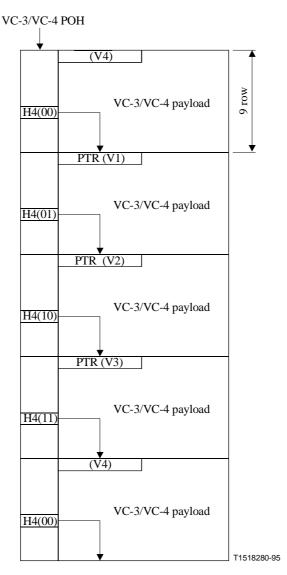

The multiplexing of a single TU-3 via the TUG-3 is depicted in Figure 7-7. The TU-3 consists of the VC-3 with a 9-byte VC-3 POH and the TU-3 pointer. The first column of the 9-row by 86-column TUG-3 is allocated to the TU-3 pointer (bytes H1, H2, H3) and fixed stuff. The phase of the VC-3 with respect to the TUG-3 is indicated by the TU-3 pointer.

Figure 7-7/G.707/Y.1322 – Multiplexing of a TU-3 via a TUG-3

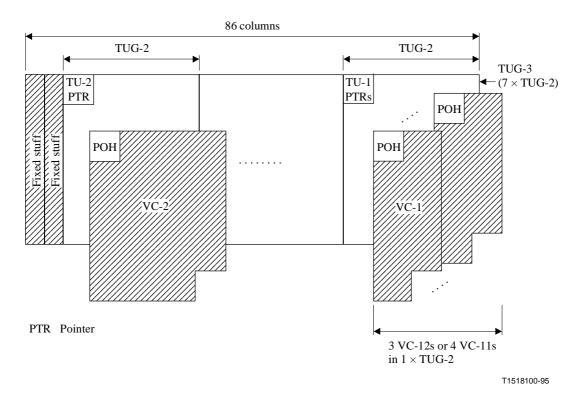

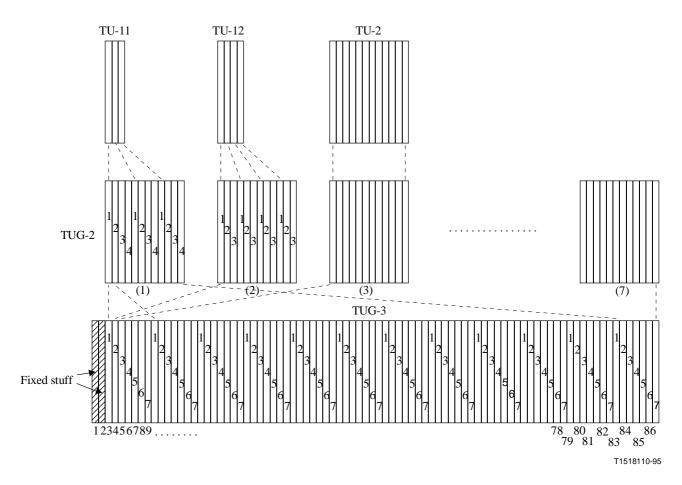

### 7.2.3 Multiplexing of TUG-2s via a TUG-3

The multiplexing structure for the TUG-2 via the TUG-3 is depicted in Figure 7-8. The TUG-3 is a 9-row by 86-column structure with the first two columns of fixed stuff.

Figure 7-8/G.707/Y.1322 – Multiplexing of seven TUG-2s via a TUG-3

A group of seven TUG-2s can be multiplexed via the TUG-3.

The arrangement of seven TUG-2s multiplexed via the TUG-3 is depicted in Figure 7-9. The TUG-2s are one-byte interleaved in the TUG-3.

Figure 7-9/G.707/Y.1322 – Multiplexing of seven TUG-2s via a TUG-3

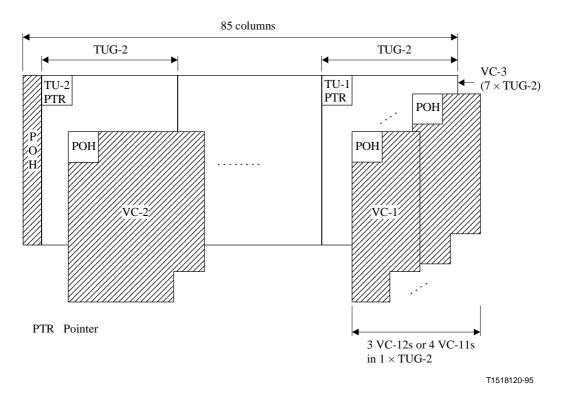

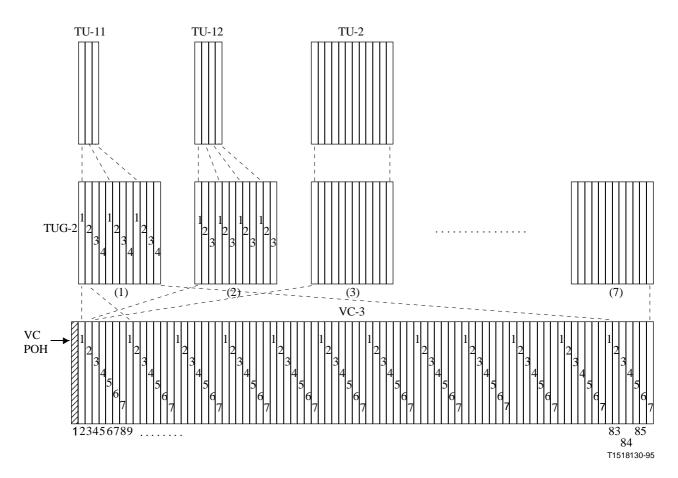

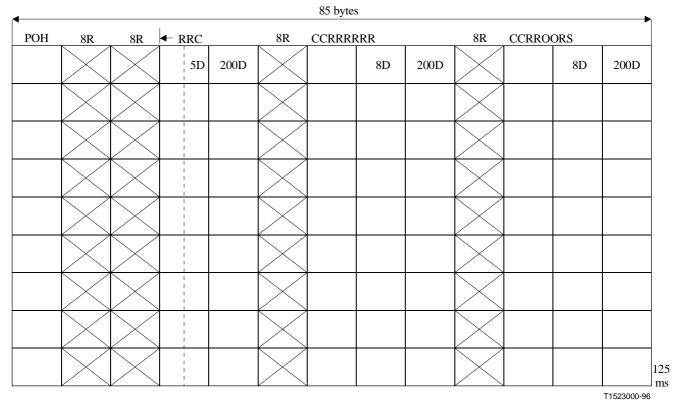

# 7.2.4 Multiplexing of TUG-2s into a VC-3

The multiplexing structure for TUG-2s into a VC-3 is depicted in Figure 7-10. The VC-3 consists of VC-3 POH and a 9-row by 84-column payload structure. A group of seven TUG-2s can be multiplexed into the VC-3.

Figure 7-10/G.707/Y.1322 – Multiplexing of seven TUG-2s into a VC-3

The arrangement of seven TUG-2s multiplexed into the VC-3 is depicted in Figure 7-11. The TUG-2s are one-byte interleaved in the VC-3. An individual TUG-2 has a fixed location in the VC-3 frame.

Figure 7-11/G.707/Y.1322 – Arrangement of seven TUG-2s multiplexed into a VC-3

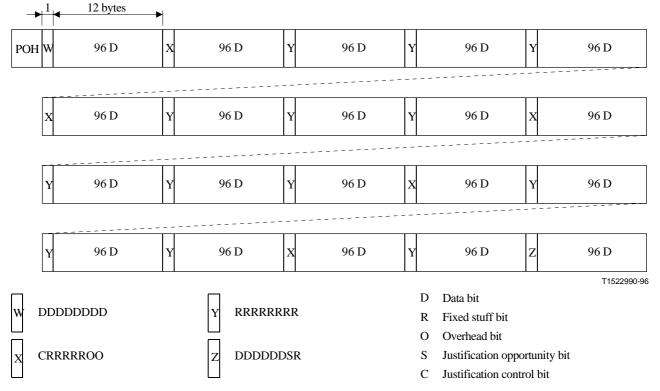

#### 7.2.5 Multiplexing of a TU-2 via TUG-2s

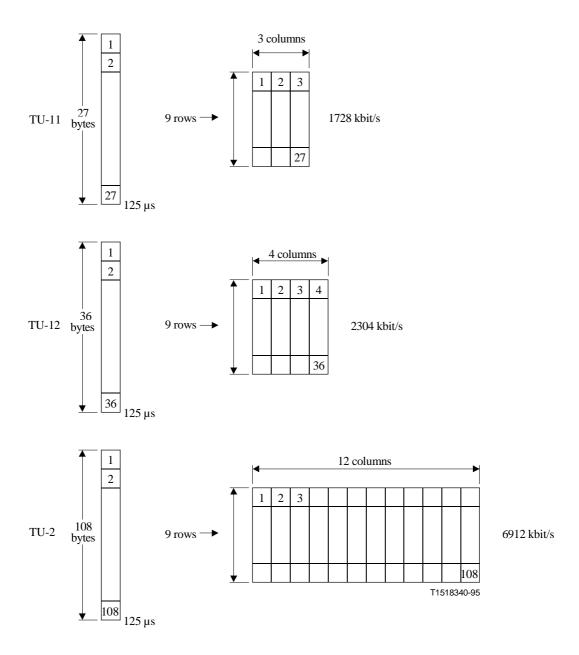

The multiplexing arrangement of a single TU-2 via the TUG-2 is depicted in Figure 7-11.

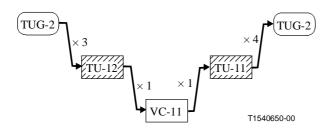

# 7.2.6 Multiplexing of TU-1s via TUG-2s

The multiplexing arrangements of four TU-11s or three TU-12s via the TUG-2 are depicted in Figure 7-11. The TU-1s are one-byte interleaved in the TUG-2.

# 7.3 AU-n/TU-n numbering scheme

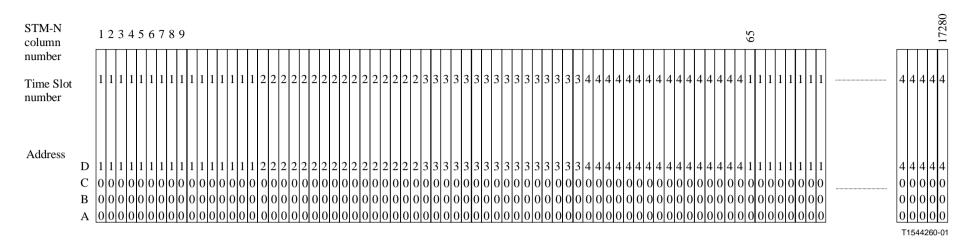

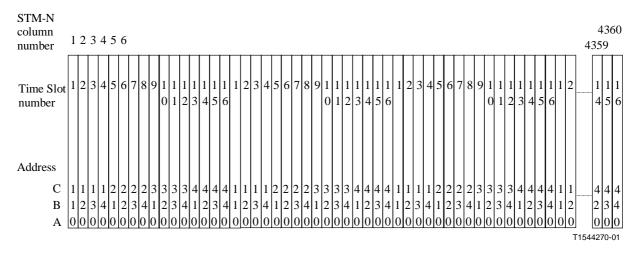

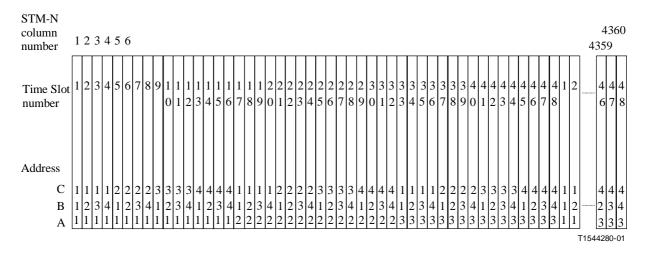

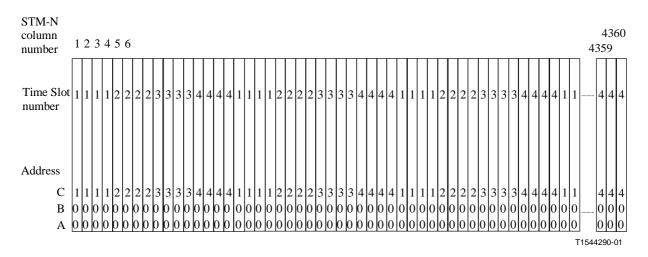

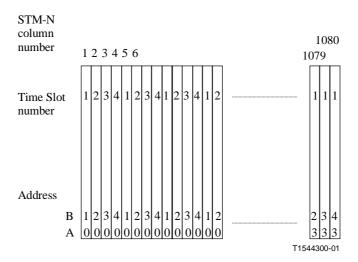

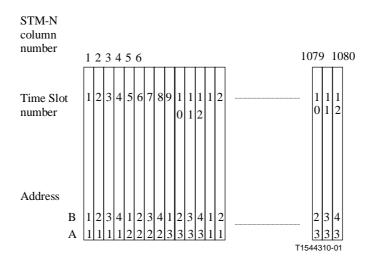

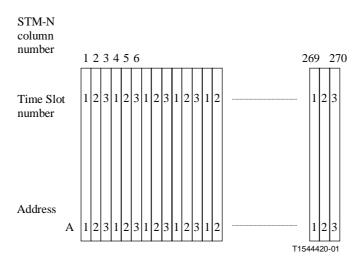

An STM-N frame comprises  $N \times 270$  columns (numbered 1 to  $N \times 270$ ). The first  $N \times 9$  columns contain the SOH and AU-4/AU-4-Xc pointer(s) with the remaining  $N \times 261$  columns containing the higher order data payload (higher order tributaries).

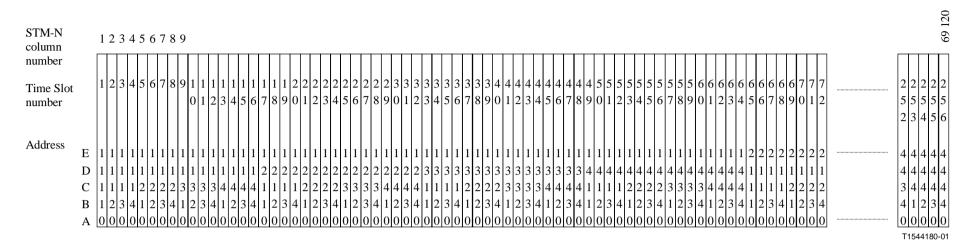

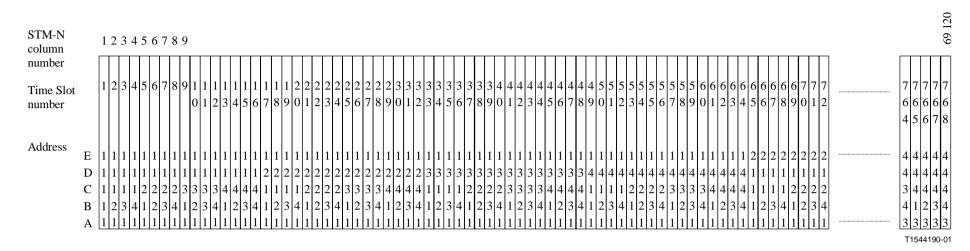

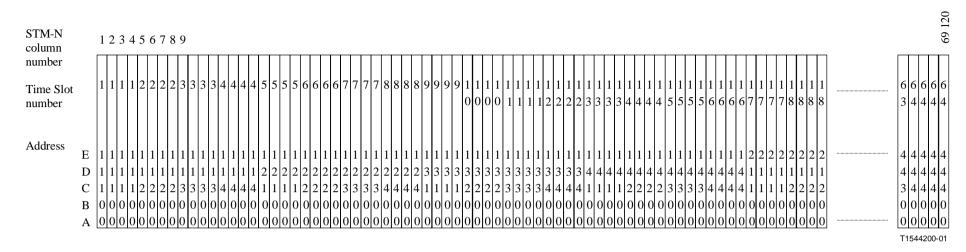

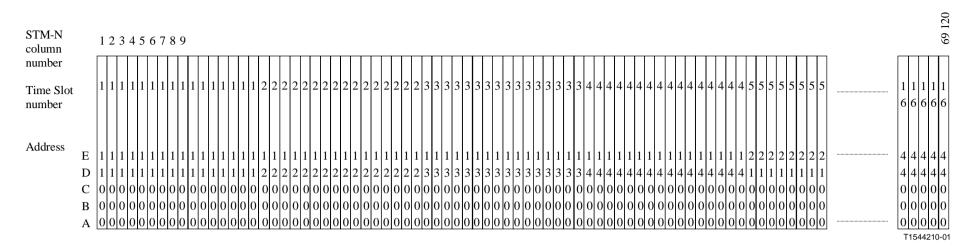

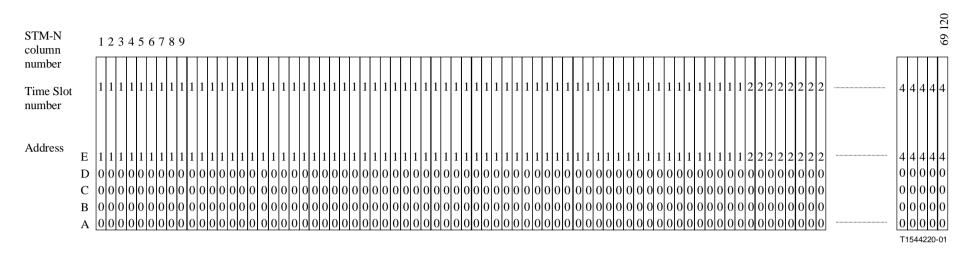

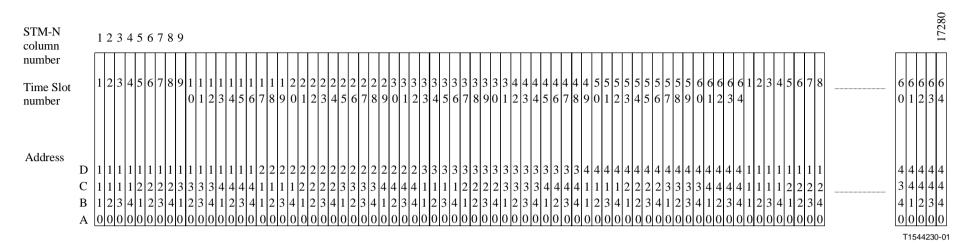

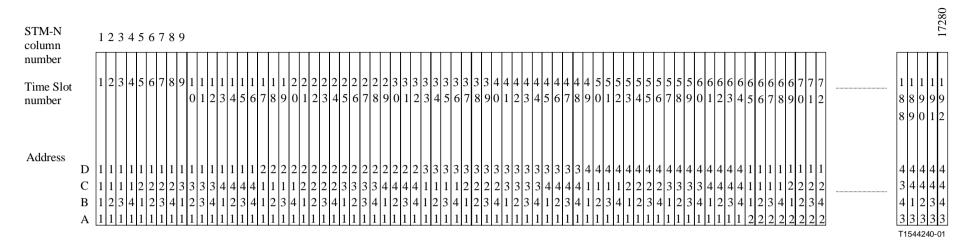

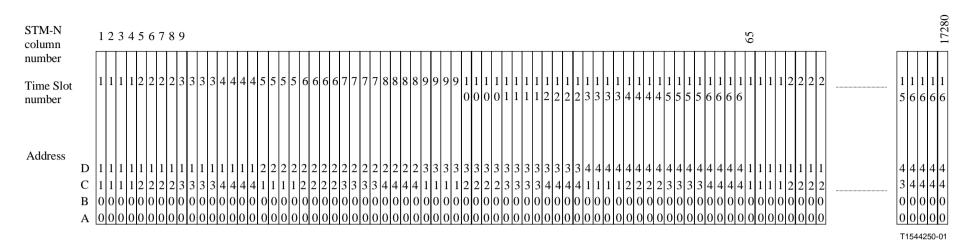

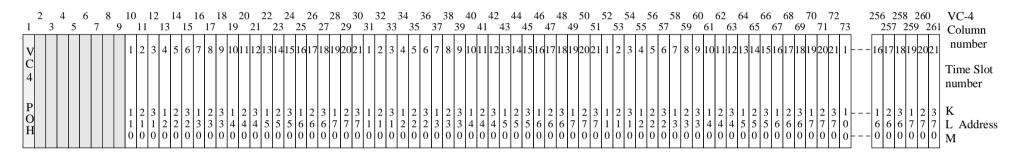

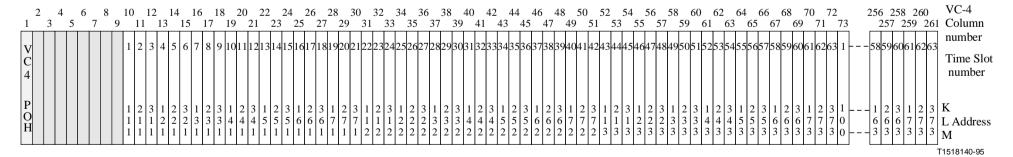

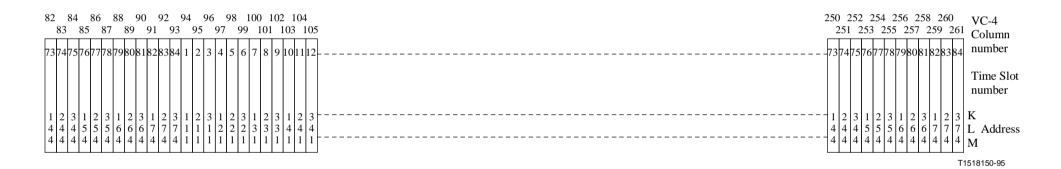

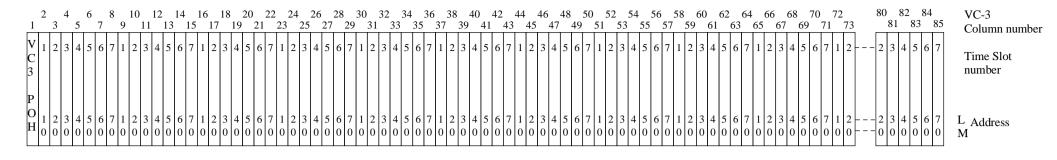

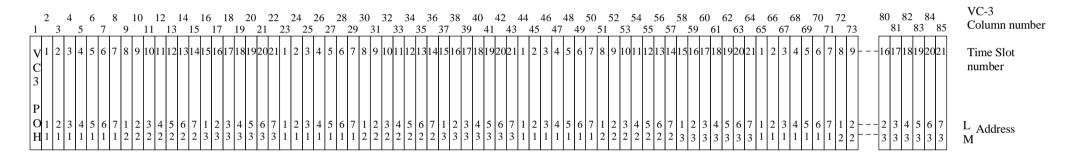

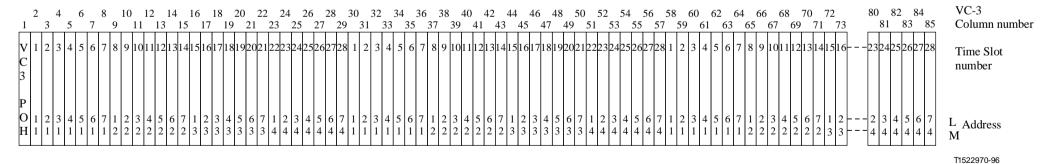

The higher order payload columns may be addressed by means of a two (B,A), three (C,B,A), four (D,C,B,A) or five (E,D,C,B,A) figure address, where A represents the AU-3 number, B the AUG-1 number, C the AUG-4 number, D the AUG-16 number and E the AUG-64 number. Refer to Figures 7-12 to 7-25.

In the case of an AU-4 structured frame, the payload columns may be addressed by means of a three figure address (K, L, M) where K represents the TUG-3 number, L the TUG-2 number, and M the TU-1 number. Refer to Figures 7-27 and 7-28 and Table 7-1. In the case of an AU-3 structured frame, only L and M coordinates are used. Refer to Figures 7-29 and Table 7-2.

In order to provide a simple and convenient means of determining the total tributary capacity, i.e. the number of lower order tributaries provided, the payload columns are allocated a Time Slot number. The number of Time Slots per tributary in each frame is determined by the payload configuration.

AU Time Slots (TS) are numbered from left to right in the STM-N as shown in Figures 7-12 to 7-26. TU Zime Slots (TS) are numbered from left to right in the VC-4/VC-3 as shown in Figures 7-27 to 7-29. For example in a VC-4, TS1 of a TU-12 starts in column 10, TS2 in column 11, and so on until TS63 is in column 72. In a VC-3, TS1 of a TU-11 starts in column 2, TS2 in column 3 ... and TS28 in column 29.

# 7.3.1 Numbering of AU-ns (VC-ns) in a STM-256

The STM-256 can comprise four AUG-64s, which shall be numbered #1 to #4:

- AUG-64 #1 is accommodated in columns 1...64, 257...320, 513...576, etc. of the STM-256;

- AUG-64 #2 is accommodated in columns 65...128, 321...384, 577...640, etc. of the STM-256;

- AUG-64 #3 is accommodated in columns 129...192, 385...448, 641...704, etc. of the STM-256;

- AUG-64 #4 is accommodated in columns 193...256, 449...512, 705...768, etc. of the STM-256.

Each AUG-64 can comprise four AUG-16s, which shall be numbered #1 to #4. Each AUG-16 can comprise four AUG-4s, which shall be numbered #1 to #4. Each AUG-4 can comprise four AUG-1s, which shall be numbered #1 to #4. Each AUG-1 can comprise three AU-3s, which shall be numbered #1 to #3.

### 7.3.1.1 Numbering of AU-4s (VC-4s) in a STM-256

Any AU-4 can be allocated a number in the form #E, #D, #C, #B, #A, where E designates the AUG-64 number (1 to 4), D designates the AUG-16 number (1 to 4), C designates the AUG-1 number (1 to 4), and A is always 0, see Figure 7-12. The location of the columns in the STM-64 occupied by AU-4 (E,D,C,B,0) is given by:

Xth column = 1 + 64\*[E-1] + 16\*[D-1] + 4\*[C-1] + [B-1] + 256\*[X-1] for X = 1 to 270.

Therefore, AU-4 (1,1,1,1,0) resides in columns 1, 257, 513, 767, ... 68 865 of the STM-256, and AU-4 (4,4,4,4,0) resides in columns 256, 512, 768, ..., 96 120 of the STM-256.

Figure 7-12/G.707/Y.1322 – AU-4 numbering scheme within an STM-256's AU pointer row and playload columns

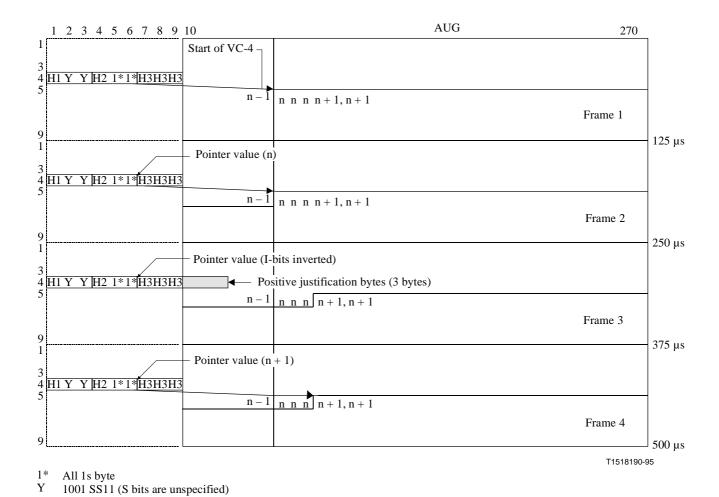

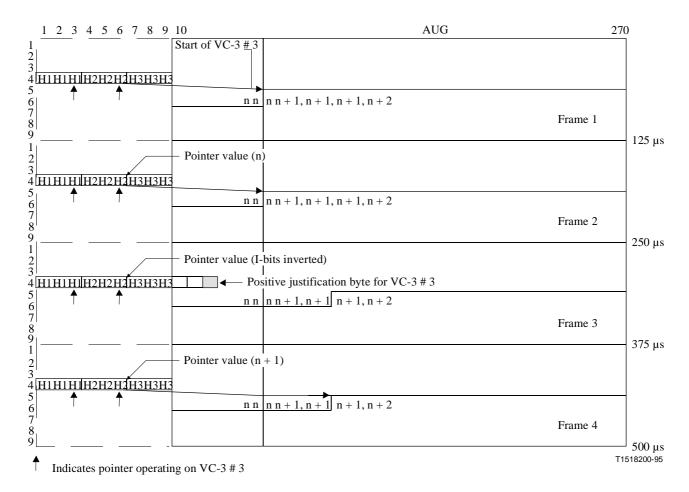

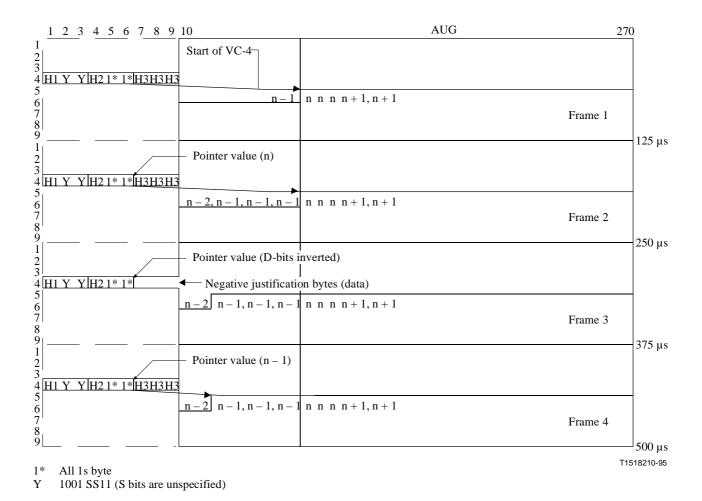

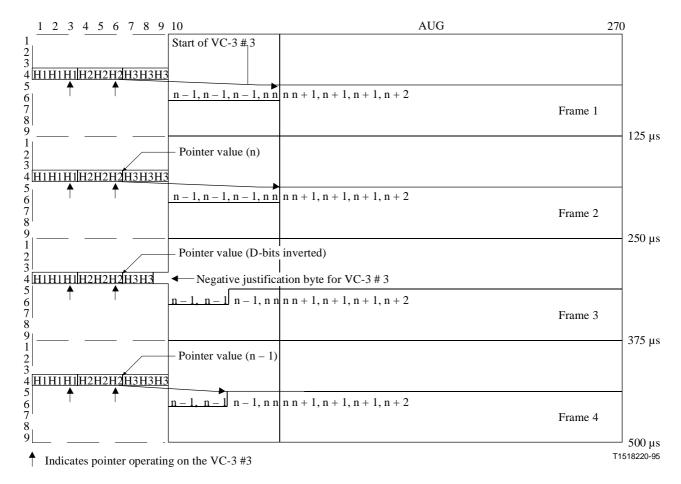

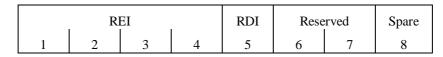

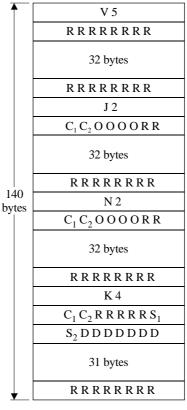

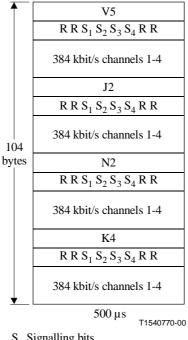

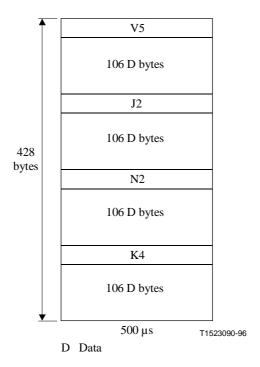

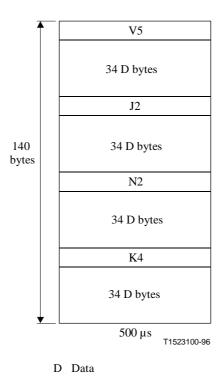

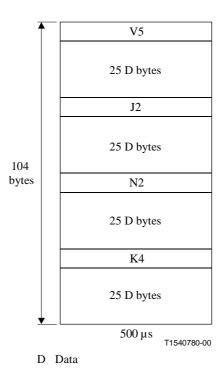

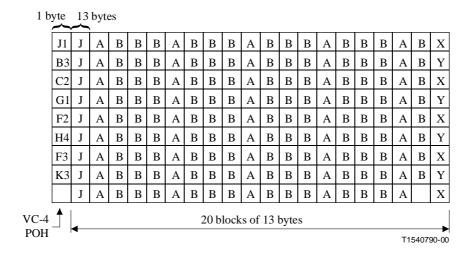

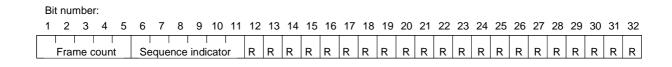

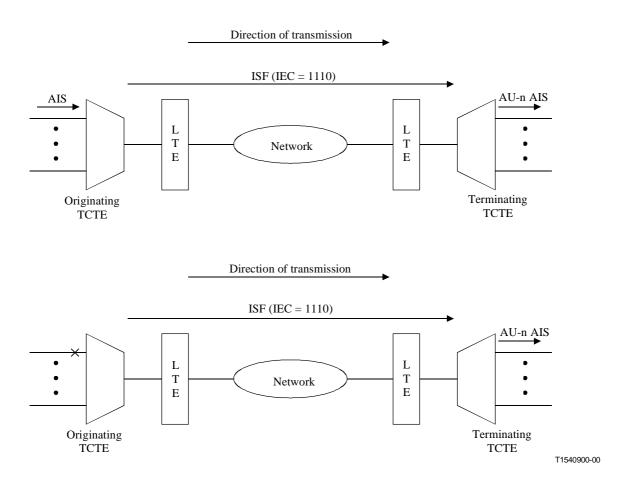

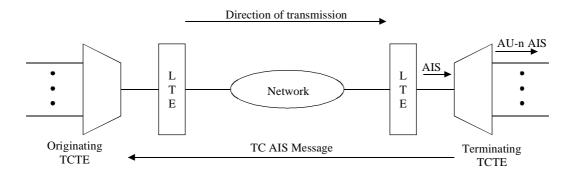

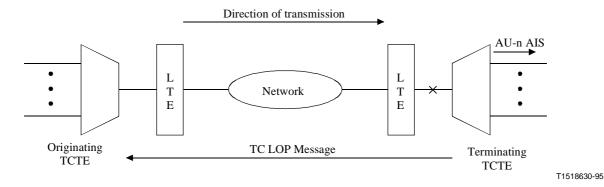

# 7.3.1.2 Numbering of AU-3s (VC-3s) in a STM-256