TELECOMMUNICATION STANDARDIZATION SECTOR OF ITU

G.704

(07/95)

# GENERAL ASPECTS OF DIGITAL TRANSMISSION SYSTEMS

SYNCHRONOUS FRAME STRUCTURES USED AT 1544, 6312, 2048, 8488 AND 44 736 kbit/s HIERARCHICAL LEVELS

ITU-T Recommendation G.704

Superseded by a more recent version

(Previously "CCITT Recommendation")

#### **FOREWORD**

The ITU-T (Telecommunication Standardization Sector) is a permanent organ of the International Telecommunication Union (ITU). The ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.

The World Telecommunication Standardization Conference (WTSC), which meets every four years, establishes the topics for study by the ITU-T Study Groups which, in their turn, produce Recommendations on these topics.

The approval of Recommendations by the Members of the ITU-T is covered by the procedure laid down in WTSC Resolution No. 1 (Helsinki, March 1-12, 1993).

ITU-T Recommendation G.704 was revised by ITU-T Study Group 15 (1993-1996) and was approved under the WTSC Resolution No. 1 procedure on the 10th of July 1995.

**NOTE**

In this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.

© ITU 199

All rights reserved. No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the ITU.

## **CONTENTS**

|    | Scope |                                                                                                 |

|----|-------|-------------------------------------------------------------------------------------------------|

|    | -     | frame structures                                                                                |

|    | 2.1   | Basic frame structure at 1544 kbit/s                                                            |

|    | 2.2   | Basic frame structure at 6312 kbit/s                                                            |

|    | 2.3   | Basic frame structure at 2048 kbit/s                                                            |

|    | 2.4   | Basic frame structure at 8448 kbit/s                                                            |

|    | 2.5   | Basic frame structure at 44 736 kbit/s                                                          |

|    | Chara | cteristics of frame structure carrying channels at various bit rates in 1544 kbit/s             |

|    | 3.1   | Interface at 1544 kbit/s carrying 64 kbit/s channels                                            |

|    | 3.2   | Interface at 1544 kbit/s carrying 32 kbit/s channel time slots                                  |

|    | 3.3   | Interface at 1544 kbit/s carrying n × 64 kbit/s                                                 |

|    | Chara | cteristics of frame structures carrying channels at various bit rates in 6312 kbit/s interfaces |

|    | 4.1   | Interface at 6312 kbit/s carrying 64 kbit/s channels                                            |

|    | 4.2   | Interfaces at 6312 kbit/s carrying other channels than 64 kbit/s                                |

|    | Chara | cteristics of frame structures carrying channels at various bit rates in 2048 kbit/s interfaces |

|    | 5.1   | Interface at 2048 kbit/s carrying 64 kbit/s channels                                            |

|    | 5.2   | Interface at 2048 kbit/s carrying n × 64 kbit/s                                                 |

|    | Chara | cteristics of frame structures carrying channels at various bit rates in 8448 kbit/s interface  |

|    | 6.1   | Interface at 8448 kbit/s carrying 64 kbit/s channels                                            |

|    | 6.2   | Interface at 8448 kbit/s carrying other channels than 64 kbit/s                                 |

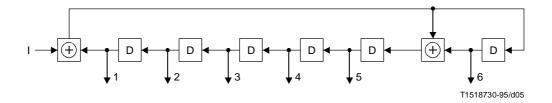

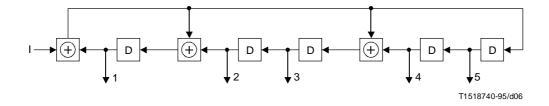

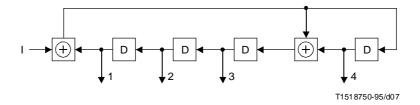

| x  | A - E | xamples of CRC implementations using shift registers                                            |

|    | A.1   | CRC-6 procedure for interface at 1544 kbit/s                                                    |

|    | A.2   | CRC-5 procedure for interface at 6312 kbit/s                                                    |

|    | A.3   | CRC-4 procedure for interface at 2048kbit/s                                                     |

| ex | B – A | lphabetical list of abbreviations used in this Recommendation                                   |

## **SUMMARY**

This Recommendation gives functional characteristics of interfaces associated with:

- network nodes, in particular, synchronous digital multiplex equipment and digital exchanges in IDNs for telephony and ISDNs; and

- PCM multiplexing equipment.

Clause 2 deals with basic frame structures, including details of frame length, frame alignment signals, Cyclic Redundancy Check (CRC) procedures and other basic information.

Clauses 3 to 6 contain more specific information about how certain channels at 64 kbit/s and at other bit rates are accommodated within the basic frame structures described in 2.

**Recommendation G.704**

## SYNCHRONOUS FRAME STRUCTURES USED AT 1544, 6312, 2048, 8488 AND 44 736 kbit/s HIERARCHICAL LEVELS

(Malaga-Torremolinos, 1984; amended at Melbourne, 1988; revised in 1990 and 1995)

## 1 Scope

This Recommendation gives functional characteristics of interfaces associated with:

- network nodes, in particular, synchronous digital multiplex equipment and digital exchanges in IDNs for telephony and ISDNs; and

- PCM multiplexing equipment.

Clause 2 deals with basic frame structures, including details of frame length, frame alignment signals, Cyclic Redundancy Check (CRC) procedures and other basic information.

Clauses 3 to 6 contain more specific information about how certain channels at 64 kbit/s and at other bit rates are accommodated within the basic frame structures described in 2.

Electrical characteristics for these interfaces are defined in Recommendation G.703.

#### NOTES

- 1 This Recommendation does not necessarily apply to those cases where the signals that cross the interfaces are devoted to non-switched connections, such as those for the transport of encoded wideband signals (e.g. broadcast TV signals or multiplexed sound-program signals which need not be individually routed via the ISDN), see also Annex A/G.702.

- 2 The frame structures recommended in this Recommendation do not apply to certain maintenance signals, such as the all 1s signals transmitted during fault conditions or other signals transmitted during out-of-service conditions.

- 3 Frame structures associated with digital multiplexing equipments using justification are covered in each corresponding equipment Recommendation.

- 4 Inclusion of channel structures at other bit rates than 64 kbit/s is a matter for further study. Recommendations G.761 and G.763 dealing with the characteristics of PCM/ADPCM transcoding equipment contain information about channel structures at 32 kbit/s. The more general use of those particular structures is a subject of further study.

### **2** Basic frame structures

## 2.1 Basic frame structure at 1544 kbit/s

## 2.1.1 Frame length

193 bits, numbered 1 to 193. The frame repetition rate is 8000 Hz.

#### 2.1.2 F-bit

The first bit of a frame is designated an F-bit, and is used for such purposes as frame alignment, performance monitoring and providing a data link.

## 2.1.3 Allocation of F-bit

Two alternative methods as given in Tables 1 and 3 for allocation of F-bits are recommended.

#### 2.1.3.1 Method 1: Twenty-four-frame multiframe

Allocation of the F-bit to the multiframe alignment signal, the CRC check bits and the data link is given in Table 1.

TABLE 1/G.704

#### Multiframe structure for the 24 frame multiframe

|                      |                      | F-bit |         |                |                                    |                                 |                           |

|----------------------|----------------------|-------|---------|----------------|------------------------------------|---------------------------------|---------------------------|

| Frame<br>number      | Bit number<br>within | As    | ssignme | ents           | Bit number(s) time                 | Signalling channel              |                           |

| within<br>multiframe | multiframe           | FAS   | DL      | CRC            | For character signal <sup>a)</sup> | For<br>signalling <sup>a)</sup> | designation <sup>a)</sup> |

| 1                    | 1                    | _     | m       | _              | 1-8                                | _                               |                           |

| 2                    | 194                  | _     | _       | $e_1$          | 1-8                                | _                               |                           |

| 3                    | 387                  | _     | m       | _              | 1-8                                | _                               |                           |

| 4                    | 580                  | 0     | _       | _              | 1-8                                | _                               |                           |

| 5                    | 773                  | _     | m       | _              | 1-8                                | _                               |                           |

| 6                    | 966                  | _     | _       | $e_2$          | 1-7                                | 8                               | A                         |

| 7                    | 1159                 | _     | m       | _              | 1-8                                | _                               |                           |

| 8                    | 1352                 | 0     | _       | _              | 1-8                                | _                               |                           |

| 9                    | 1545                 | _     | m       | _              | 1-8                                | _                               |                           |

| 10                   | 1738                 | _     | _       | $e_3$          | 1-8                                | _                               |                           |

| 11                   | 1931                 | _     | m       | _              | 1-8                                | _                               |                           |

| 12                   | 2124                 | 1     | _       | _              | 1-7                                | 8                               | В                         |

| 13                   | 2317                 | _     | m       | _              | 1-8                                | _                               |                           |

| 14                   | 2510                 | _     | _       | $e_4$          | 1-8                                | _                               |                           |

| 15                   | 2703                 | _     | m       | _              | 1-8                                | _                               |                           |

| 16                   | 2896                 | 0     | _       | _              | 1-8                                | _                               |                           |

| 17                   | 3089                 | _     | m       | _              | 1-8                                | _                               |                           |

| 18                   | 3282                 | _     | _       | e <sub>5</sub> | 1-7                                | 8                               | С                         |

| 19                   | 3475                 | _     | m       | _              | 1-8                                | _                               |                           |

| 20                   | 3668                 | 1     | _       | _              | 1-8                                | _                               |                           |

| 21                   | 3861                 | _     | m       | _              | 1-8                                | _                               |                           |

| 22                   | 4054                 | _     | _       | e <sub>6</sub> | 1-8                                | _                               |                           |

| 23                   | 4247                 | _     | m       | _              | 1-8                                | _                               |                           |

| 24                   | 4440                 | 1     | _       | _              | 1-7                                | 8                               | D                         |

FAS Frame alignment signal (... 001011...).

DL 4 kbit/s data link (message bits m).

CRC CRC-6 block check field (check bits  $e_1$  to  $e_6$ ).

a) Only applicable in the case of channel associated signalling (see 3.1.3.2).

### 2.1.3.1.1 Multiframe alignment signal

The F-bit of every fourth frame forms the pattern 001011 . . . 001011. This multiframe alignment signal is used to identify where each particular frame is located within the multiframe in order to extract the cyclic redundancy check code, CRC-6, and the data link information, as well as to identify those frames that contain signalling (frames 6, 12, 18 and 24), if channel associated signalling is used.

### 2.1.3.1.2 Cyclic Redundancy Check (CRC)

The CRC-6 is a method of performance monitoring that is contained within the F-bit position of frames 2, 6, 10, 14 18 and 22 of every multiframe (see Table 1).

The CRC-6 message block check bits  $e_1$ ,  $e_2$ ,  $e_3$ ,  $e_4$ ,  $e_5$ , and  $e_6$  are contained within multiframe bits 194, 966, 1738, 2510, 3282 and 4054 respectively, as shown in Table 1. The CRC-6 Message Block (CMB) is a sequence of 4632 serial bits that is coincident with a multiframe. By definition, CMB N begins at bit position 1 of multiframe N and ends at bit position 4632 of multiframe N. The first transmitted CRC bit of a multiframe is the most significant bit of the CMB polynomial.

In calculating the CRC-6 bits, the F-bits are replaced by binary 1s. All information in the other bit positions will be identical to the information in the corresponding multiframe bit positions.

The check-bit sequence  $e_1$  through  $e_6$  transmitted in multiframe N+1, is the remainder after multiplication by  $x^6$  and then division (modulo 2) by the generator polynomial  $x^6+x+1$  of the polynomial corresponding to CMB N. The first check bit  $(e_1)$  is the most significant bit of the remainder; the last check bit  $(e_6)$  is the least significant bit of the remainder. Each multiframe contains the CRC-6 check bits generated for the preceding CMB.

At the receiver, the received CMB, with each F-bit having first been replaced by a binary 1, is acted upon by the multiplication/division process described above. The resulting remainder is compared on a bit-by-bit basis, with the CRC-6 check bits contained in the subsequently received multiframe. The compared check bits will be identical in the absence of transmission errors.

### 2.1.3.1.3 4 kbit/s data link

Beginning with frame 1 of the multiframe (see Table 1), the first bit of every other frame is part of the 4 kbit/s data link. This data link provides a communication path between primary hierarchical level terminals. In prioritized order the data link will contain priority operations messages, other maintenance or operations messages, periodic terminal performance reports, or an idle data link sequence.

- Both categories of operations messages are transmitted in the form of 16-bit sequences of the form 111111110P<sub>1</sub>P<sub>2</sub>P<sub>3</sub>P<sub>4</sub>P<sub>5</sub>P<sub>6</sub>0, where the particular message is coded by the six bits P<sub>1</sub> through P<sub>6</sub>, permitting up to 64 distinct messages. Designated sequences and their functional uses are listed in Table 2. Use of sequences not shown in the table is for further study.

- Periodic terminal performance reports are formatted using the unnumbered, unacknowledged frame

option of Q.921/LAPD, as described in 2.1.3.1.3.3. Transmission of any of the assigned 16-bit sequences

terminates any processing of a (lower priority) performance report that might be in progress, as seven or

more consecutive ones are recognized in Recommendation Q.921 as an abort command.

- The idle data link sequence is a continuous repetition of the pattern 011111110.

- The transmission of Loss of Frame Alignment (LFA) also called Remote Alarm Indication (RAI) and idle data link sequence in m-bits is mandatory. The other use of m-bits is optional, but when a function other than mandatory functions is used, the specification described here should be applied to guarantee the interworking of terminals.

NOTE - Some functions, such as PRM, are mandatory in some national standard.

#### 2.1.3.1.3.1 Priority operations messages

Priority messages are transmitted as continuous repetitions of the designated sequence for the duration of the condition initiating the message. It is permissible to interrupt the continuous repetition of the sequence for an interval not to exceed 100 ms not more then once per second, in order to send one or more other maintenance messages.

Two priority messages have been defined:

- After an LFA condition is detected at local end A, the LFA sequence is transmitted to remote end B for the duration of the LFA condition, but not less than one second;

- a loopback control signal that is used in those applications requiring a continuous enabling signal during operations in a looped condition.

TABLE 2/G.704

## Assigned operations data link messages

| Priority Messages                                 |                   |  |  |  |  |

|---------------------------------------------------|-------------------|--|--|--|--|

| Function                                          | Codeword          |  |  |  |  |

| LFA (also called RAI)                             | 11111111 00000000 |  |  |  |  |

| Loopback Retention                                | 11111111 01010100 |  |  |  |  |

| Other Operation Messages                          |                   |  |  |  |  |

| Category                                          |                   |  |  |  |  |

| Function                                          | Codeword          |  |  |  |  |

| Loopbacks:                                        |                   |  |  |  |  |

| Customer Installation Type A Operate              | 11111111 01110000 |  |  |  |  |

| Customer Installation Type A Release              | 11111111 00011100 |  |  |  |  |

| Customer Installation Type B Operate              | 11111111 00000100 |  |  |  |  |

| Customer Installation Type C Operate              | 11111111 00000100 |  |  |  |  |

| Payload Operate                                   | 11111111 00101000 |  |  |  |  |

| Payload Release                                   | 11111111 01001100 |  |  |  |  |

| Network Type A Operate                            | 11111111 01001000 |  |  |  |  |

| Universal Release                                 | 11111111 00100100 |  |  |  |  |

|                                                   |                   |  |  |  |  |

| Protection switching:                             | 11111111 01000010 |  |  |  |  |

| Operate Line 2                                    |                   |  |  |  |  |

| Operate Line 2                                    | 11111111 00100010 |  |  |  |  |

| Operate Line 3                                    | 11111111 01100010 |  |  |  |  |

| Operate Line 4                                    | 11111111 00010010 |  |  |  |  |

| Operate Line 5                                    | 11111111 01010010 |  |  |  |  |

| Operate Line 6                                    | 11111111 00110010 |  |  |  |  |

| Operate Line 7                                    | 11111111 01110010 |  |  |  |  |

| Operate Line 8                                    | 11111111 00001010 |  |  |  |  |

| Operate Line 9                                    | 11111111 01001010 |  |  |  |  |

| Operate Line 10                                   | 11111111 00101010 |  |  |  |  |

| Operate Line 11                                   | 11111111 01101010 |  |  |  |  |

| Operate Line 12                                   | 11111111 00011010 |  |  |  |  |

| Operate Line 13                                   | 11111111 01011010 |  |  |  |  |

| Operate Line 14                                   | 11111111 00111010 |  |  |  |  |

| Operate Line 15                                   | 11111111 01111010 |  |  |  |  |

| Operate Line 16                                   | 11111111 00000110 |  |  |  |  |

| Operate Line 17                                   | 11111111 01000110 |  |  |  |  |

| Operate Line 18                                   | 11111111 00100110 |  |  |  |  |

| Operate Line 19                                   | 11111111 01100110 |  |  |  |  |

| Operate Line 20                                   | 11111111 00010110 |  |  |  |  |

| Operate Line 21                                   | 11111111 01010110 |  |  |  |  |

| Operate Line 22                                   | 11111111 00110110 |  |  |  |  |

| Operate Line 23                                   | 11111111 01110110 |  |  |  |  |

| Operate Line 24                                   | 11111111 00001110 |  |  |  |  |

| Operate Line 25                                   | 11111111 01001110 |  |  |  |  |

| Operate Line 26                                   | 11111111 00101110 |  |  |  |  |

| Operate Line 27                                   | 11111111 01101110 |  |  |  |  |

| Acknowledge protection switching action           | 11111111 00011000 |  |  |  |  |

| Release protection switch                         | 11111111 01100100 |  |  |  |  |

| Synchronization:                                  |                   |  |  |  |  |

| Reserved – for further study                      | 11111111 00001100 |  |  |  |  |

| Reserved – for further study                      | 11111111 00110000 |  |  |  |  |

| Reserved – for further study                      | 11111111 01000100 |  |  |  |  |

| Reserved – for further study                      | 11111111 00010100 |  |  |  |  |

| NOTE – Unassigned messages are for further study. |                   |  |  |  |  |

### 2.1.3.1.3.2 Other maintenance or operations messages

Other maintenance and operations messages are defined in three general categories of loopbacks, protection switching, and synchronization:

- Four types of line loopbacks (in which the entire signal including F-bits is returned to the direction sending the initiation signal) are recognized, three on customer premises and one within the network. Each has a defined sequence to operate. One has a unique sequence to release, while all share a common release sequence. A payload loopback (in which only the information bits in a frame are returned) is defined for implementation in a primary hierarchical level terminal. The F-bits in the return direction are generated by the equipment performing loopback. Unique operate and release sequences are defined. The payload loopback also responds to the universal release sequence.

- For protection switching, 27 sequences are defined to activate protection switching, one sequence is defined to release a protection switch, and one sequence is defined to acknowledge a protection switching action. Activation sequences are of the form 111111110P<sub>1</sub>P<sub>2</sub>P<sub>3</sub>P<sub>4</sub>P<sub>5</sub>10, where the bit sequence P<sub>1</sub>P<sub>2</sub>P<sub>3</sub>P<sub>4</sub>P<sub>5</sub> is the binary representation of the decimal line number x of the line to be switched to the protection line. In these sequences, P<sub>1</sub> is the least significant bit of the binary representation.

- Four messages are reserved for synchronization-related operations. The details are for further study.

## 2.1.3.1.3.3 Performance report from a primary hierarchical level terminal

Performance verification is based on the calculation of CRC check sums and comparison with those received in bits  $e_1$  through  $e_6$  as described in 2.1.3.1.2. These counts, and counts of other events available at the receiving terminal are collected for contiguous one second periods, summarized and formatted into a performance report message that is returned once each second to the originating terminal in the data link for the opposite direction of transmission.

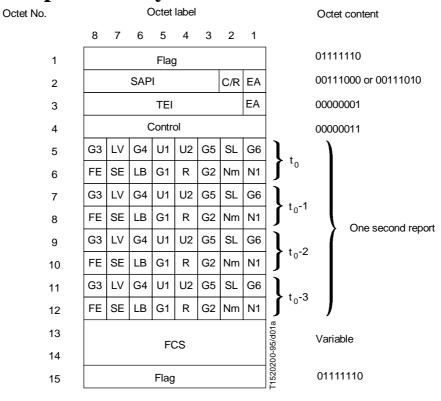

The overall length of the Q.921 frame, including opening and closing flags is 15 bytes. Data on the four most recent seconds is structured into an eight-octet information field as shown in Figure 1. At the end of each one second accumulation interval, a modulo 4 counter is incremented and the most recent data is examined to set the performance bits in the  $t_0$  octets (octets 5 and 6 of Figure 1). Data from octets 5 and 6 of the previous performance report are moved to octets 7 and 8 of the current report; previous octets 7 and 8 get moved to current octets 9 and 10; previous octets 9 and 10 get moved to current octets 11 and 12, while the previous octets 11 and 12 are discarded.

NOTE 1 – The SAPI value 14 (decimal) is reserved in the 4 kbit/s data link for use in the performance report. The C/R is set to 1 if the terminal originating the report is within the network; the bit is set to 0 if the report originates from within a customer installation. The TEI is set to all zeros. The Extended Address (EA) is always set to 0 in the octet containing the SAPI, and set to 1 in the octet containing the TEI.

The specific values of C/R and TEI defined here are used at the Network Node Interfaces (NNI). Other specific values may be used at local access portion and User-Network Interface (UNI) (see Recommendations G.963 and I.431).

NOTE 2 – The events tracked for the performance report and their definitions are:

- CRC error event The occurrence of a received set of check bits that differ from the locally generated code.

- Severely errored framing event The occurrence of two or more errors in the multiframe alignment sequence within a 3 ms period. Contiguous 3 ms periods shall be examined.

- Frame synchronization bit error event The occurrence of an error in the multiframe alignment signal.

- Line code violation The occurrence of a bipolar violation.

- Controlled slip event The occurrence of a controlled frame slip.

- Active payload loopback The existence of an operative payload loopback in the terminal originating the

performance report.

| Address<br>00111000<br>00111010<br>00000001                                                                                                            | Interpretation SAPI = 14, C/R = 0 (CI) EA = 0 SAPI = 14, C/R = 1 (Carrier) EA = 0 TEI = 0, EA = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control 00000011 One second report G1 = 1 G2 = 1 G3 = 1 G4 = 1 G5 = 1 G6 = 1 SE = 1 FE = 1 LV = 1 SL = 1 LB = 1 U1, U2 = 0 R = 0 NmN1 = 00, 01, 10, 11 | Interpretation Unacknowledged Information Transfer Interpretation CRC Error Event = 1 $1 < \text{CRC Error Event} \le 5$ $5 < \text{CRC Error Event} \le 10$ $10 < \text{CRC Error Event} \le 100$ $10 < \text{CRC Error Event} \le 319$ CRC Error Event $\ge 320$ Severely-Errored Framing Event $\ge 1$ (FE shall = 0) Frame Synchronization Bit Error Event $\ge 1$ (SE shall = 0) Line Code Violation Event $\ge 1$ Slip Event $\ge 1$ Payload Loopback Activated Under Study for Synchronization Reserved (Default value is 0) One-second report modulo 4 counter |

| FCS<br>Variable                                                                                                                                        | Interpretation CRC16 Frame Check Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

NOTE – Rightmost bit transmitted first.

### FIGURE 1/G.704

## Performance report structure at NNI

### 2.1.3.2 Method 2: Twelve-frame multiframe

Allocation of the F-bit to the frame alignment signal, multiframe alignment signal and signalling is given in Table 3.

TABLE 3/G.704

#### Allocation of F-bits for the 12-frame multiframe

| Frame number                                    | Frame alignment signal | Multiframe alignment signal or signalling |  |  |  |  |  |  |

|-------------------------------------------------|------------------------|-------------------------------------------|--|--|--|--|--|--|

| 1                                               | 1                      | -                                         |  |  |  |  |  |  |

| 2                                               | _                      | S                                         |  |  |  |  |  |  |

| 3                                               | 0                      | _                                         |  |  |  |  |  |  |

| 4                                               | 4 – S                  |                                           |  |  |  |  |  |  |

| NOTE – For multiframe structure, see 3.1.3.2.2. |                        |                                           |  |  |  |  |  |  |

### 2.2 Basic frame structure at 6312 kbit/s

## 2.2.1 Frame length

The number of bits per frame is 789. The frame repetition rate is 8000 Hz.

#### 2.2.2 F-bits

The last five bits of a frame are designated as F-bits, and are used for such purposes as frame alignment, performance monitoring and providing a data link.

#### 2.2.3 Allocation of F-bits

Allocation of the F-bits is given in Table 4.

TABLE 4/G.704

## Allocation of F-bits

| Frame number | Bit number |       |                |       |                |  |  |

|--------------|------------|-------|----------------|-------|----------------|--|--|

|              | 785        | 786   | 787            | 788   | 789            |  |  |

| 1            | 1          | 1     | 0              | 0     | m              |  |  |

| 2            | 1          | 0     | 1              | 0     | 0              |  |  |

| 3            | X          | Х     | Х              | a     | m              |  |  |

| 4            | $e_1$      | $e_2$ | e <sub>3</sub> | $e_4$ | e <sub>5</sub> |  |  |

m Data link bit.

#### 2.2.3.1 Frame alignment signal

The frame and multiframe alignment signal is 110010100, and is carried on the F-bits in frames 1 and 2, excluding bit 789 of frame 1.

a Remote end alarm bit (1 state = alarm, 0 state = no alarm).

$e_i$  CRC-5 check bit (i = 1 to 5).

x Spare bits, to be set at state 1 if not used.

### 2.2.3.2 Cyclic redundancy check

The Cyclic Redundancy Check 5 (CRC-5) Message Block (CMB) is a sequence of 3151 serial bits which starts at bit number 1 of frame number 1 and ends at bit number 784 of frame number 4. The CRC-5 message block check bits e<sub>1</sub>, e<sub>2</sub>, e<sub>3</sub>, e<sub>4</sub> and e<sub>5</sub> occupy the last five bits of the multiframe as shown in Table 4.

The check-bit sequence  $e_1$  through  $e_5$  transmitted in multiframe N is the remainder after multiplication by  $x^5$  and then division (modulo 2) by the generator polynomial  $x^5 + x^4 + x^2 + 1$  of the polynomial corresponding to CMB N. The first check bit  $(e_1)$  is the most significant bit of the remainder; the last check bit  $(e_5)$  is the least significant bit of the remainder. Each multiframe contains the CRC-5 check bits generated for the corresponding CMB.

At the receiver the incoming sequence of 3156 serial bits (i.e. 3151 bits of CMB and 5 CRC bits), when divided by the generator polynomials, will result in a remainder of 00000 in the absence of transmission errors.

#### 2.2.3.3 4 kbit/s data link

The bit m shown in Table 4 is used as a data link bit. These bits provide 4 kbit/s data transmission capability associated with the 6312 kbit/s digital path.

#### 2.2.3.4 Remote end alarm indication

After a loss of frame alignment condition is detected at local end A, remote end alarm signal bit a, shown in Table 4, will be transmitted to remote end B.

### 2.3 Basic frame structure at 2048 kbit/s

#### 2.3.1 Frame length

256 bits, numbered 1 to 256. The frame repetition rate is 8000 Hz.

#### 2.3.2 Allocation of bits number 1 to 8 of the frame

Allocation of bits number 1 to 8 of the frame is shown in Table 5A.

## 2.3.3 Description of the CRC-4 procedure in bit 1 of the frame

#### 2.3.3.1 Special use of bit 1 of the frame

Where there is a need to provide additional protection against simulation of the frame alignment signal, and/or where there is a need for an enhanced error monitoring capability, then bit 1 should be used for a cyclic redundancy check-4 (CRC-4) procedure as detailed below.

NOTE – Equipment incorporating the CRC-4 procedure should be designed to be capable of interworking with equipment which does not incorporate the CRC-4 procedure, that is, an ability to continue to provide service (traffic) between equipments with and without a CRC-4 capability. This can be achieved either manually (e.g. by straps) or automatically.

- For the manual case, the equipment incorporating the CRC-4 procedure should be capable of fixing bit 1 of the frame to the binary "1" state (see Table 5A, Note 1).

- For the automatic case, this can be achieved at the equipment having the CRC-4 capability either:

- as a "higher-layer" function under the control of a network management facility (e.g. a TMN) the details are for further study; or

- as a "lower-layer" function using a modified CRC-4 multiframe alignment algorithm as described in Annex B/G.706.

- **2.3.3.2** The allocation of bits 1 to 8 of the frame is shown in Table 5B for a complete CRC-4 multiframe.

- **2.3.3.3** Each CRC-4 multiframe, which is composed of 16 frames numbered 0 to 15, is divided into two 8-frame Sub-Multiframes (SMF), designated SMF I and SMF II which signifies their respective order of occurrence within the CRC-4 multiframe structure. The SMF is the Cyclic Redundancy Check-4 (CRC-4) block size (i.e. 2048 bits).

The CRC-4 multiframe structure is not related to the possible use of a multiframe structure in 64 kbit/s channel time slot 16 (see 5.1.3.2).

TABLE 5A/G.704

#### Allocation of bits 1 to 8 of the frame

| Bit number                               | 1              | 2                                                                   | 3        | 4 | 5 | 6               | 7 | 8 |

|------------------------------------------|----------------|---------------------------------------------------------------------|----------|---|---|-----------------|---|---|

| Alternate frames                         |                |                                                                     |          |   |   |                 |   |   |

| Frame containing the                     | S <sub>i</sub> | 0                                                                   | 0        | 1 | 1 | 0               | 1 | 1 |

| frame alignment signal                   | (Note 1)       | Frame alignment signal                                              |          |   |   |                 |   |   |

| Frame not containing the frame alignment | Si             | 1 A S <sub>a4</sub> S <sub>a5</sub> S <sub>a6</sub> S <sub>a7</sub> |          |   |   | S <sub>a8</sub> |   |   |

| signal                                   | (Note 1)       | (Note 2)                                                            | (Note 3) |   |   | (Note 4)        |   |   |

#### NOTES

- $S_i$  = Bits reserved for international use. One specific use is described in 2.3.3. Other possible uses may be defined at a later stage. If no use is realized, these bits should be fixed at 1 on digital paths crossing an international border. However, they may be used nationally if the digital path does not cross a border.

- 2 The bit is fixed at 1 to assist in avoiding simulations of the frame alignment signal.

- 3 A = Remote alarm indication. In undisturbed operation, set to 0; in alarm condition, set to 1.

- 4  $S_{a4}$  to  $S_{a8}$  = Additional spare bits whose use may be as follows:

- i) Bits  $S_{a4}$  to  $S_{a8}$  may be recommended by ITU-T for use in specific point-to-point applications (e.g. transcoder equipments conforming to Recommendation G.761).

- ii) Bit S<sub>a4</sub> may be used as a message-based data link to be recommended by ITU-T for operations, maintenance and performance monitoring. If the data link is accessed at intermediate points with consequent alterations to the S<sub>a4</sub> bit, the CRC-4 bits must be updated so as to retain the correct end-to-end path termination functions associated with the CRC-4 procedure (see 2.3.3.5.4). The data-link protocol and messages are for further study.

- iii) Bits  $S_{a5}$  to  $S_{a7}$  are for national usage where there is no demand on them for specific point-to-point applications [see i) above].

- iv) One of the bits  $S_{a4}$  to  $S_{a8}$  may be used in a synchronization interface to convey PDH synchronization status messages, as described in 2.3.4.

- Bits S<sub>a4</sub> to S<sub>a8</sub> (where these are not used) should be set to 1 on links crossing an international border.

### 2.3.3.4 Use of bit 1 in 2048 kbit/s CRC-4 multiframe

In those frames containing the frame alignment signal (defined in 2.3.2), bit 1 is used to transmit the CRC-4 bits. There are four CRC-4 bits, designated  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_4$  in each SMF.

In those frames not containing the frame alignment signal (see 2.3.2), bit 1 is used to transmit the 6-bit CRC-4 multiframe alignment signal and two CRC-4 error indication bits (E).

The CRC-4 multiframe alignment signal has the form 001011.

The E-bits should be set to "0" until both basic frame and CRC-4 multiframe alignment are established (see clause 4/G.706). Thereafter, the E-bits should be used to indicate received errored sub-multiframes by setting the binary state of one E-bit from 1 to 0 for each errored sub-multiframe. Any delay between the detection of an errored sub-multiframe and the setting of the E-bit that indicates the error state must be less than 1 second.

#### **NOTES**

- 1 The E-bits will always be taken into account even if the SMF which contains them is found to be errored, since there is little likelihood that the E-bits themselves will be errored.

- 2 In the short term, there may exist equipments which do not use the E-bits; in this case the E-bits are set to binary 1.

TABLE 5B/G.704

#### **CRC-4 multiframe structure**

|            | Sub-multiframe | Frame                                      |                                                                             |                                      | ]                                    | Bits 1 to                                                                              | 8 of the                                                                               | frame                                                                                   |                                                                                        |                                                                                        |

|------------|----------------|--------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|            | (SMF)          | number                                     | 1                                                                           | 2                                    | 3                                    | 4                                                                                      | 5                                                                                      | 6                                                                                       | 7                                                                                      | 8                                                                                      |

| Multiframe | I              | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7       | $\begin{array}{c} C_1 \\ 0 \\ C_2 \\ 0 \\ C_3 \\ 1 \\ C_4 \\ 0 \end{array}$ | 0<br>1<br>0<br>1<br>0<br>1<br>0      | 0<br>A<br>0<br>A<br>0<br>A<br>0<br>A | $\begin{matrix} 1 \\ S_{a4} \\ 1 \\ S_{a4} \\ 1 \\ S_{a4} \\ 1 \\ S_{a4} \end{matrix}$ | $\begin{matrix} 1 \\ S_{a5} \\ 1 \\ S_{a5} \\ 1 \\ S_{a5} \\ 1 \\ S_{a5} \end{matrix}$ | $\begin{array}{c} 0 \\ S_{a6} \\ 0 \\ S_{a6} \\ 0 \\ S_{a6} \\ 0 \\ S_{a6} \end{array}$ | $\begin{matrix} 1 \\ S_{a7} \\ 1 \\ S_{a7} \\ 1 \\ S_{a7} \\ 1 \\ S_{a7} \end{matrix}$ | $\begin{matrix} 1 \\ S_{a8} \\ 1 \\ S_{a8} \\ 1 \\ S_{a8} \\ 1 \\ S_{a8} \end{matrix}$ |

|            | II             | 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | C <sub>1</sub> 1 C <sub>2</sub> 1 C <sub>3</sub> E C <sub>4</sub> E         | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>A<br>0<br>A<br>0<br>A<br>0<br>A | $\begin{matrix} 1 \\ S_{a4} \\ 1 \\ S_{a4} \\ 1 \\ S_{a4} \\ 1 \\ S_{a4} \end{matrix}$ | $\begin{matrix} 1 \\ S_{a5} \\ 1 \\ S_{a5} \\ 1 \\ S_{a5} \\ 1 \\ S_{a5} \end{matrix}$ | $\begin{array}{c} 0 \\ S_{a6} \\ 0 \\ S_{a6} \\ 0 \\ S_{a6} \\ 0 \\ S_{a6} \end{array}$ | $\begin{matrix} 1 \\ S_{a7} \\ 1 \\ S_{a7} \\ 1 \\ S_{a7} \\ 1 \\ S_{a7} \end{matrix}$ | $\begin{matrix} 1 \\ S_{a8} \\ 1 \\ S_{a8} \\ 1 \\ S_{a8} \\ 1 \\ S_{a8} \end{matrix}$ |

#### **NOTES**

- 1 E = CRC-4 error indication bits (see 2.3.3.4).

- 2  $S_{a4}$  to  $S_{a8}$  = Spare bits (see Note 4 to Table 5A).

- 3  $C_1$  to  $C_4$  = Cyclic Redundancy Check-4 (CRC-4) bits (see 2.3.3.4 and 2.3.3.5).

- 4 A = Remote alarm indication (see Table 5A).

#### 2.3.3.5 Cyclic Redundancy Check (CRC)

### 2.3.3.5.1 Multiplication/division process

A particular CRC-4 word, located in sub-multiframe N, is the remainder after multiplication by  $x^4$  and then division (modulo 2) by the generator polynomial  $x^4 + x + 1$ , of the polynomial representation of sub-multiframe N – 1.

#### NOTES

- When representing the contents of the check block as a polynomial, the first bit in the block, i.e. frame 0, bit 1 or frame 8, bit 1, should be taken as being the most significant bit. Similarly,  $C_1$  is defined to be the most significant bit of the remainder and  $C_4$  the least significant bit of the remainder.

- 2 There may be a need to update CRC-4 bits at intermediate equipments which access the  $S_{a4}$  bit message-based datalink (see 2.3.3.5.4).

## 2.3.3.5.2 Encoding procedure

- i) The CRC-4 bits in the SMF are replaced by binary 0s.

- ii) The SMF is then acted upon by the multiplication/division process referred to in 2.3.3.5.1.

- iii) The remainder resulting from the multiplication/division process is stored, ready for insertion into the respective CRC-4 locations of the next SMF.

NOTE – The CRC-4 bits thus generated do not affect the result of the multiplication/division process in the next SMF because, as indicated in i) above, the CRC-4 bit positions in an SMF are initially set to 0 during the multiplication/division process.

#### 2.3.3.5.3 Decoding procedure

- i) A received SMF is acted upon by the multiplication/division process referred to in 2.3.3.5.1, after having its CRC-4 bits extracted and replaced by 0s.

- ii) The remainder resulting from this division process is then stored and subsequently compared on a bit-bybit basis with the CRC bits received in the next SMF.

iii) If the remainder calculated in the decoder exactly corresponds to the CRC-4 bits received in the next SMF, it is assumed that the checked SMF is error free.

#### 2.3.3.5.4 Updating procedure at intermediate path points in a message-based data-link application

The  $S_{a4}$  bit may be used as a message-based data-link within 2048 kbit/s paths [see Note 4, ii) to Table 5A]. Situations are envisaged where access to this data link could be required at points on the path between the true path termination points, e.g. reporting of error performance data from intermediate sites along the path. In such situations, it is important that the logical path termination role of CRC-4 is not invalidated or impaired. Hence, any changes to the  $S_{a4}$  bits within a SMF at an intermediate path point does not imply a recalculation of the CRC-4 bits over the whole SMF, but rather their update as a linear recoding function in respect of specific deterministic binary changes of the  $S_{a4}$  bits only.

Annex C/G.706 gives further information regarding this updating procedure.

## 2.3.4 Synchronization Status: San

One of the  $S_{a4}$  to  $S_{a8}$  bits, (the actual  $S_a$  bit is for operator selection), is allocated for PDH Synchronization Status Messages. To prevent ambiguities in pattern recognition, it is necessary to align the first bit ( $S_{an1}$ , Table 5C) with frame 1 (Table 5D) of a G.704 multiframe. Table 5C gives the assignment of bit patterns to the four synchronization levels agreed to within ITU-T. Two additional bit patterns are assigned: one to indicate that quality of the synchronization is unknown and the other to indicate that the signal should not be used for synchronization. The remaining codes are reserved for quality levels defined by individual operators.

Table 5D gives the numbering of the  $S_{an}$  (n = 4, 5, 6, 7, 8) bits. A  $S_{an}$  bit is organized as a 4 bit nibble  $S_{an1}$  to  $S_{an4}$ .  $S_{an1}$  is the most significant bit,  $S_{an4}$  is the least significant bit.

NOTE - The message set in San1 to San4 is a copy of the set defined in SDH bits 5 to 8 of byte S1.

#### 2.4 Basic frame structure at 8448 kbit/s

#### 2.4.1 Frame length

The number of bits per frame is 1056. They are numbered from 1 to 1056. The frame repetition rate is 8000 Hz.

### 2.4.2 Frame alignment signal

The frame alignment signal is 11100110 100000 and occupies the bit-positions 1 to 8 and 529 to 534.

#### 2.4.3 Service digits

Bit 535 is used to convey alarm indication (bit 535 at 1 state = alarm; bits 535 at 0 state = no alarm).

Bit 536 is left free for national use and should be fixed at 1 on paths crossing the international border. The same applies to bits 9-40 in the case of channel-associated signalling.

### 2.5 Basic frame structure at 44 736 kbit/s

### 2.5.1 Multiframe length

The number of bits per multiframe is 4760 bits.

## 2.5.2 Multiframe overhead bits

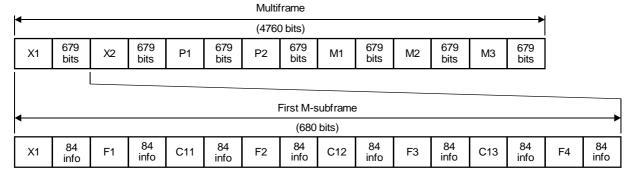

The multiframe are divided into seven M-subframes each with 680 bits; each M-subframe is further divided into 8 blocks of 85 bits: 1 bit for overhead and 84 bits for payload (see Figure 2). Thus, there are 56 overhead bits per multiframe.

#### 2.5.3 Allocation of the multiframe overhead bits

The overhead bits are the first bit of the eight 85-bit blocks in each of the seven M-subframes in a multiframe, as shown in Figure 2. The 56 overhead bits are: 2 X-bits, 2 P-bits, 3 M-bits, 28 F-bits, and 21 C-bits.

TABLE 5C/G.704

#### Synchronization Status Message (SSM) bit allocation

| QL                      | S <sub>an1</sub> , S <sub>an2</sub> , S <sub>an3</sub> , S <sub>an4</sub> (Note) | Synchronization Quality Level (QL) description     |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| 0                       | 0000                                                                             | Quality unknown (existing synchronization network) |  |  |  |  |

| 1                       | 0001                                                                             | Reserved                                           |  |  |  |  |

| 2                       | 0010                                                                             | Rec. G.811                                         |  |  |  |  |

| 3                       | 0011                                                                             | Reserved                                           |  |  |  |  |

| 4                       | 0100                                                                             | G.812 transit                                      |  |  |  |  |

| 5                       | 0101                                                                             | Reserved                                           |  |  |  |  |

| 6                       | 0110                                                                             | Reserved                                           |  |  |  |  |

| 7                       | 0111                                                                             | Reserved                                           |  |  |  |  |

| 8                       | 1000                                                                             | G.812 local                                        |  |  |  |  |

| 9                       | 1001                                                                             | Reserved                                           |  |  |  |  |

| 10                      | 1010                                                                             | Reserved                                           |  |  |  |  |

| 11                      | 1011                                                                             | Synchronous Equipment Timing Source (SETS)         |  |  |  |  |

| 12                      | 1100                                                                             | Reserved                                           |  |  |  |  |

| 13                      | 1101                                                                             | Reserved                                           |  |  |  |  |

| 14                      | 1110                                                                             | Reserved                                           |  |  |  |  |

| 15                      | 15 Do not use for synchronization                                                |                                                    |  |  |  |  |

| $\overline{NOTE - n} =$ | 4, 5, 6, 7 or 8 (i.e. one S <sub>a</sub> bit only) de                            | pending on operator selection.                     |  |  |  |  |

### 2.5.3.1 X-bits (X1, X2)

X1 and X2 are used to indicate received errored multiframes to the remote-end (remote alarm indication "RAI" or "yellow" signal); these bits are set to binary 1 (i.e., X1 = X2 = 1) during error free condition, and to binary 0 (i.e. X1 = X2 = 0) if Loss of Signal (LOS), Out of Frame (OOF), Alarm Indication Signal (AIS), or Slips are detected in the incoming signal. The maximum allowed rate of change of state for the X-Bits is once a second; therefore, the X-Bits should be set to binary 0 for a length of time equal to the length of the error condition, but rounded-up to the next integer.

## 2.5.3.2 P-bits (P1, P2)

P1 and P2 are used for performance monitoring; these bits carry parity information calculated over the 4704 payload bits in the preceding multiframe: P1 = P2 = 1 if the digital sum of all payload bits is one, and P1 = P2 = 0 if the digital sum of all payload bits is zero. The P-bits are calculated and may be modified at each section of a facility; therefore, the P-bits provide SECTION performance information NOT end-to-end performance information.

## 2.5.3.3 Multiframe alignment signal (M1, M2, M3)

The multiframe alignment signal 010 (M1 = 0, M2 = 1, M3 = 0) is used to locate all seven M-subframes, within the multiframe.

TABLE 5D/G.704

## S<sub>an</sub> numbering in TimeSlot 0 (TS0) for use in synchronization status message

|    | Frame<br>number | Bit 1          | Bit 2 | Bit 3 | Bit 4            | Bit 5            | Bit 6            | Bit 7            | Bit 8            |

|----|-----------------|----------------|-------|-------|------------------|------------------|------------------|------------------|------------------|

|    | 0               | C <sub>1</sub> | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

|    | 1               | 0              | 1     | A     | S <sub>a41</sub> | S <sub>a51</sub> | S <sub>a61</sub> | S <sub>a71</sub> | S <sub>a81</sub> |

| S  | 2               | C <sub>2</sub> | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

| M  | 3               | 0              | 1     | A     | S <sub>a42</sub> | S <sub>a52</sub> | S <sub>a62</sub> | S <sub>a72</sub> | S <sub>a82</sub> |

| F  | 4               | C <sub>3</sub> | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

| I  | 5               | 1              | 1     | A     | S <sub>a43</sub> | S <sub>a53</sub> | S <sub>a63</sub> | S <sub>a73</sub> | S <sub>a83</sub> |

|    | 6               | C <sub>4</sub> | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

|    | 7               | 0              | 1     | A     | S <sub>a44</sub> | S <sub>a54</sub> | S <sub>a64</sub> | S <sub>a74</sub> | S <sub>a84</sub> |

|    | 8               | $C_1$          | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

|    | 9               | 1              | 1     | A     | S <sub>a41</sub> | S <sub>a51</sub> | S <sub>a61</sub> | S <sub>a71</sub> | S <sub>a81</sub> |

| S  | 10              | $C_2$          | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

| M  | 11              | 1              | 1     | A     | S <sub>a42</sub> | S <sub>a52</sub> | S <sub>a62</sub> | S <sub>a72</sub> | S <sub>a82</sub> |

| F  | 12              | $C_3$          | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

| II | 13              | Е              | 1     | A     | S <sub>a43</sub> | S <sub>a53</sub> | S <sub>a63</sub> | S <sub>a73</sub> | S <sub>a83</sub> |

|    | 14              | C <sub>4</sub> | 0     | 0     | 1                | 1                | 0                | 1                | 1                |

|    | 15              | Е              | 1     | A     | S <sub>a44</sub> | S <sub>a54</sub> | S <sub>a64</sub> | S <sub>a74</sub> | S <sub>a84</sub> |

### 2.5.3.4 M-subframe alignment signal (F1, F2, F3, F4)

The M-subframe alignment signal 1001 (F1 = 1, F2 = 0, F3 = 0, F4 = 1) is used to identify the overhead bit positions.

## 2.5.3.5 C-bits (C11, C12, C13, C21, ... C<sub>ij</sub>, ... C73)

In general 44 736 kbit/s signals could be:

- a) unchannelized for bulk data transport; and

- b) channelized for multiplex applications.

In either case, the  $C_{ij}$  bit positions are available for specific uses, and must be settable by 44 736 kbit/s sources. The way that these  $C_{ij}$  bits are used determine the features available in the 44 736 kbit/s signal, through the embedded operations channels:

• The 6312-44 736 kbit/s multiplexing application (M23), uses the C-bits to indicate justification (Recommendation G.752). This standard describes the C-bit Parity application which does not use stuffing bits for justification.

|    | The 56 overhead bits sequential positions as follows: |     |    |     |    |     |    |

|----|-------------------------------------------------------|-----|----|-----|----|-----|----|

| X1 | F1                                                    | C11 | F2 | C12 | F3 | C13 | F4 |

| X2 | F1                                                    | C21 | F2 | C22 | F3 | C23 | F4 |

| P1 | F1                                                    | C31 | F2 | C32 | F3 | C33 | F4 |

| P2 | F1                                                    | C41 | F2 | C42 | F3 | C43 | F4 |

| M1 | F1                                                    | C51 | F2 | C52 | F3 | C53 | F4 |

| M2 | F1                                                    | C61 | F2 | C62 | F3 | C63 | F4 |

| M3 | F1                                                    | C71 | F2 | C72 | F3 | C73 | F4 |

T1518720-95/d01

FIGURE 2/G.704

#### 44 736 kbit/s multiframe structure

• Both, the unchannelized application as well as the channelized C-bit Parity multiplex application<sup>1)</sup> use the C-bits as described in 2.5.3.5.1.

## 2.5.3.5.1 Allocation of C-bits for C-bit Parity application

Regardless of the application (unchannelized or channelized) the C-bits for C-bit Parity application are allocated as follows:

- C11: Application Identification Channel (AIC) For C-bits Parity application this bit shall be set to binary 1.

- C12: Network Requirements  $(N_r)$  Reserved for future network use. It shall be set to binary 1.

- C13: Far-End Alarm and Control (FEAC) bit is used for two purposes:

- Alarm signals to send alarm or status information from the far-end terminal back to the near-end terminal; and

<sup>1)</sup> The C-Bit Parity multiplex application for channelized signals uses a two-step multiplexing process to multiplex primary rate signals (1544 or 2048 kbit/s) to the 44 736 kbit/s level. In the first step, four 1544 kbit/s or three 2048 kbit/s lines are multiplexed together to form an integral signal at a bit rate f<sub>e</sub>, (pseudo-6312 kbit/s level). In the second step, seven pseudo-6312 kbit/s level, each at a bit rate f<sub>e</sub> are multiplexed together to form a 44 736 kbit/s signal with enhanced operations features. The bit rate f<sub>e</sub> (nominally 6306.2723) kbit/s) is chosen such that when the seven pseudo-6312 kbit/s level signals are combined, along with "full time" 44 736 kbit/s level justification and the 56 frame overhead bits, the resultant output bit rate will nominally be 44 736 kbit/s. This multiplexing process is the same as that defined for the M23 application except that in the C-bit Parity case all seven intermediate timeslots, one in each of the seven M-subframes, are justified at every justification opportunity. Since justification occurs 100% of the time, the C-bits are not needed to denote justification, and they can be used for other purposes.

2) Control signals to initiate 44 736 kbit/s and 1544 kbit/s line loopbacks at the far-end terminal, from the near-end terminal.

At international interfaces, initiation of control loopback signal is "optional" and the application of this functionality should be at the discretion of the respective Administrations. The FEAC signal consists of a repeating 16-bit codeword with a general format of 0xxx xxx0 1111 1111, rightmost bit transmitted first (where x can be a 1 or a 0).

To report alarm/status conditions, the 16-bit codeword must be repeated at least 10 times, or while the condition exists, whichever is longer. (Table 6 shows the alarms/status codewords assigned). These codewords shall be transmitted only after the event has been declared: for example, a 44 736 kbit/s AIS defect would be detected and then timed for several seconds before declaring AIS failure, at which time the appropriate codeword would be transmitted.

To send loopback control commands, two codewords must be sent: the first one – repeated ten times – to activate/de-activate, the other – also repeated ten times – to specify the line number, therefore, each loopback command consists of 20 16-bit codewords. (Table 7 shows the control codewords assigned.) Control words take precedence over alarm signals.

When no alarm/status or control is being transmitted, the FEAC bits must be all set to binary 1.

- C21, C22, C23 Not used; must be set to binary 1.

- C31, C32, C33 CP-bits are used to carry path (end-to-end facility) parity information. The network terminating equipment (NTE) that originates the 44 736 kbit/s signal must set these bits (C31 = C32 = C33) to the same value as the P-bits. The CP-bits must not be modified along the 44 736 kbit/s facility path.

- C41, C42, C43 FEBE-bits are used to carry far-end block error information. All three FEBE bits are set to binary 1 (C41 = C42 = C43 = 1) if no errors are detected in the M-bits, or F-bits, or indicated by the CP-bits. If any error condition (errored M-bits, errored F-bits, or parity in CP-bits) is detected within the multiframe, the FEBE bits must be set to any combination of 1s or 0s (except 111).

- C51, C52, C53 DL<sub>t</sub> bits are used for a 28.2 kbit/s-terminal-to-terminal path maintenance data link. The implementation of this data link is optional but if implemented, it shall conform to the rules set forth in this subclause. The messages carried in the path maintenance data link utilize the frame structure, field definitions, and elements of procedure of the LAPD protocol defined in Recommendation Q.921 but with different addresses. The structure of the LAPD message-oriented signals is defined in Table 8. Table 9 shows the contents and structure of the information field for each of the four message types defined: Common Language Path ID, ITU-T Path ID, Test ID, and Idle Signal ID. The information field contains 6 data elements to identify:

- 1) the test type;

- 2) the equipment type;

- 3) the central office location;

- 4) the frame (within the central office);

- 5) the unit (within the frame); and

- 6) information specific to the test type.

These signals shall be transmitted continuously at a minimum rate of once per second. When LAPD messages are not being transmitted (i.e. the data link is idle), LAPD flags (01111110) shall be continuously transmitted. If terminal-to-terminal data link function is not implemented, all three bits shall be set to binary 1 (C51 = C52 = C53 = 1). Other applications for the path maintenance data link are for further study.

- C61, C62, C63 Not used; must be set to binary 1.

- C71, C72, C73 Not used; must be set to binary 1.

TABLE 6/G.704

#### FEAC alarm/status codewords

| FEAC alarm/status codewords                    |                     |  |  |  |  |  |

|------------------------------------------------|---------------------|--|--|--|--|--|

| Alarm/status condition                         | Codeword            |  |  |  |  |  |

| Out of frame at 44 736 kbit/s                  | 0000 0000 1111 1111 |  |  |  |  |  |

| Equipment failure at 1544 or 2048 kbit/s (NSA) | 0000 0110 1111 1111 |  |  |  |  |  |

| Equipment failure at 1544 or 2048 kbit/s (SA)  | 0000 1010 1111 1111 |  |  |  |  |  |

| LOS/HBER at 44 736 kbit/s                      | 0001 1100 1111 1111 |  |  |  |  |  |

| Equipment failure at 44 736 kbit/s (NSA)       | 0001 1110 1111 1111 |  |  |  |  |  |

| Multiple LOS/HBER at 1544 or 2048 kbit/s       | 0010 1010 1111 1111 |  |  |  |  |  |

| AIS received 44 736 kbit/s                     | 0010 1100 1111 1111 |  |  |  |  |  |

| Equipment failure for 44 736 kbit/s (SA)       | 0011 0010 1111 1111 |  |  |  |  |  |

| Idle received at 44 736 kbit/s                 | 0011 0100 1111 1111 |  |  |  |  |  |

| Common equipment (NSA)                         | 0011 1010 1111 1111 |  |  |  |  |  |

| Single LOS/HBER at 1544 or 2048 kbit/s         | 0011 1100 1111 1111 |  |  |  |  |  |

#### **NOTES**

- 1 The rightmost bit of each codeword is transmitted first.

- 2 SA denotes service affecting equipment failure forcing out-of-service state, indicating a defect requiring immediate attention.

- 3 NSA denotes non-service affecting equipment failure indicating a defect in equipment that is not activated, not available, or suspended; it requires attention, but not high priority.

## 2.5.3.6 Special patterns used at 44 736 kbit/s

Two special patterns are defined for the 44 736 kbit/s signals independently of how the C-bits are used: AIS and IDLE, as described next.

## 2.5.3.6.1 Alarm Indication Signal (AIS)

The AIS is a signal with valid multiframe and M-subframe alignment signals, and valid P-bits. The information bits are set to a 1010... sequence, starting with a binary one (1) after each M-bit, F-bit, X-bit, P-bit, and C-bit. The C-bits are set to binary zero (C1 = 0, C2 = 0, C3 = 0). The X-bits are set to binary one (X1 = 1, X2 = 1).

## **2.5.3.6.2** Idle Signal (Idle)

The Idle Signal is a signal with valid multiframe and M-subframe alignment signals, and valid P-bits. The information bits are set to a 1100... sequence, starting with a binary one (1) after each M-bit, F-bit, X-bit, and C-bit. The C-bits are set to binary zero (C1 = 0, C2 = 0, C3 = 0), in the third M-subframe (C31, C32, C33); the remaining C-Bits (three C-bits in M-subframes 1, 2, 4, 5, 6, and 7) may be individually set to one or zero, and may vary with time. The X-bits are set to binary one (X1 = 1, X2 = 1).

TABLE 7/G.704

### FEAC control codeword

| FEAC control codewords                                                                                                                                                                                                                                                                                                                                                        |                                            |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|

| Command                                                                                                                                                                                                                                                                                                                                                                       | Codeword                                   |  |  |  |  |  |

| Activate loopback De-activate loopback 44 736 kbit/s line                                                                                                                                                                                                                                                                                                                     | 0000 1110 1111 1111<br>0011 1000 1111 1111 |  |  |  |  |  |

| All 1544 or 2048 kbit/s lines<br>1544 or 2048 kbit/s Line No. 1, Group #1<br>1544 or 2048 kbit/s Line No. 2, Group #1<br>1544 or 2048 kbit/s Line No. 3, Group #1<br>1544 kbit/s Line No. 4, Group #1<br>1544 or 2048 kbit/s Line No. 1, Group #2<br>1544 or 2048 kbit/s Line No. 2, Group #2<br>1544 or 2048 kbit/s Line No. 3, Group #2<br>1544 kbit/s Line No. 4, Group #2 | 0010 0110 1111 1111<br>0100 0010 1111 1111 |  |  |  |  |  |

| 1544 or 2048 kbit/s Line No. 1, Group #3 1544 or 2048 kbit/s Line No. 2, Group #3 1544 or 2048 kbit/s Line No. 3, Group #3 1544 kbit/s Line No. 4, Group #3 1544 or 2048 kbit/s Line No. 1, Group #4 1544 or 2048 kbit/s Line No. 2, Group #4 1544 or 2048 kbit/s Line No. 3, Group #4 1544 kbit/s Line No. 4, Group #4                                                       | 0101 0010 1111 1111<br>0101 0100 1111 1111 |  |  |  |  |  |

| 1544 or 2048 kbit/s Line No. 1, Group #5<br>1544 or 2048 kbit/s Line No. 2, Group #5<br>1544 or 2048 kbit/s Line No. 3, Group #5<br>1544 kbit/s Line No. 4, Group #5                                                                                                                                                                                                          | 0110 0010 1111 1111<br>0110 0100 1111 1111 |  |  |  |  |  |

| 1544 or 2048 kbit/s Line No. 1, Group #6<br>1544 or 2048 kbit/s Line No. 2, Group #6<br>1544 or 2048 kbit/s Line No. 3, Group #6<br>1544 kbit/s Line No. 4, Group #6                                                                                                                                                                                                          | 0110 1010 1111 1111<br>0110 1100 1111 1111 |  |  |  |  |  |

| 1544 or 2048 kbit/s Line No. 1, Group #7<br>1544 or 2048 kbit/s Line No. 2, Group #7<br>1544 or 2048 kbit/s Line No. 3, Group #7<br>1544 Line No. 4, Group #7                                                                                                                                                                                                                 | 0111 0010 1111 1111<br>0111 0100 1111 1111 |  |  |  |  |  |

## NOTES

- The commands that refer to 1544 or 2048 kbit/s line apply only to a channelized C-bit Parity applications.

- $^{2}$  "Group" refers to the four 1544 kbit/s or three 2048 kbit/s signals that form the intermediate internal  $f_{e}$  signal (see footnote 1); seven of these groups (plus justification) are combined to form the 44 736 kbit/s signal.

- The rightmost bit of each codeword is transmitted first.

- 4 To activate or de-activate loopback, the appropriate activate or de-activate 16-bit codeword is transmitted ten times followed immediately by ten repetitions of the 16-bit codeword corresponding to the required line number. Thus, the total length of loopback control message is 20 16-bit words.

TABLE 8/G.704

### LAPD message structure

| Octet no.                                                        | Octet label     | Octet content                                                                              |            |                                                |  |  |

|------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------|------------|------------------------------------------------|--|--|

| 1                                                                | Flag            | Flag                                                                                       |            |                                                |  |  |

| 2                                                                | SAPI            | CR                                                                                         | EA         | 00111100 <sub>2</sub> or 00111110 <sub>2</sub> |  |  |

| 3                                                                | TEI             | •                                                                                          | EA         | 000000012                                      |  |  |

| 4                                                                | Control         |                                                                                            |            | 000000112                                      |  |  |

|                                                                  | Information fie | Information field                                                                          |            |                                                |  |  |

| N – 1                                                            | FCS             |                                                                                            |            | See below                                      |  |  |

| N                                                                | FCS             |                                                                                            |            |                                                |  |  |

| Flag<br>01111110 <sub>2</sub>                                    |                 | nterpretation<br>esponse Messa                                                             | age        |                                                |  |  |

| SAPI   CR   EA<br>00111100 <sub>2</sub><br>00111110 <sub>2</sub> | S               | Interpretation<br>SAPI = 15, C/R = 0 (DTE), EA = 0<br>SAPI = 15, C/R = 1 (carrier), EA = 0 |            |                                                |  |  |

| TEI/EA<br>00000001 <sub>2</sub>                                  |                 | Interpretation TEI = 0, EA = 1                                                             |            |                                                |  |  |

| Control<br>00000011 <sub>2</sub>                                 |                 | Interpretation Fixed value: Unacknowledged Information Transfer                            |            |                                                |  |  |

| Information field variable                                       | II<br>S         | Interpretation<br>See Table 9                                                              |            |                                                |  |  |

| FCS<br>Frame Check Seque                                         | nce In C        | nterpretation<br>RC-16 Frame                                                               | Check Sequ | ence, 16-bit code                              |  |  |

NOTE – The source of the identification messages shall generate the FCS and the zero stuffing required for transparency. Zero stuffing by a transmitter prevents the occurrence of the flag patten (01111110) in the bits between the opening and closing flags of a frame, by inserting a zero after any sequence of five consecutive ones. The receiver removes a zero following five consecutive ones.

- 3 Characteristics of frame structure carrying channels at various bit rates in 1544 kbit/s

- 3.1 Interface at 1544 kbit/s carrying 64 kbit/s channels

- 3.1.1 Frame structure

- 3.1.1.1 Number of bits per 64 kbit/s channel time slot

Eight, numbered 1 to 8.

TABLE 9/G.704

### Information field contents for data-link messages

ITU-T path identification

CL path identification

| CL paul          | identification              |                        | 110-1 paul 1              | dentification            | _                   |

|------------------|-----------------------------|------------------------|---------------------------|--------------------------|---------------------|

| Data elements    | Binary value                |                        | Data elements             | Binary value             |                     |

| Туре             | 0011 1000<br>(1 octet)      | CL-path ID             | Туре                      | 0011 1111<br>(1 octet)   | ITU-T path ID       |

| LIC              | xxxx xxxx (10 octets)       | Equipment ID           | LIC                       | xxxx xxxx<br>(10 octets) | Equipment ID        |

| FIC              | xxxx xxxx<br>(11 octets)    | Location ID            | FIC                       | xxxx xxxx<br>(11 octets) | Location ID         |

| EIC              | xxxx xxxx (10 octets)       | Frame ID               | EIC                       | xxxx xxxx (10 octets)    | Frame ID            |