## Les Multiplexes Numériques

Mr. H. Leijon, UIT

## 1. Les Multiplexes Numériques

## 1.1 Introduction

Les premiers systèmes MIC sont destinés aux applications a courte distance. Dans le réseau a longue et moyenne distance, où on demande une capacité supérieure en matière de circuits, il est plus économique et pratique de grouper ensemble le plus grand nombre de systèmes MIC en une ligne commune de transmission, au lieu d'utiliser plusieurs systèmes primaires MIC. Ces systèmes supérieurs sont appelés Multiplexes Numériques.

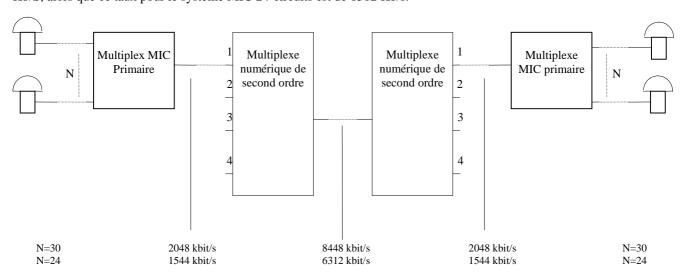

La tâche principale pour un multiplexeur numérique est de combiner un nombre d'impulsions de flux d'arrivée, tributaires dans un flux d'impulsions sortant avec un taux de bits bruts qui est un peu élevé que les taux tributaires et vice versa. Dans un système de second ordre, quatre signaux primaires MIC sont combinés à un signal commun numérique. Les deux systèmes primaires MIC standardises donnent deux multiplexes numériques avec des taux de bits différents (voir Figure1). Un multiplexe numérique base sur le système MIC a 30 circuits et a un taux de bits de 8448 Kb/S, alors que ce taux pour le système MIC 24-circuits est de 6312 Kb/s.

Figure 1

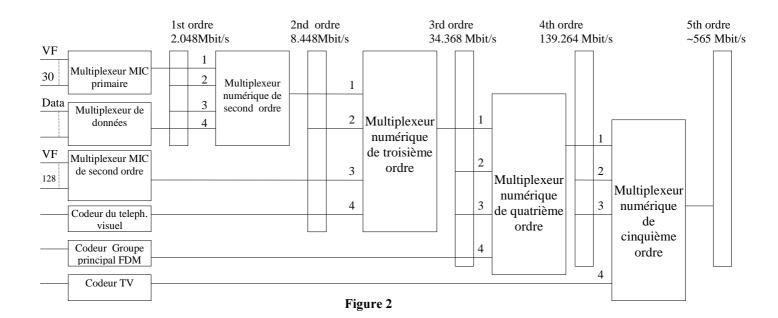

Les systèmes de transmission numériques peuvent être relies ensemble en une hiérarchie, de la même manière que pour les systèmes FDM. Une hiérarchie d'un multiplexe numérique en système MIC à 30 voies est montrée en Figure 2. On peut y voir que les facilites de transmission peuvent être utilisées non seulement pour la voix, mais aussi pour les données, le téléphone visuel, les groupes FDM et la télévision.

## 1.2 Les mutiplexes numériques de second ordre

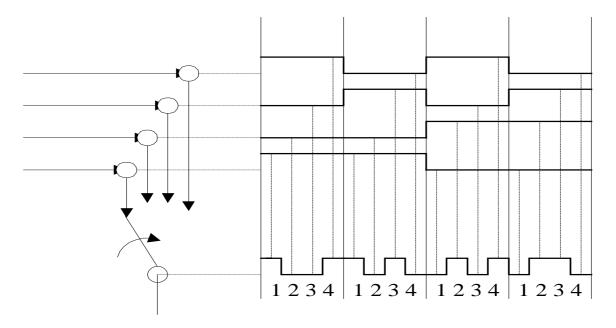

Les principes de base du multiplexage numérique sont les mêmes dans tous les étages hiérarchiques. Le multiplexage dans le multiplexeur de second ordre peut servir comme un modèle général. Le principe fondamental de multiplexage numérique est le processus d'intercalage dans le quel les tributaires sont combinées bit par bit à un flux de bit commun de sortie (voir Figure 3).

Figure 3: Intercalage de bits

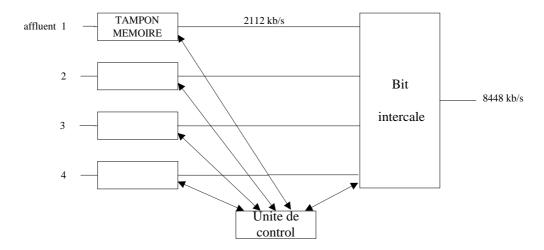

Quand un bit intercale entre, les quatre affluents doivent être synchronisés. Tous les multiplexes primaires ont indépendamment des horloges fonctionnant pour donner ainsi des flux de bits avec une légère différence dans les taux de bits et dans les phases.

Pour atteindre la synchronisation entre les affluents, des tampons mémoires, sont places entre les affluents et le bit intercale. C'est ce que montre la figure 4. La synchronisation est maintenant réalisée en lisant les bits dans le mémoire tampon avec un taux de bits plus élevé que lors de la lecture de bits à l'intérieur. La lecture du taux est de 2112 Kb/s, ce qui donne un taux de bits de second ordre de 4 x 2112 = 8448 Kb/s. Le taux de bit nominal pour un flux primaire est 2048 Kb/s. Une unité de contrôle ordonne la lecture depuis les quatre tampons mémoires en même temps. La lecture doit être faites dans des bains a cause du taux de bits élevé.

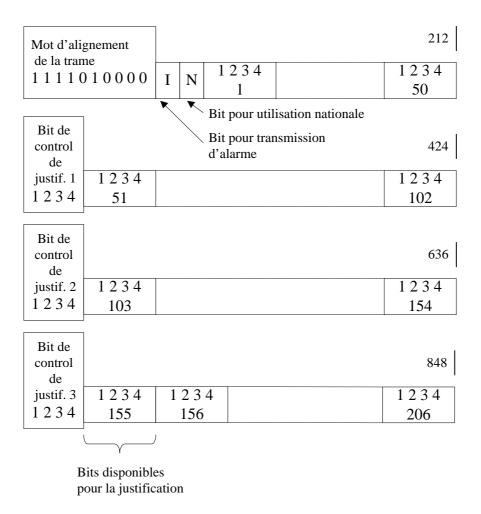

La structure de la trame du second ordre est décidée par unité de contrôle où le mot d'alignement de la trame du second ordre (1111010000), deux bits de service et de contrôle de justification sont insérés dans le temps disponible entre les sous-trames - voir Figure 5.

Ici, les bits de contrôle de justification, et les quatre mots de bit no. 155 appelle une explication plus détaillée. Puisque les taux de bits des affluents peuvent varier quelques peu de leur valeur nominale de 2048 Kb/s, alors que la lecture depuis les mémoires tampon est toujours constante, il y a un risque de surestimer une des mémoires tampon. Le risque est annule en stoppant la lecture de cette mémoire durant la période d'un bit. Les quatre mots no. 155 (un bit/affluent) est réservé à cette fin. les positions des bits contiennent ou des informations des affluents ou des bits redondants dépendant de la charge dans les tampons mémoires.

Si une position de bit dans le mot de bit no. 155 contient une information d'affluent, les trois bits correspondants de contrôle de justification sont intégrés en un, si non ils se positionnent sur zéro. Le multiplexeur receveur peut alors faire un choix multiple par le moyen des trois bits de contrôle de justification. Par conséquent une erreur due à un bit isolée ne peut modifier le résultat.

Dans la direction de réception, la trame du mot d'alignement est utilisée comme une référence lors de la définition du signal digital a l'entrée dans ses composantes. Le statut du contrôle de la justification des bits est note et les termes des bits, non voulus du no. 155 sont écartés. Les bits sont inscrits dans les mémoires en vue d'adoucir les variations dans la transmission. La lecture a partir des tampons mémoires est faite au même temps que le taux de bit, comme une moyenne du signal original affluent.