#### **Sebastien Gareau**

#### Systems Architect and Distinguished Engineer | Ciena, USA

Sebastien is a Systems Architect in the WaveLogic Technologies team, working on the latest coherent modem products.

His background is in ASIC/FPGA digital design and architecture, and has been at Ciena for 16 years.

He represents Ciena in various public forums such as ITU-T Question 11, OpenROADM and OIF Optical track, and has various editorship roles in these forums.

#### ITU Workshop on "Evolution of Optical Networks for IMT2030 and Beyond" Charles K. Kao Auditorium, Hong Kong Science and Technology Park (HKSTP) 20 November 2024, 15:00 - 18:00

#### **B800G and other thoughts**

**Sebastien Gareau**

# **B800G** Asks/Requirements

- Increase capacity/reach of interfaces by increasing aggregate baud

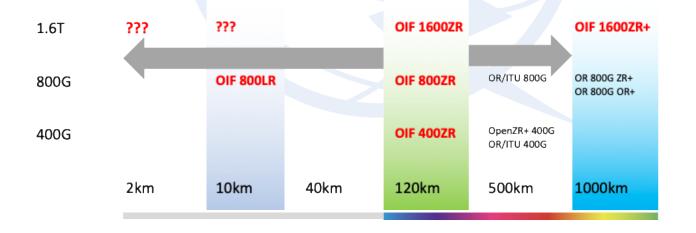

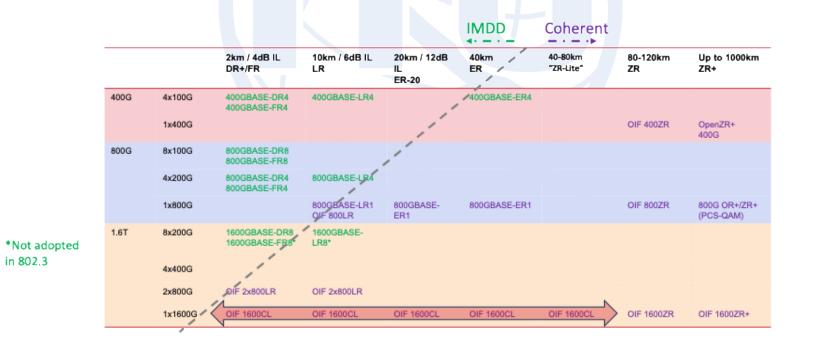

- E.g. 1.6T and 1.2T aligning to OIF 1600ZR+ and 1200ZR+

- LO/HO container to aggregate and optimize muxponding

- LO/HO container to optimize OTN switching

- Optimize the interoperable interface bit rate

- ZR+ Reach expectations in OIF 1000km, beyond current scope of ITU

Note: ITU is calling it B1T, but we have not excluded the need for a new 800G longer reach interface at this early stage

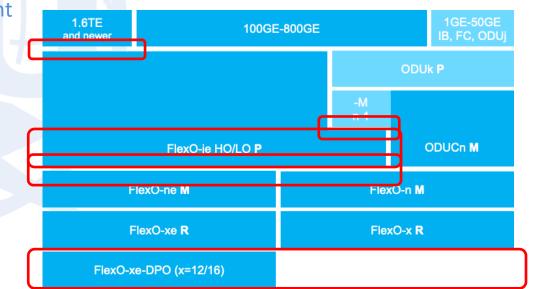

# **Proposed B800G Architecture**

- Focus on FlexO-xe/ZR+ Ethernet optimized <u>multi-vendor</u> <u>interoperable</u> interfaces

- Full rate FlexO-x and Ethernet optimized FlexO-xe supported by bookend single-vendor interfaces (common elements in G.709.1)

- FlexO-x-DPO OTN <u>multi-vendor interoperable</u> interfaces no longer needed

- FlexO-ne Ethernet GMP mapping procedure to include 1.6TE client

- ODUflex BMP mapping in G.709 no longer needed

- FlexO-je optional and switchable path layer and define OH

- Name still in discussion (e.g. B1T ODU, FlexO-npe, ...)

- FlexO-je to FlexO-n mapping procedure

- FlexO-je to FlexO-ne adaptation procedure

- Legacy ODUk and ODUCn services can be mapped to FlexO-n

- No compromises in capacity

- Legacy ODUk and ODUCn services can be mapped to FlexO-ne

- Compromise in capacity

Both FlexO-xe and FlexO-x can be supported by bookend single-vendor

## Proposed New B800G G.709.x Work Items

- New FlexO-16e-RS in G.709.5

- New FlexO-12e-DPO and FlexO-16e-DPO in G.709.6 or G.709.b1t

- New FlexO-16e-MFI and FlexO-16-MFI in G.sup58

- Extend Ethernet GMP mapping procedure to include 1.6TE client in G.709.1

- New FlexO-je optional <u>path</u> layer and define OH in G.709.1

- New FlexO-je to FlexO-n mapping procedure in G.709.1

- New ODUCn-1 or ODUCn-M mapping procedure in G.709.1

- Note: ITU members can alternatively decide to create new Recommendations

# **B800G/ZR+ Interoperable PCS**

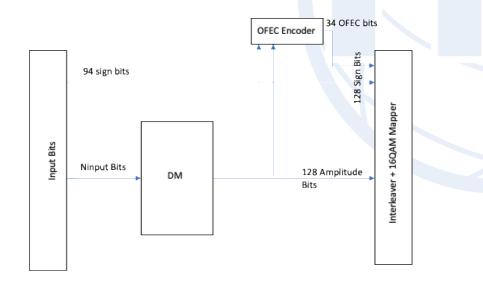

- ITU has not adopted interoperable probabilistic shaping in B400G — Likely needed for B800G, alignment with OIF that has target reach of 1000km

- Amplitude shaping can be applied to OFEC

# **B800G/ZR+ Interoperable PCS**

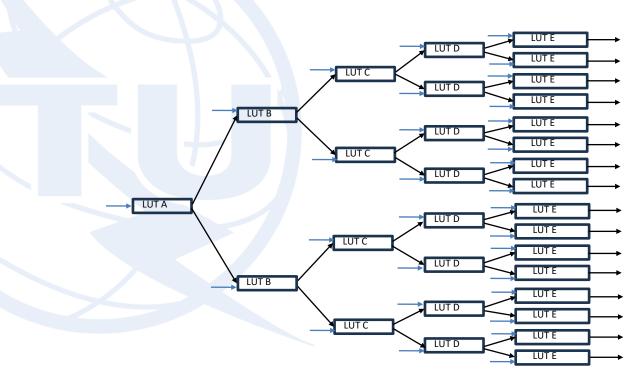

- OpenROADM adopted a simple scheme for B400G

- LUT based, with N=11

- Option for ITU B800G

- 260Gbaud FlexO-16e/ZR+

- OIF proposals for 1200ZR+/1600ZR+

- Ciena proposal, fixed tree, N=128

- Option for ITU B800G

- Tradeoff performance and baud

- 250-260Gbaud FlexO-16e/ZR+

- OIF requirement of 13.7dB RSNR

# **Coherent-Lite**

- OIF has an active project for 800LR

- OIF started project 1600CL

- Based on KP4+BCH2 concat FEC

- Low latency/power, purpose built

# **Coherent-Lite**

- Should this be in scope of ITU for FlexO-x and FlexO-xe?

- OTN handoff applications for FlexO-x-RS don't have a lot of traction

- CL can address various applications

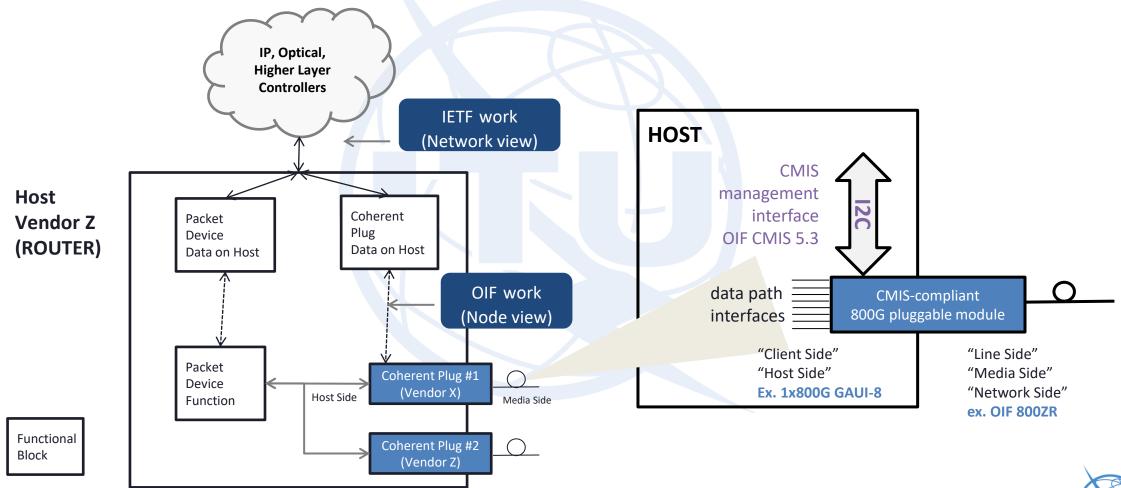

# **Network Management Coherent Plugs**

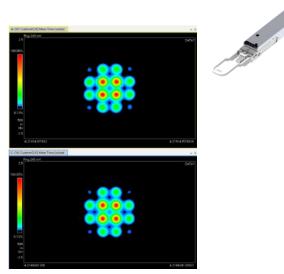

## 1.6T is Here!

#### WaveLogic 6 Nano WaveLogic 6 Extreme 800G, 141GBd, 3nm CMOS 1.6Tb/s, 200Gbaud, 3nm CMOS 1.6T, 2x800LR , 3nm CMOS 900 800 *~*% 1<sup>st</sup> 3nm coherent 009 500 Gb/s DSP ASIC ₹3 300 200 1600G 1500 **3nm coherent** 1<sup>st</sup> 200GBaud Silicon **DSP ASIC** Receiver **Photonics** Receiver 1<sup>st</sup> 200GBaud **Silicon Photonics-based Coherent Driver Modulator** Modulator with integrated (CDM) SOA

# Thank you !