TELECOMMUNICATION STANDARDIZATION SECTOR

OF ITU

**V.28**

(03/93)

# DATA COMMUNICATION OVER THE TELEPHONE NETWORK

# ELECTRICAL CHARACTERISTICS FOR UNBALANCED DOUBLE-CURRENT INTERCHANGE CIRCUITS

ITU-T Recommendation V.28

(Previously "CCITT Recommendation")

#### **FOREWORD**

The ITU Telecommunication Standardization Sector (ITU-T) is a permanent organ of the International Telecommunication Union. The ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.

The World Telecommunication Standardization Conference (WTSC), which meets every four years, established the topics for study by the ITU-T Study Groups which, in their turn, produce Recommendations on these topics.

ITU-T Recommendation V.28 was revised by the ITU-T Study Group XVII (1988-1993) and was approved by the WTSC (Helsinki, March 1-12, 1993).

#### **NOTES**

As a consequence of a reform process within the International Telecommunication Union (ITU), the CCITT ceased to exist as of 28 February 1993. In its place, the ITU Telecommunication Standardization Sector (ITU-T) was created as of 1 March 1993. Similarly, in this reform process, the CCIR and the IFRB have been replaced by the Radiocommunication Sector.

In order not to delay publication of this Recommendation, no change has been made in the text to references containing the acronyms "CCITT, CCIR or IFRB" or their associated entities such as Plenary Assembly, Secretariat, etc. Future editions of this Recommendation will contain the proper terminology related to the new ITU structure.

In this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.

© ITU 1993

All rights reserved. No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the ITU.

# **CONTENTS**

|       |                                                     | Page |  |  |  |

|-------|-----------------------------------------------------|------|--|--|--|

| 1     | Scope                                               | 1    |  |  |  |

| 2     | Interchange equivalent circuit                      | 1    |  |  |  |

| 3     | Load                                                |      |  |  |  |

| 4     | Generator                                           |      |  |  |  |

| 5     | Significant levels $(V_1)$                          |      |  |  |  |

| 6     | Signal characteristics                              | 4    |  |  |  |

| 7     | Detection of generator power-off or circuit failure |      |  |  |  |

| Annex | x A – Operation from 20 kbit/s to 64 kbit/s         | 5    |  |  |  |

|       | A.1 Option 1                                        | 5    |  |  |  |

|       | A.2 Option 2                                        | 6    |  |  |  |

# ELECTRICAL CHARACTERISTICS FOR UNBALANCED DOUBLE-CURRENT INTERCHANGE CIRCUITS

(Geneva, 1972; amended at Geneva, 1980, Malaga-Torremolinos, 1984, at Melbourne, 1988 and Helsinki, 1993)

## 1 Scope

The electrical characteristics specified in this Recommendation apply generally to interchange circuits operating with data signalling rates below the limit of 20 kbit/s.

However, for existing equipments, operation up to 64 kbit/s is possible under specific conditions which are described in Annex A.

For new equipment intended for operation at data signalling rates above 20 kbit/s, consideration should be given to the use of electrical characteristics according to Recommendations V.10 and V.11.

# 2 Interchange equivalent circuit

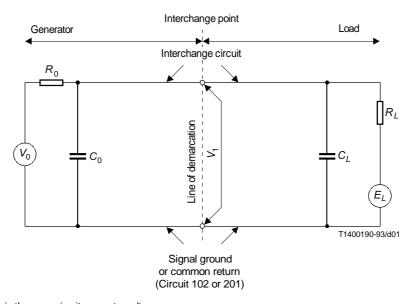

Figure 1 shows the interchange equivalent circuit with the electrical parameters, which are defined below.

This equivalent circuit is independent of whether the generator is located in the data circuit-terminating equipment and the load in the data terminal equipment or vice versa.

- $V_0$  is the open-circuit generator voltage.

- is the total effective d.c. resistance associated with the generator, measured at the interchange point.

- $C_0^{\circ}$  is the total effective capacitance associated with the generator, measured at the interchange point.

- $V_1$  is the voltage at the interchange point with respect to signal ground or common return.

- is the total effective capacitance associated with the load, measured at the interchange point.

- is the total effective d.c. resistance associated with the load, measured at the interchange point.

- E, is the open-circuit load voltage (bias).

FIGURE 1/V.28

Interchange equivalent circuit

The impedance associated with the generator (load) includes any cable impedance on the generator (load) side of the interchange point.

The equipment at both sides of the interface may implement generators as well as receivers in any combination.

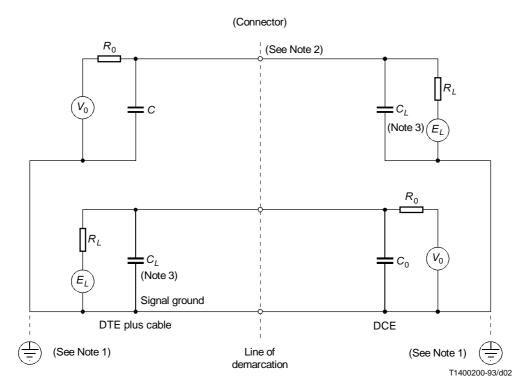

For data transmission applications, it is commonly accepted that the interface cabling is provided by the DTE. This introduces the line of demarcation between the DTE plus cable and the DCE. This line is also called the interchange point and is physically implemented in the form of a connector. The applications also require interchange circuits in both directions. This leads to an illustration as shown in Figure 2.

#### 3 Load

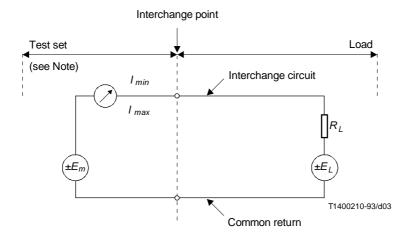

The test conditions for measuring the load impedance are shown in Figure 3.

The impedance on the load side of an interchange circuit shall have a d.c. resistance ( $R_L$ ) neither less than 3000 ohms nor more than 7000 ohms. With an applied voltage ( $E_m$ ), 3 to 15 volts in magnitude, the measured input current (I) shall be within the following limits:

$$I_{\min, \max} = \left| \frac{E_m \pm E_{L \max}}{R_{L \max, \min}} \right|$$

The open-circuit load voltage  $(E_L)$  shall not exceed 2 volts.

The effective shunt capacitance  $(C_I)$  of the load, measured at the interchange point, shall not exceed 2500 picofarads.

To avoid inducing voltage surges on interchange circuits the reactive component of the load impedance shall not be inductive.

NOTE – This is subject to further study.

The load on an interchange circuit shall not prejudice continuous operation with any input signals within the voltage limits specified in clause 4.

## 4 Generator

The generator on an interchange circuit shall withstand an open circuit and a short circuit between itself and any other interchange circuit (including generators and loads) without sustaining damage to itself or its associated equipment.

The open circuit generator voltage  $(V_0)$  on any interchange circuit shall not exceed 15 volts in magnitude. The impedance  $(R_0)$  and  $(R_0)$  on the generator side of an interchange circuit is not specified; however, the combination of  $(R_0)$ 0 and  $(R_0)$ 0 shall be selected so that a short circuit between any two interchange circuits shall not result in any case in a current in excess of one-half ampere.

NOTE-It should be noted that there may be older equipment in the field, where the open-circuit generator voltage is up to 25 volts.

Additionally, when the load open-circuit voltage  $(E_L)$  is zero, the voltage  $(V_1)$  at the interchange point shall not be less than 5 volts and not more than 15 volts in magnitude (either positive or negative polarity), for any load resistance  $(R_L)$  in the range between 3000 ohms and 7000 ohms.

The effective shunt capacitance  $(C_0)$  at the generator side of an interchange circuit is not specified. However, in addition to any load resistance  $(R_L)$  the generator shall be capable of driving all of the capacitance at the generator side  $(C_0)$ , plus a load capacitance  $(C_L)$  of 2500 picofarads.

NOTES

- 1 For test purposes other than specified in this Recommendation (e.g. signal quality measurement), a transmitter test load of 3000 ohms may be used.

- 2 Relay or switch contacts may be used to generate signals on an interchange circuit, with appropriate measures to ensure that signals so generated comply with the applicable clauses of clause 6.

#### **NOTES**

- 1 Signal ground may be further connected to external protective ground if national regulations require.

- 2 For data transmission over telephone-type facilities, ISO has specified a 25-pin connector and pin assignments in accordance with ISO 2110.

- 3 Many existing interchange circuit generators do not provide for meeting the maximum rise time requirement of clause 6 when driving a capacitance of greater than 2500 pF, the maximum permitted load capacitance ( $C_I$ ), which includes the capacitance of the DTE supplied interface cable.

# FIGURE 2/V.28 Practical representation of the inferface

# 5 Significant levels $(V_1)$

For data interchange circuits, the signal shall be considered in the binary 1 condition when the voltage  $(V_1)$  on the interchange circuit measured at the interchange point is more negative than minus 3 volts. The signal shall be considered in the binary 0 condition when the voltage  $(V_1)$  is more positive than plus 3 volts.

For control and timing interchange circuits, the circuit shall be considered ON when the voltage  $(V_1)$  on the interchange circuit is more positive than plus 3 volts, and shall be considered OFF when the voltage  $(V_1)$  is more negative than minus 3 volts (see Table 1).

NOTE – In certain countries, in the case of direct connection to d.c. telegraph-type circuits only, the voltage polarities in Table 1 may be reversed.

The region between plus 3 volts and minus 3 volts is defined as the transition region. For an exception to this, see clause 7.

NOTE – The internal resistance of the ammeter shall be much less than the load resistance  $(R_L)$ .

# FIGURE 3/V.28 **Equivalent test circuit**

TABLE 1/V.28 Correlation table

| $V_1 > +3 \text{ volts}$ |  |  |

|--------------------------|--|--|

| 0                        |  |  |

| ON                       |  |  |

|                          |  |  |

## 6 Signal characteristics

The following limitations to the characteristics of signals transmitted across the interchange point, exclusive of external interference, shall be met at the interchange point when the interchange circuit is loaded with any receiving circuit which meets the characteristics specified in clause 3.

These limitations apply to all (data, control and timing) interchange signals unless otherwise specified.

- 1) All interchange signals entering into the transition region shall proceed through this region to the opposite signal state and shall not re-enter this region until the next significant change of signal condition, except as indicated in 6) below.

- 2) There shall be no reversal of the direction of voltage change while the signal is in the transition region, except as indicated in 6) below.

- 3) For control interchange circuits, the time required for the signal to pass through the transition region during a change in state shall not exceed one millisecond.

- 4) For data and timing interchange circuits, the time required for the signal to pass through the transition region during a change in state shall not exceed 1 millisecond or 3% of the nominal element period on the interchange circuit, whichever is the less.

- 5) To reduce crosstalk between interchange circuits the maximum instantaneous rate of voltage change will be limited. A provisional limit will be 30 volts per microsecond.

- 6) When electromechanical devices are used on interchange circuits, points 1) and 2) above do not apply to data interchange circuits.

## 7 Detection of generator power-off or circuit failure

Certain applications require detection of various fault conditions in the interchange circuits, e.g.:

- 1) generator power-off condition;

- 2) receiver not interconnected with a generator;

- 3) open-circuited interconnecting cable;

- 4) short-circuited interconnecting cable.

The power-off impedance of the generator side of these circuits shall not be less than 300 ohms when measured with an applied voltage (either positive or negative polarity) not greater than 2 volts in magnitude referenced to signal ground or common return.

The interpretation of a fault condition by a receiver (or load) is application dependent. Each application may use a combination of the following classification:

- *Type 0:* No interpretation. A receiver or load does not have detection capability.

- Type 1: Data circuits assume a binary 1 state. Control and timing circuits assume an OFF condition.

The association of the circuit failure detection to particular interchange circuits in accordance with the above types is a matter of the functional and procedural characteristics specification of the interface.

The interchange circuits monitoring circuit fault conditions in the general telephone network interfaces are indicated in Recommendation V.24.

#### Annex A

#### Operation from 20 kbit/s to 64 kbit/s

(This annex forms an integral part of this Recommendation)

Note – It should be noted that actual hardware for V.28 generators and receivers is not designed with a view to operating at signalling rates beyond 20 kbit/s, and may not meet all requirements contained in this Recommendation when operated at such signalling rates. Furthermore, the performance of such hardware may not meet the requirements of International Standards on signal quality (viz: ISO 7480 and ISO 9543). The only application presently recognized by the CCITT, where there may be a need to apply V.28 electrical characteristics at signalling rates higher than 20 kbit/s is with existing DTEs which are connected to DCEs comprising a data compression capability according to Recommendation V.42 bis.

#### A.1 Option 1

Limit the load capacitance  $(C_1)$  on each circuit to the value:

$$C_1 max. (pF) \le \left[ \left( 2500 + C_0 \right) 20 / BR \right] - C_0$$

BR being the maximum bit rate (in kbit/s) considered for the interface and  $C_0$  the capacitance associated with the generator side of the interface.

Such a limitation of the load capacitance allows to maintain compliance with the 3% of a Unit Interval (UI) maximum transition region crossing time requirement of 6.4.

### A.2 Option 2

Replace, beyond 20 kbit/s, the 3% requirement of 6.4 by a constant value of 1.5 μs.

This allows keeping the 2500 pF maximum  $C_1$  load capacitance specified in clause 4 at the cost of a transition region crossing relative time increasing from 3% of a UI at 20 kbit/s up to 9.6% of a UI at 64 kbit/s.

NOTE – Option 1 may be inapplicable if  $C_0$  is not small relative to 2500 pF (e.g. in the case of a DTE with a long interconnecting cable). Option 2 reduces the operating margins at the interface by adding up to 2% of jitter at 64 kbit/s on the data signals and, for synchronous interfaces, by increasing the timing displacement between circuits with contradirectional timing relationship (typically up to 15% at 64 kbit/s, which may correspond to a sampling error of 30% if there is no phase shift compensation in the data receiver).

The added jitter may prevent a DTE operating in start-stop mode at (or near) the 64 kbit/s limit from complying with a category II level of signal quality, as defined by ISO in standard ISO 7480 (Start-stop Transmission Signal Quality at DTE/DCE Interfaces). The added timing displacement may prevent a DTE operating in synchronous mode at (or near) the 64 kbit/s limit from complying with the requirements of the standard ISO 9543 (Synchronous Transmission Signal Quality at DTE/DCE Interfaces) for contradirectional timing.